背景

《ug471》介绍了Xilinx 7 系列 SelectIO 的输入/输出特性及逻辑资源的相关内容。

第 1 章《SelectIO Resources》介绍了输出驱动器和输入接收器的电气特性,并通过大量实例解析了各类标准接口的实现。

第 2 章《SelectIO Logic Resources》介绍了输入输出数据寄存器及其双倍数据速率(DDR)操作,以及可编程输入延(IDELAY)和可编程输出延迟(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介绍了ISERDESE2 、OSERDESE2与IO_FIFO。

了解了这个手册充分介绍的SelectIO架构和资源,以及所支持的电平标准。就可以利用相应的架构和资源实现与不同电平标准、通信速率间的外设建立起联系。

系列目录与传送门

- 基于Xilinx的7系列,

- 笔者学习、研究FPGA的过程、笔记,记录为:《凡人修FPGA传》。

说明1:本系列基于文档文档《ug471_7Series_SelectIO.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,非常支持并推荐大家去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:本博客是笔者用来记录学习过程的一个形式,并非专业论文。因此,在本博客中不会太注重图文格式的规范。

说明5:如果文章有误,欢迎诸位道友指出、讨论,笔者也会积极改正,希望大家一起进步!

文章目录

- 背景

- 系列目录与传送门

- 前言

- 1、Introduction

- [2、ILOGIC Resources](#2、ILOGIC Resources)

-

- [2.1、Combinatorial Input Path](#2.1、Combinatorial Input Path)

- [2.2、Input DDR Overview (IDDR)](#2.2、Input DDR Overview (IDDR))

-

- [2.2.1、OPPOSITE_EDGE 模式](#2.2.1、OPPOSITE_EDGE 模式)

- [2.2.2、SAME_EDGE 模式](#2.2.2、SAME_EDGE 模式)

- [2.2.3、SAME_EDGE_PIPELINED 模式](#2.2.3、SAME_EDGE_PIPELINED 模式)

- [2.3、Input DDR Resources (IDDR)](#2.3、Input DDR Resources (IDDR))

- [3、Input Delay Resources (IDELAY)](#3、Input Delay Resources (IDELAY))

-

- [3.1、IDELAY Modes](#3.1、IDELAY Modes)

- [3.2、IDELAY Timing](#3.2、IDELAY Timing)

- 3.3、补充:波形图

- 4、IDELAYCTRL

-

- [4.1、IDELAYCTRL Overview](#4.1、IDELAYCTRL Overview)

- [4.2、IDELAYCTRL Timing](#4.2、IDELAYCTRL Timing)

- [4.3、IDELAYCTRL Locations](#4.3、IDELAYCTRL Locations)

- [5、OLOGIC Resources](#5、OLOGIC Resources)

-

- [5.1、Output DDR Overview (ODDR)](#5.1、Output DDR Overview (ODDR))

-

- [5.1.1、OPPOSITE_EDGE 模式](#5.1.1、OPPOSITE_EDGE 模式)

- [5.1.2、SAME_EDGE 模式](#5.1.2、SAME_EDGE 模式)

- [5.2、Clock Forwarding](#5.2、Clock Forwarding)

- [5.3、Output DDR Primitive (ODDR)](#5.3、Output DDR Primitive (ODDR))

- [6、Output Delay Resources (ODELAY)---Not Available in HR Banks](#6、Output Delay Resources (ODELAY)—Not Available in HR Banks)

-

- [6.1、ODELAY Modes](#6.1、ODELAY Modes)

- [6.2、ODELAY Timing](#6.2、ODELAY Timing)

- 6.3、补充:波形图

- 7、参考文献

前言

本文对应的是《ug471_7Series_SelectIO.pdf》的第 2 章 < SelectIO Logic Resources > 部分,是对7系列FPGA的所带有的I/O逻辑资源的一个概述与介绍。

1、Introduction

7系列FPGA的基本I/O逻辑资源,包括以下内容:

• Combinatorial input/output

• 3-state output control

• Registered input/output

• Registered 3-state output control

• Double-Data-Rate (DDR) input/output

• DDR output 3-state control

• IDELAY provides users control of an adjustable, fine-resolution delay taps

• ODELAY provides users control of an adjustable, fine-resolution delay taps

• SAME_EDGE output DDR mode

• SAME_EDGE and SAME_EDGE_PIPELINED input DDR mode

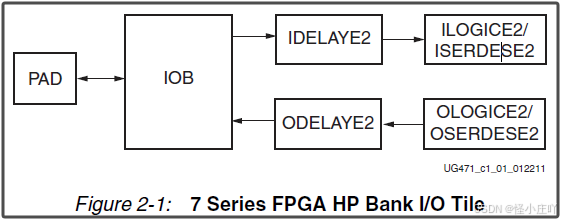

图2-1,展示了1.8V HP Bank 的一个 I/O Tile。

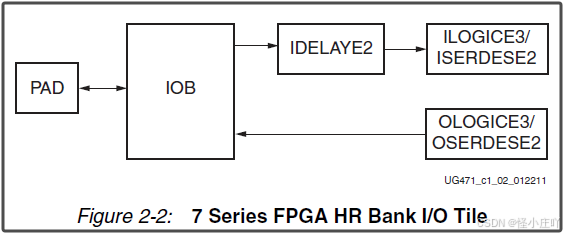

图2-2,展示了3.3V HR Bank 的一个 I/O Tile。

SelectIO™输入、输出和三态驱动器,都位于输入/输出缓冲器(input/output buffer,IOB)中。

HP Bank 有独立的IDELAY和ODELAY模块。HR Bank 的逻辑元素与 HP Bank 相同,只是缺少ODELAY模块。

2、ILOGIC Resources

ILOGIC 模块与 输入/输出模块(I/O blockIOB)相邻,包含用于捕获通过 IOB 进入 FPGA 的数据的同步元件(synchronous elements)。

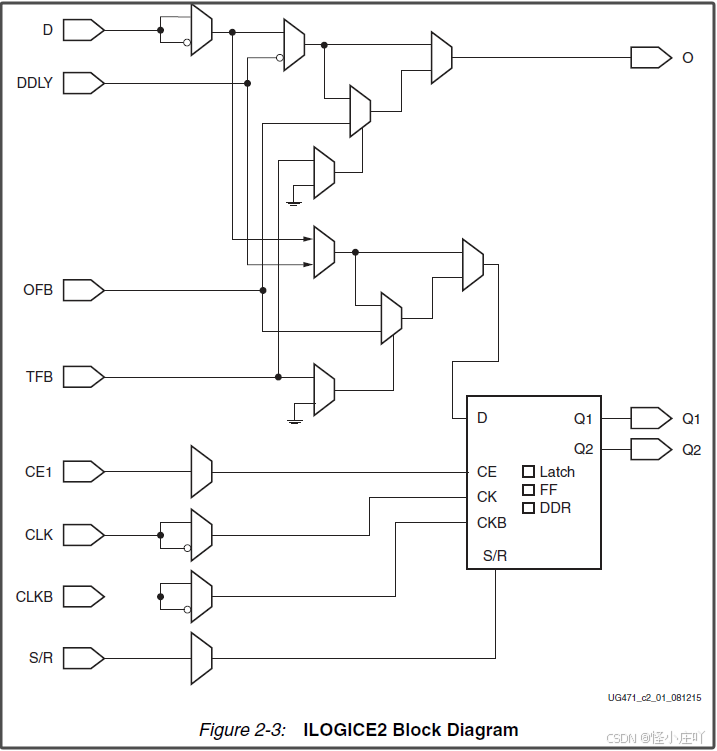

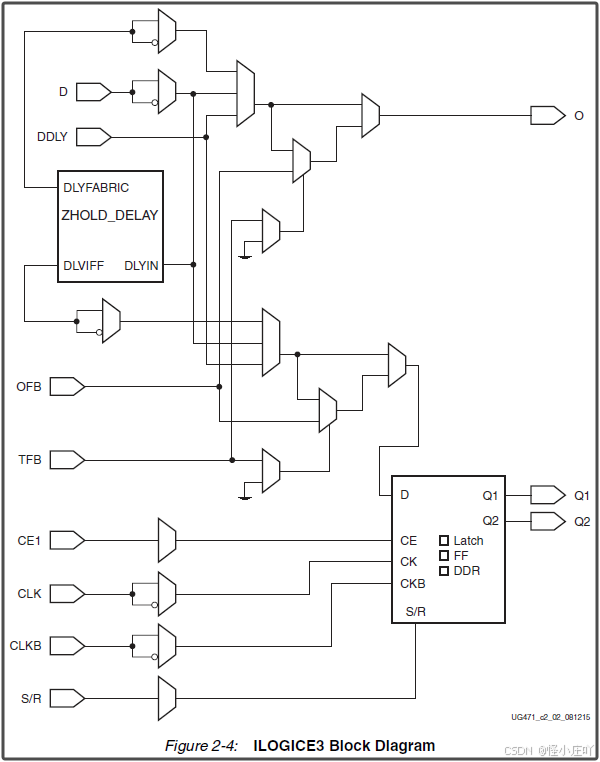

7 系列器件中的 ILOGIC 配置类型包括 ILOGICE2(HP I/O bank)和 ILOGICE3(HR I/O bank)。二者功能及端口完全一致,区别仅在于:

• ILOGICE3位于 HR bank,包含零保持延迟元件(zero hold delay element,ZHOLD)。

• ILOGICE2位于 HP bank,不含 ZHOLD 元件。

• 这些差异如图 2-3 和图 2-4 所示。

输入/输出互连(input/output interconnect,IOI)存储元件 D输入端 上的 ZHOLD 延迟,会自动匹配内部时钟分配延迟,可消除焊盘之间的保持时间要求,使之为零。ILOGIC 模块支持在输入端配置可选的静态未补偿(an optional static uncompensated)零保持(zero hold,ZHOLD)延迟线(delay line),用于补偿时钟插入延迟(clock insertion delays)。当时钟路径直接来自同一 Bank 或相邻 Bank 的 BUFG/BUFGCE 时,ZHOLD功能可经过优化用于补偿时钟插入延迟。除非时钟源为 MMCM 或 PLL,亦或在 Xilinx设计约束(XDC)中设置了 IOBDELAY 属性,ZHOLD 默认启用。重要提示:ZHOLD 并非适用于所有应用场景,需查阅时序报告以确认其对特定时钟方案的影响。

ILOGICE2 和 ILOGICE3 并非可实例化的原语。在布局布线后,如输入触发器(input flip-flop,IFD)或 IDDR(input DDR)等用户实例化的元件,则会被包含在ILOGICE2 或 ILOGICE3中。

ILOGIC 可支持以下操作:

• 边沿触发的 D 型触发器

• IDDR 模式(OPPOSITE_EDGE 或 SAME_EDGE 或 SAME_EDGE_PIPELINED)

• 电平敏感锁存器

• 异步 / 组合逻辑

ILOGIC 模块的寄存器具有一个公共的时钟使能信号(CE1),默认情况下为高电平有效。如果未连接该信号,任何存储元件的时钟使能引脚将默认为有效状态。ILOGIC 模块的寄存器有一个通用的同步或异步 置位和复位信号(SR 信号)。置位/复位 输入引脚 SR 会将存储元件强制设置为 SRVAL 属性所指定的状态。复位条件优先于置位条件。在 ILOGIC 模块中,可以为每个存储元件单独设置 SRVAL 属性,但对于同步或异步置位 / 复位(SRTYPE)的选择,却不能为 ILOGIC 模块中的每个存储元件单独进行设置。

博客在 《xilinx原语介绍及仿真之IDDR》中有进行ILOGICE的寄存器(IFD)使用的说明,并在有如下结论:

2.1、Combinatorial Input Path

组合输入路径,Combinatorial Input Path,组合输入路径用于在输入驱动器和 FPGA 逻辑之间建立直接连接。

在以下情况下,软件会自动使用该路径:

• 从输入数据到 FPGA 逻辑中的逻辑资源存在直接(未寄存)的连接。

• 将软件映射指令 " pack I/O register/latches into IOBs " 设置为 "OFF" 状态。

2.2、Input DDR Overview (IDDR)

7系列器件在 ILOGIC 模块中配备了专用寄存器,用于实现输入双倍数据速率(DDR)寄存器功能。通过实例化 IDDR 原语来使用这一功能。

当不使用IDDR功能时,在使用IDDR原语后,只需要添加(IOB == "TRUE")原语,就可以使用ILOGICE中的触发器(FF)的功能。 这个触发器相比FPGA内部触发器更靠近FPGA管脚,使得建立时间余量更大,更有利于时序。(《xilinx原语介绍及仿真之IDDR》)

所有输入到 I/O tile 的时钟均采用全多路复用方式(fully multiplexed),即 ILOGIC 模块和 OLOGIC 模块之间不共享时钟。IDDR 原语支持以下工作模式:

• OPPOSITE_EDGE 模式

• SAME_EDGE 模式

• SAME_EDGE_PIPELINED 模式

SAME_EDGE模式 和 SAME_EDGE_PIPELINED模式 允许设计人员在 ILOGIC 模块内将下降沿数据转移到上升沿域,从而节省可配置逻辑块(CLB)和时钟资源,并提高性能。上述这些模式,通过 DDR_CLK_EDGE 属性来实现。

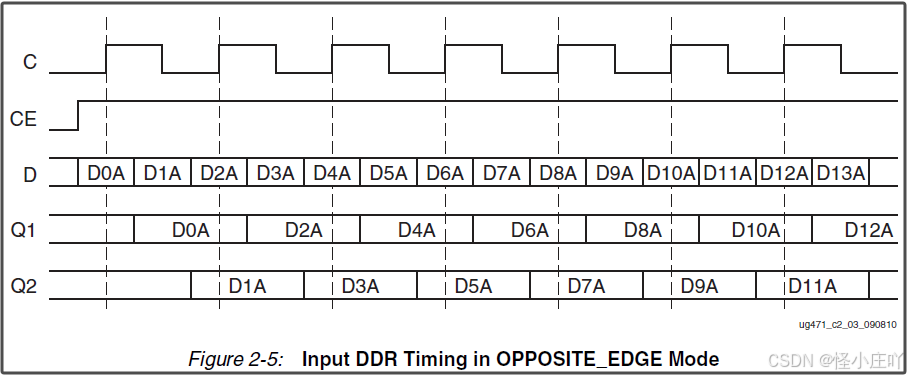

2.2.1、OPPOSITE_EDGE 模式

传统DDR 的 OPPOSITE_EDGE模式,是通过 ILOGIC 模块中的单个输入来实现的。上升沿、下降沿均采样:在时钟的上升沿,数据通过输出 Q1 传输至 FPGA 逻辑;在时钟的下降沿,数据则通过输出 Q2 传输至 FPGA 逻辑。且,输出相较于输入要延一拍。

图 2-5 展示了 IDDR 在 OPPOSITE_EDG模式 下的时序图。

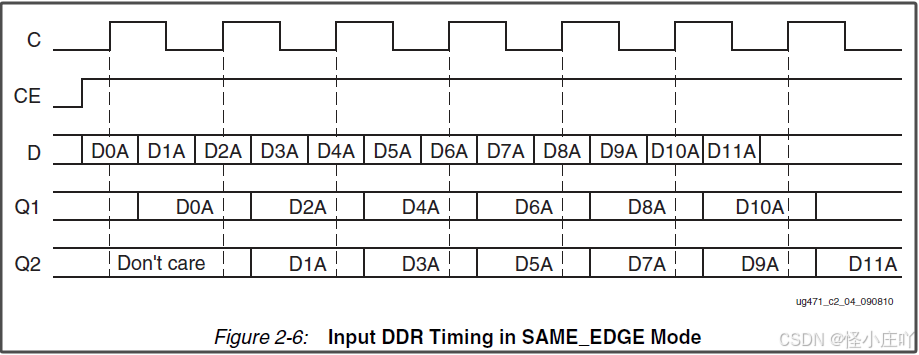

2.2.2、SAME_EDGE 模式

在 SAME_EDGE 沿模式下,数据会在同一个时钟边沿被送入FPGA逻辑。

输出结果,与OPPOSITE_EDGE 模式相比,差别在于数据对齐了,但错开了一位。

图2-6,展示 SAME_EDGE模式 下的IDDR时序图。在时序图中,输出对Q1和Q2不再是(0)和(1)。而是,第一对出现的是Q1(0)和Q2(don't care),接着在下一个时钟周期出现的是(1)和(2)。

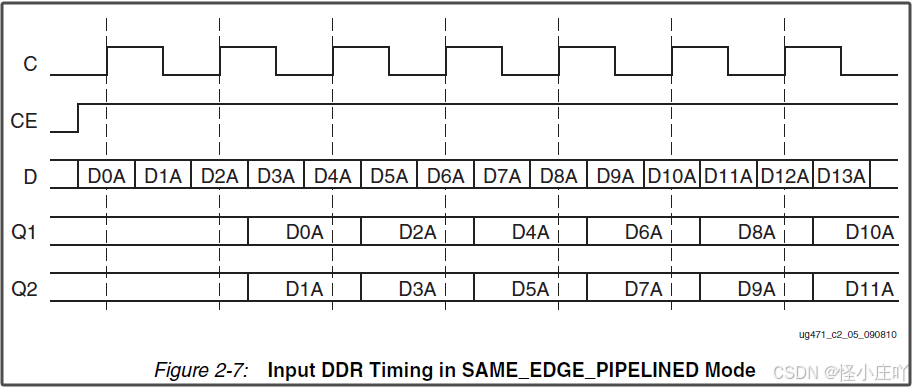

2.2.3、SAME_EDGE_PIPELINED 模式

在 SAME_EDGE_PIPELINED 模式下,数据在同一个时钟边沿被传输到 FPGA 逻辑中。

与 SAME_EDGE 模式不同的是,数据对不再被一个时钟周期分隔开。然而,为了消除 SAME_EDGE 模式中的时钟周期分隔效应(separated effect),需要额外的时钟延迟。

图 2-7, 展示了 IDDR 在 SAME_EDGE_PIPELINED 模式下的时序图。输出对 Q1 和 Q2 会同时被传输到 FPGA 逻辑中。

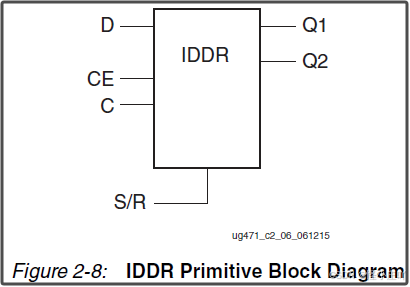

2.3、Input DDR Resources (IDDR)

- IDDR primitive

图2-8,展示了 IDDR 原语。其中,Set 和 Reset 不能同时断言。

3、Input Delay Resources (IDELAY)

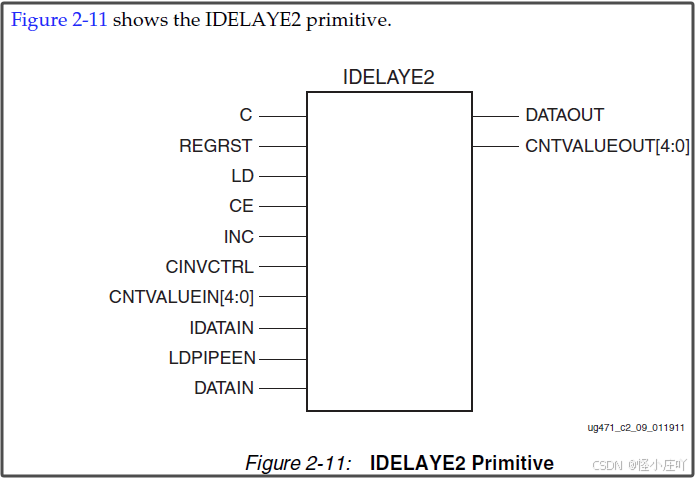

Every I/O block contains a programmable delay primitive called IDELAYE2. The IDELAY can be connected to an ILOGICE2/ISERDESE2 or ILOGICE3/ISERDESE2 block.

IDELAYE2 is a 31-tap, wraparound, delay primitive with a calibrated tap resolution. Refer to the 7 series FPGA data sheets for delay values. It can be applied to the combinatorial input path, registered input path, or both. It can also be accessed directly from the FPGA logic. IDELAY allows incoming signals to be delayed on an individual input pin basis. The tap delay resolution is contiguously calibrated by the use of an IDELAYCTRL reference clock from the range specified in the 7 series FPGA data sheets.

- IDELAYE2 primitive

3.1、IDELAY Modes

当用作输入延迟(IDELAY)时,数据输入可来自输入缓冲器(IBUF)或 FPGA 逻辑,输出则连接至 ILOGICE2/ISERDESE2 或 ILOGICE3/ISERDESE2 模块。它有以下几种工作模式可供选择:

- Fixed delay mode( IDELAY_TYPE=FIXED )

在 fixed delay mode 下,延迟值在配置时根据 IDELAY_VALUE 属性确定的抽头编号(tap number)进行预设。一旦完成配置,该值便无法更改。使用此模式时,必须实例化 IDELAYCTRL 原语。

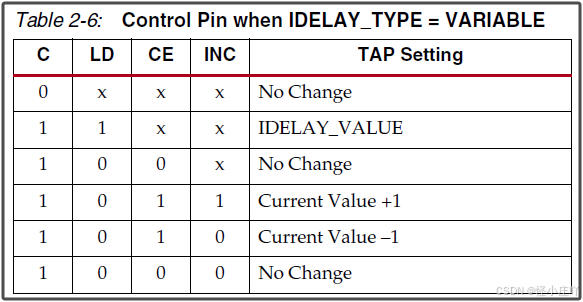

- Variable delay mode( IDELAY_TYPE=VARIABLE )

在 variable delay mode下,延迟值可以在配置完成后可通过操控控制信号 CE 和 INC 来改变。使用此模式时,同样必须实例化 IDELAYCTRL 原语。

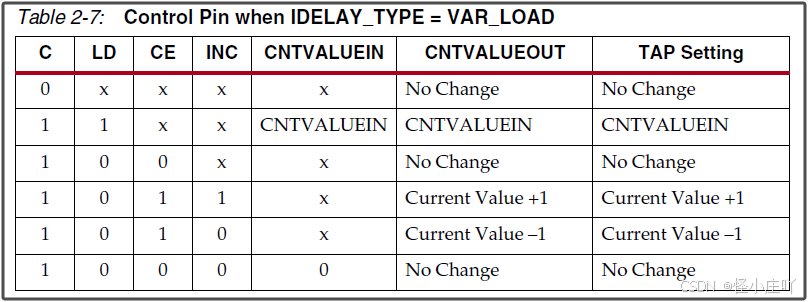

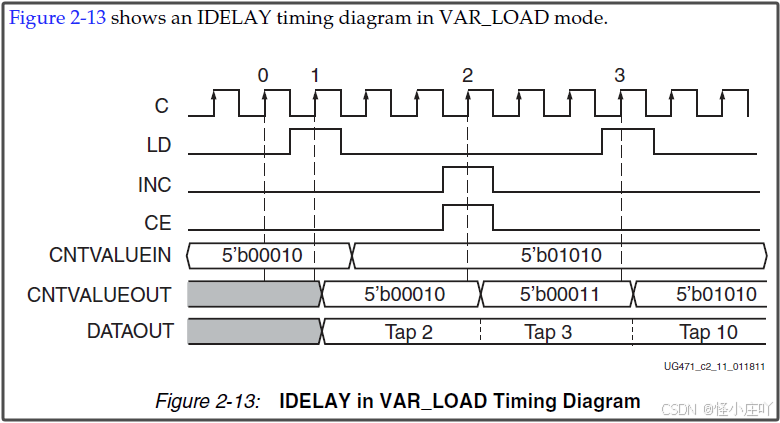

- Loadable variable mode( IDELAY_TYPE=VAR_LOAD )

在此模式下,除了具备与 Variable delay mode( IDELAY_TYPE=VARIABLE ) 相同的功能外,还可通过来自 FPGA 逻辑的 5 位输入 CNTVALUEIN[4:0] 加载 IDELAY 的 tap 。当 LD 引脚出现脉冲时,CNTVALUEIN[4:0] 上的值将成为新的 tap value 。使用此模式时,必须实例化 IDELAYCTRL 原语。

VAR_LOAD模式与VARIABLE模式相似,区别在于 VARIABLE模式为高电平时,是加载IDELAY_VALUE的值到内部作为延时数据,而VAR_LOAD模式在LD为高电平时,加载输入信号CNTVALUEIN的值作为内部新的延时数据。(《xilinx原语介绍及仿真之IDELAYE2 & IDELAYCTRL》)

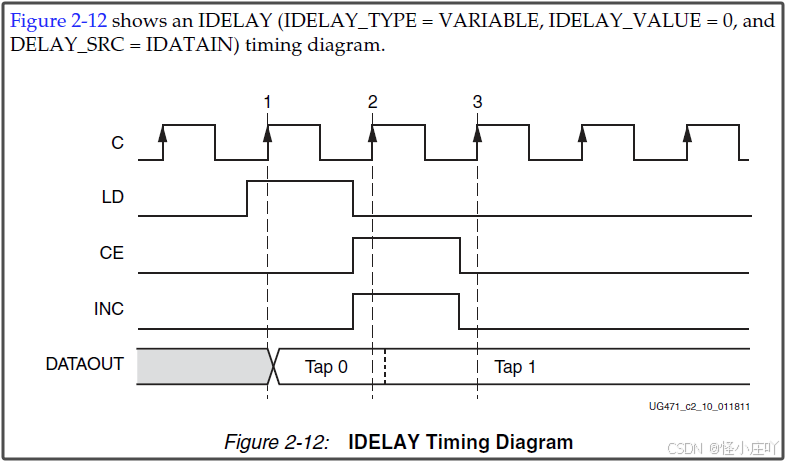

3.2、IDELAY Timing

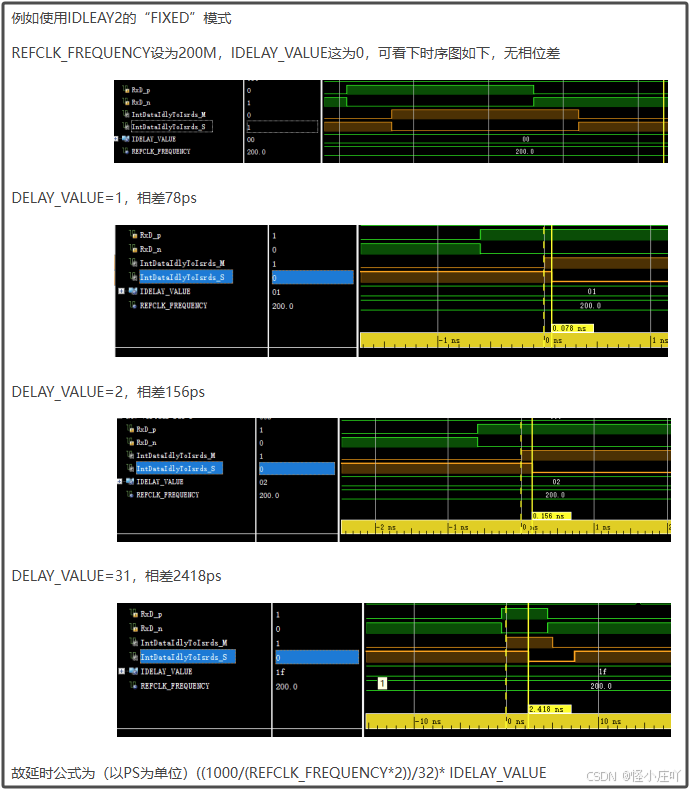

3.3、补充:波形图

在《7系列selectio之DELAYE相关》中,看到这样一个波形,就直接截图给诸位道友展示了。请原谅笔者有些懒,没有自己跑仿真。

4、IDELAYCTRL

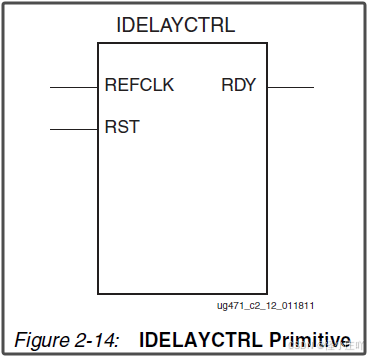

4.1、IDELAYCTRL Overview

如果实例化了 IDELAYE2 或 ODELAYE2 原语,那么也必须实例化 IDELAYCTRL 模块。 IDELAYCTRL 模块会持续校准其所在区域内的各个 delay taps(IDELAY/ODELAY),以降低工艺、电压和温度变化带来的影响。IDELAYCTRL 模块会使用用户提供的参考时钟(REFCLK)来校准 IDELAY 和 ODELAY。

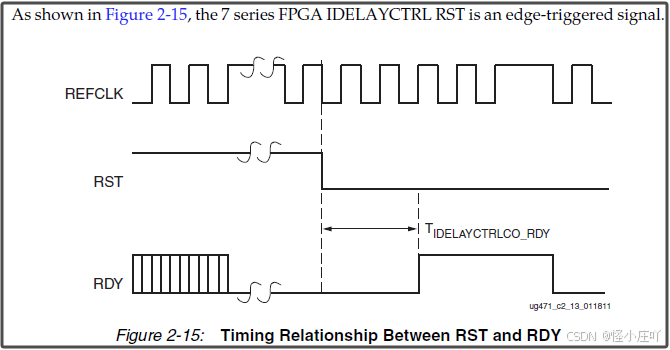

- RST - Reset

RST 为高电平有效异步复位信号。复位释放后延时一段时间将RDY信号拉高表示复位完成。

To ensure proper IDELAY and ODELAY operation, IDELAYCTRL must be reset after configuration and the REFCLK signal is stable. A reset pulse width TIDELAYCTRL_RPW is required.

- REFCLK - Reference Clock

REFCLK 为 IDELAYCTRL 提供时间基准,用于校准同一区域内所有 IDELAY 和 ODELAY 模块。

该时钟必须由 BUFG 或 BUFH 驱动,且设定值也不是可以随意给的,要求是 190-210、 290-310、390-410 这三个范围之间。

REFCLK must be FIDELAYCTRL_REF ± the specified ppm tolerance (IDELAYCTRL_REF_PRECISION) to guarantee a specified IDELAY and ODELAY resolution ( TIDELAYRESOLUTION ). REFCLK can be supplied directly from a user-supplied source or the MMCM and must be routed on a global clock buffer.

- RDY - Ready

RDY 表示 IDELAY 和 ODELAY 模块已完成校准。若 REFCLK 保持高电平或低电平超过一个时钟周期,RDY 信号将置为无效(低电平)。若 RDY 无效(低电平),则必须重新复位 IDELAYCTRL 模块。

The implementation tools allow RDY to be unconnected/ignored.

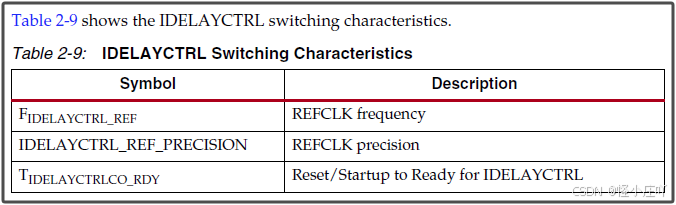

4.2、IDELAYCTRL Timing

4.3、IDELAYCTRL Locations

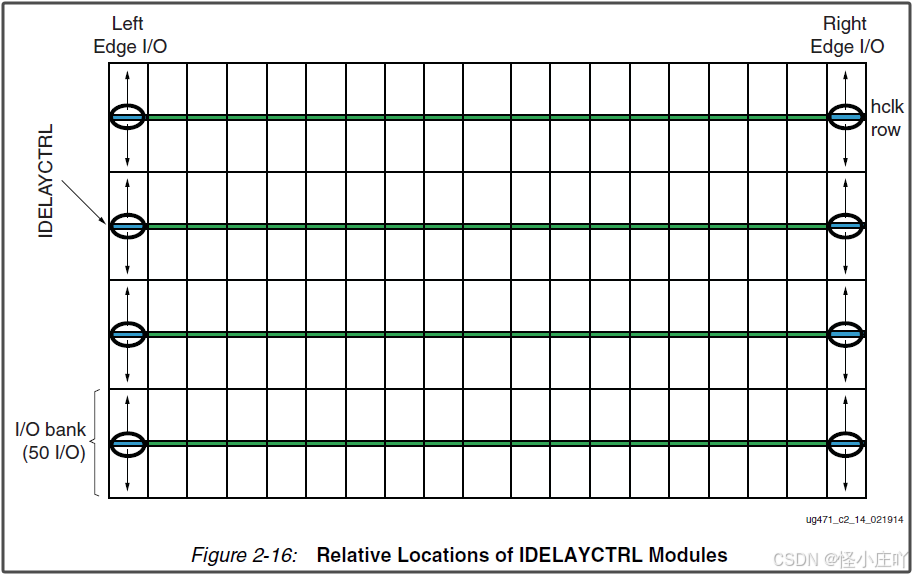

在每个时钟区域的每一 I/O 列中都存在 IDELAYCTRL 模块。一个 IDELAYCTRL 模块会对其所在时钟区域内的所有 IDELAYE2 和 ODELAYE2 模块进行校准。

图2-16,展示了IDELAYCTRL模块在FPGA架构中的相对位置。

5、OLOGIC Resources

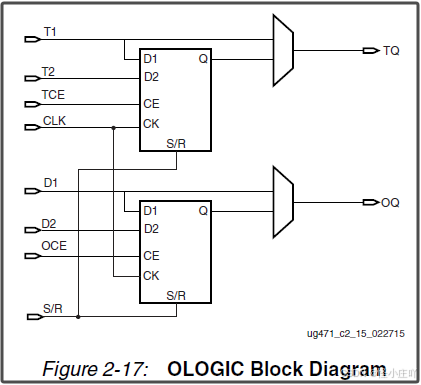

OLOGIC 模块靠近 I/O block( IOB )。OLOGIC 是一个专用的同步模块,用于通过 IOB 将数据从 FPGA 中输出。

OLOGIC 资源的类型包括 OLOGICE2(HP I/O banks)和 OLOGICE3(HR I/O banks)。

OLOGICE2 和 OLOGICE3 并非原语,不能被实例化。在布局布线之后,它们包含用户实例化的元件,比如 output flip-flop(OFD)或 output DDR element(ODDR)。

OLOGIC 由两个主要模块组成,一个用于配置输出数据路径,另一个用于配置三态控制路径。这两个模块有一个公共时钟(CLK),但使能信号不同,分别是 OCE 和 TCE。两者都具有由独立的 SRVAL 属性控制的异步和同步置位与复位(S/R 信号)功能。

输出路径和三态路径可以被独立配置为以下模式之一:

• 边沿触发的 D 型触发器

• DDR模式(SAME_EDGE 或 OPPOSITE_EDGE)

• 电平敏感锁存器

• 异步 / 组合逻辑

图 2-17,展示了 OLOGIC 模块中的各种逻辑资源。

- Combinatorial Output Data and 3-State Control Path

组合输出路径在 FPGA 逻辑与输出驱动器或输出驱动器控制之间建立直接连接。在以下情况下,软件会自动使用这些路径:

• 从 FPGA 逻辑中的逻辑资源到输出数据或三态控制存在直接(未寄存)的连接。

• " pack I/O register/latches into IOBs " 这一软件映射指令设置为 "关闭(OFF)" 状

5.1、Output DDR Overview (ODDR)

ODDR位于OLOGIC中,把FPGA内部逻辑中的单沿传输信号转换为双沿传输信号,输出给ODELAYE或者PAD。(《xilinx原语详解及仿真之ODDR》)

7 系列器件在 OLOGIC(输出逻辑)模块中设有专用寄存器,用于实现 ODDR 寄存器功能。通过实例化 ODDR 原语即可使用该功能。使用 OLOGIC 时,DDR 多路复用会自动进行,无需手动控制多路选择,该控制信号由时钟生成。

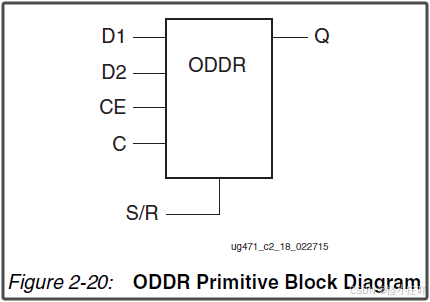

ODDR 原语只有一个时钟输入,下降沿数据由输入时钟的本地反相时钟驱动。所有输入到 I/O tile 的时钟均采用全多路复用方式(fully multiplexed),即 ILOGIC 模块和 OLOGIC 模块之间不存在时钟共享。ODDR 原语支持以下工作模式:

• OPPOSITE_EDGE 模式

• SAME_EDGE 模式

SAME_EDGE模式 允许设计人员在 ODDR时钟 的上升沿将两个数据输入都提供给 ODDR 原语,从而节省了可配置逻辑块(CLB)和时钟资源,并提升了性能。此模式通过 DDR_CLK_EDGE 属性实现,同时也支持三态控制。

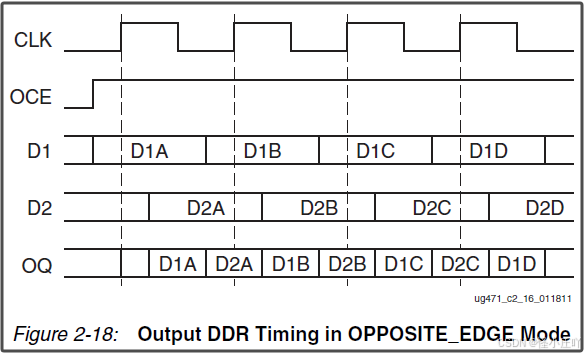

5.1.1、OPPOSITE_EDGE 模式

在 OPPOSITE_EDGE模式下,时钟(CLK)的上升沿和下降沿都被用于以两倍的数据传输速率捕获来自 FPGA 逻辑的数据。输出端的数据都会被传输到 IOB 的数据输入端或三态控制输入端。

如图 2-18 ,展示了在OPPOSITE_EDGE模式下的 output DDR 时序图。

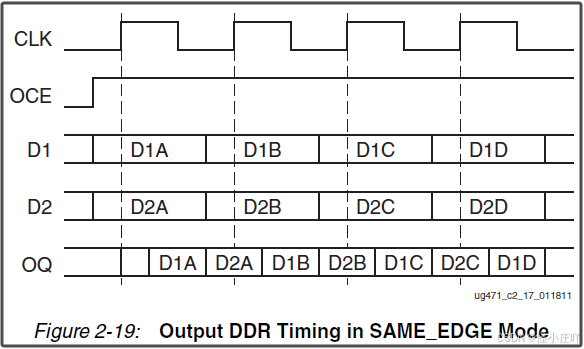

5.1.2、SAME_EDGE 模式

在 SAME_EDGE模式 下,数据可以在同一个时钟边沿被传输至 IOB 。在同一个时钟边沿将数据传输至 IOB,可避免出现建立时间违规的情况,并且与使用 CLB 寄存器相比,用户能够以最小的寄存器到寄存器延迟实现更高的 DDR 频率。

图 2-19 ,展示了SAME_EDGE 模式下的输出 DDR 时序图。

5.2、Clock Forwarding

Output DDR 可以将时钟的一个副本转发到输出端。这对于以相同延迟传播时钟信号和 DDR 数据,以及在每个时钟负载都有独立时钟驱动器的多时钟生成场景中非常有用。实现方法是将 ODDR 原语的 D1 输入端置为高电平,D2 输入端置为低电平。Xilinx 建议采用这种方案将时钟从 FPGA 逻辑转发至输出引脚。

5.3、Output DDR Primitive (ODDR)

6、Output Delay Resources (ODELAY)---Not Available in HR Banks

每个 HP I/O block 包含一个名为 ODELAYE2 的可编程绝对延迟原语。该 ODELAY 可连接至 OLOGICE2/OSERDESE2 模块。

ODELAY is a 31-tap,wraparound, delay primitive with a calibrated tap resolution.

它可应用于组合输出路径或寄存输出路径,也可直接从 FPGA 逻辑进行访问。ODELAY 允许对输出信号按单个信号进行延迟处理。通过从 7 系列 FPGA 数据手册规定的范围内选择 IDELAYCTRL 参考时钟,可调整 tap delay resolution 。

6.1、ODELAY Modes

当用作 ODELAY 时,数据输入来自 IBUF 或 FPGA 逻辑,输出则连接 ILOGICE2/ISERDESE2 或 ILOGICE3/ISERDESE2。ODELAY 提供以下几种操作模式:

- Fixed delay mode( ODELAY_TYPE = FIXED )

在 fixed delay mode 下,延迟值在配置时根据 ODELAY_VALUE 属性确定的 tap number进行预设。一旦完成配置,该值便无法更改。使用此模式时,必须实例化 IDELAYCTRL 原语。

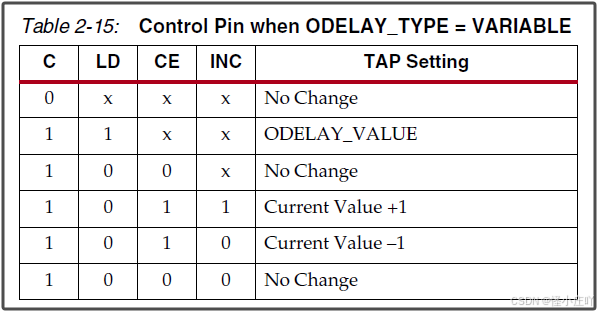

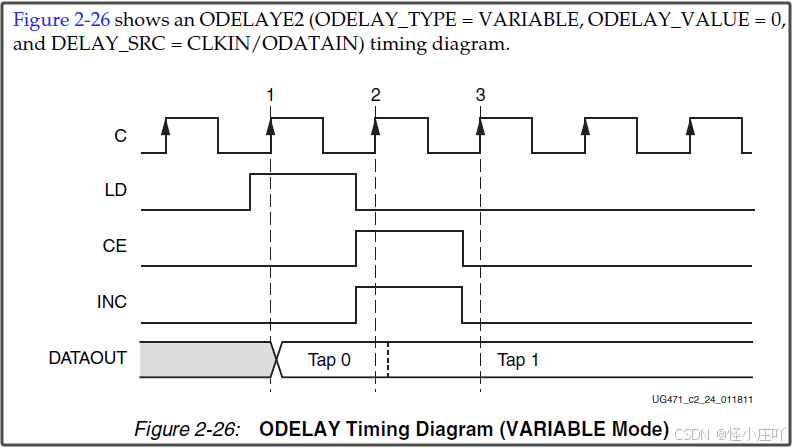

- Variable delay mode( ODELAY_TYPE = VARIABLE )

在 variable delay mode 下,配置完成后,可通过操控控制信号 CE 和 INC 来改变延迟值。使用此模式时,必须实例化 IDELAYCTRL 原语。

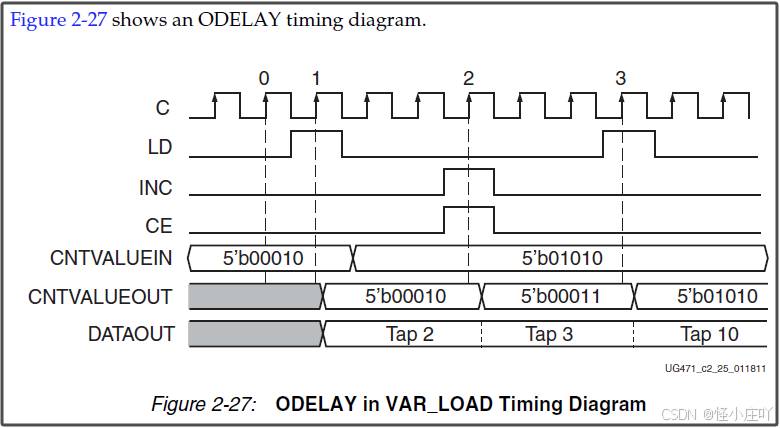

- Loadable variable delay mode (ODELAY_TYPE = VAR_LOAD)

在此模式下,除具备与 ODELAY_TYPE = VARIABLE 相同的功能外,还可通过来自 FPGA 逻辑的 5 位输入 CNTVALUEIN[4:0] 加载 ODELAY 的 tap。当 LD 引脚出现脉冲时,CNTVALUEIN<4:0 > 上的值将成为新的 tap value。由于具备这一功能,ODELAY_VALUE 属性将被忽略。使用此模式时,必须实例化 IDELAYCTRL 原语。

6.2、ODELAY Timing

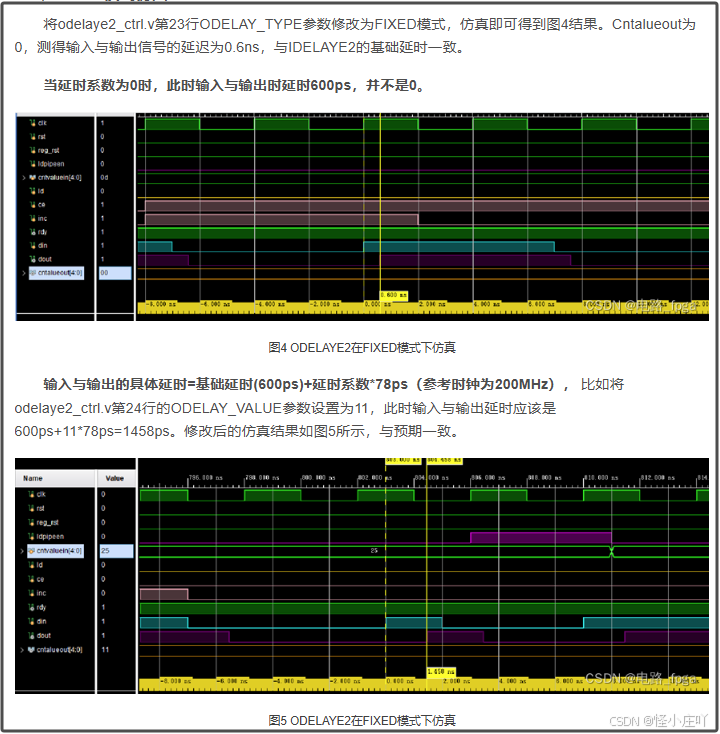

6.3、补充:波形图

但是在《xilinx原语介绍及仿真之ODELAYE2》中,看到了仿真波形,如下图所示。请原谅笔者有些懒,没有自己跑仿真。

7、参考文献

1、《ug471_7Series_SelectIO.pdf》

3、《xilinx原语介绍及仿真之IDDR》,这篇也还不错。

4、《xilinx原语介绍及仿真之IDELAYE2 & IDELAYCTRL》

6、《xilinx原语介绍及仿真之ODELAYE2》,这篇博客里面的仿真做的比较全,诸位道友感兴趣的话,可以去看一看。