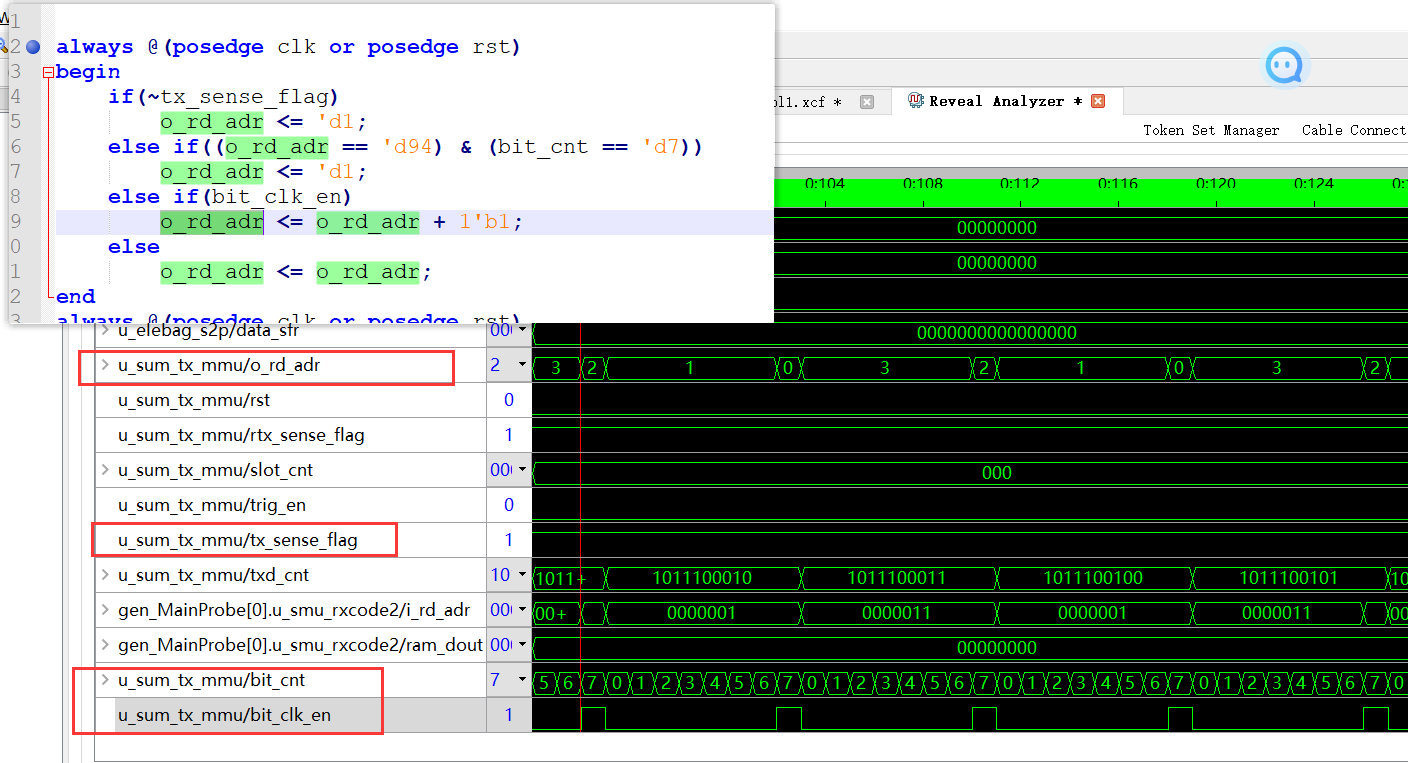

在Vivado中在always块中写逻辑时如果出现always块中的异步复位敏感词在块内部未使用的情况,如下例的rst:

always @(posedge clk or posedge rst)

begin

if(~tx_sense_flag)

o_rd_adr <= 'd1;

else if((o_rd_adr == 'd94) & (bit_cnt == 'd7))

o_rd_adr <= 'd1;

else if(bit_clk_en)

o_rd_adr <= o_rd_adr + 7'd1;

else

o_rd_adr <= o_rd_adr;

end 综合时出现[Synth 8-91] ambiguous clock in event control。

解决办法是在begin end 中加入复位初始化条件,或者删除@()中的 or posedge rst即可。

而在Diamond中对该情况不会进行报错。

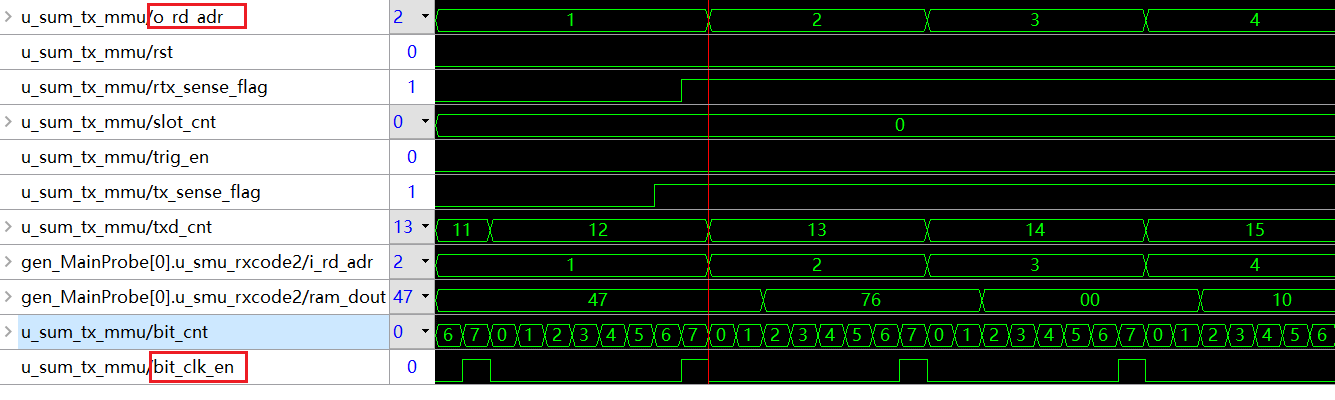

这导致在调试时遇到Reveal抓取的逻辑与预期的并不相符,出现不规律乱跳的情况,如下图:

o_rd_adr应该在bit_clk_en为1时自加一,其他情况下保持不变。而实际中o_rd_adr并不是预期的效果。

解决办法:删除掉or posedge rst(由于块中未使用rst故改成同步复位),再进行调试即正确。