简要记录一下:实验任务是通过自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测

试(该AXI配置的AXI FULL模式)。即PL端通过按下按键KEY后向PS端的DDR3写入数据,然后PS端可以通过串口读出数据并且可以通过ILA去抓出PL端的写模块写入的数据比较是否一致

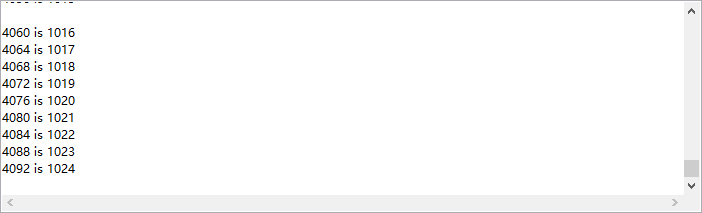

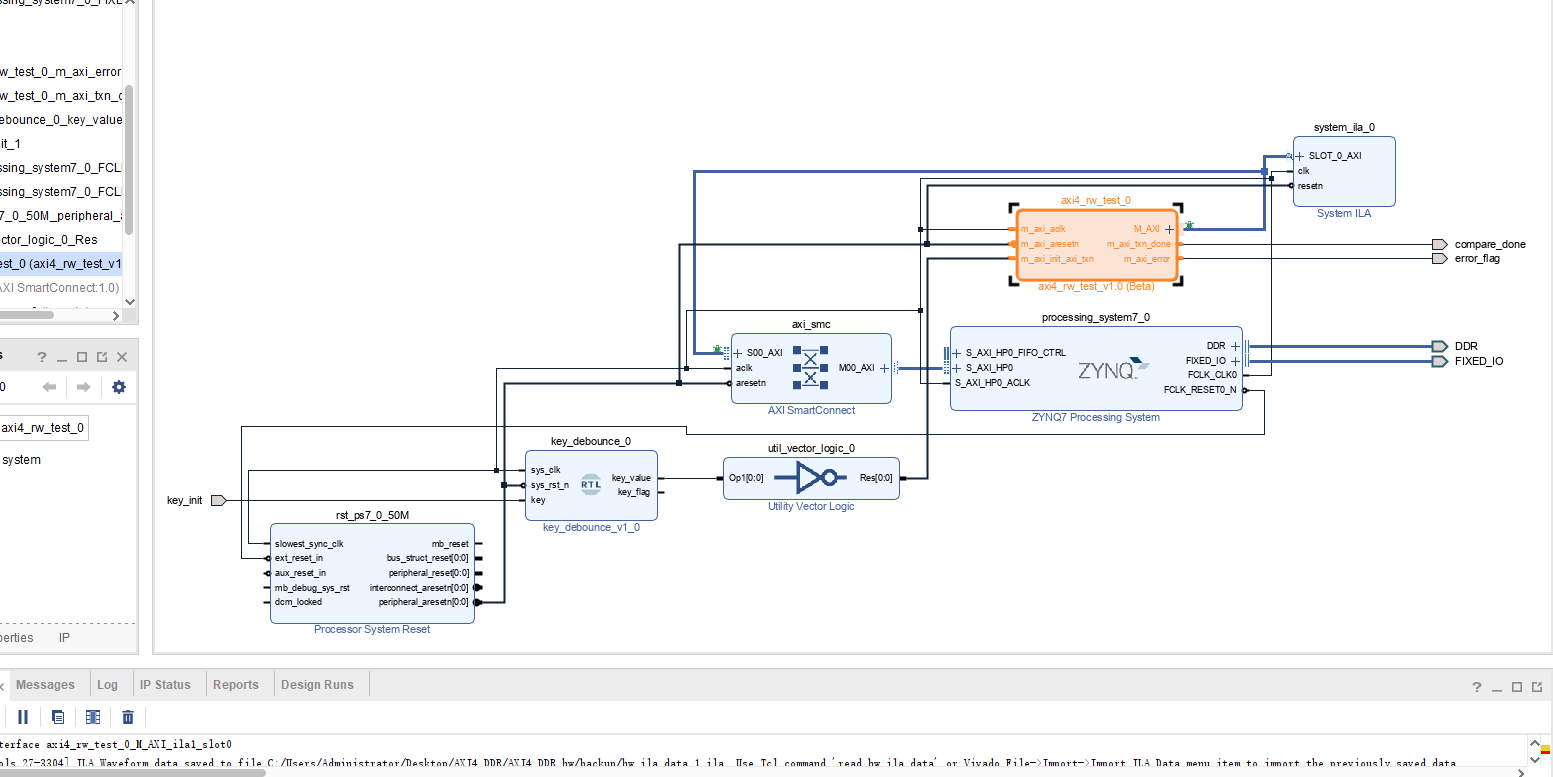

硬件框图:

DDR3 Test 是自定义的 IP 核,具有 AXI4 Master 端口,该端口通过 AXI Smartconnect模块,最终连接到 PS 端的 S_AXI_HP0 端口。输入的按键控制 DDR3 Test 模块对 PS 的 DDR3 进行读写测

试,并在读写测试结束后,通过两个 PL LED 灯分别指示读写完成和读写错误 。

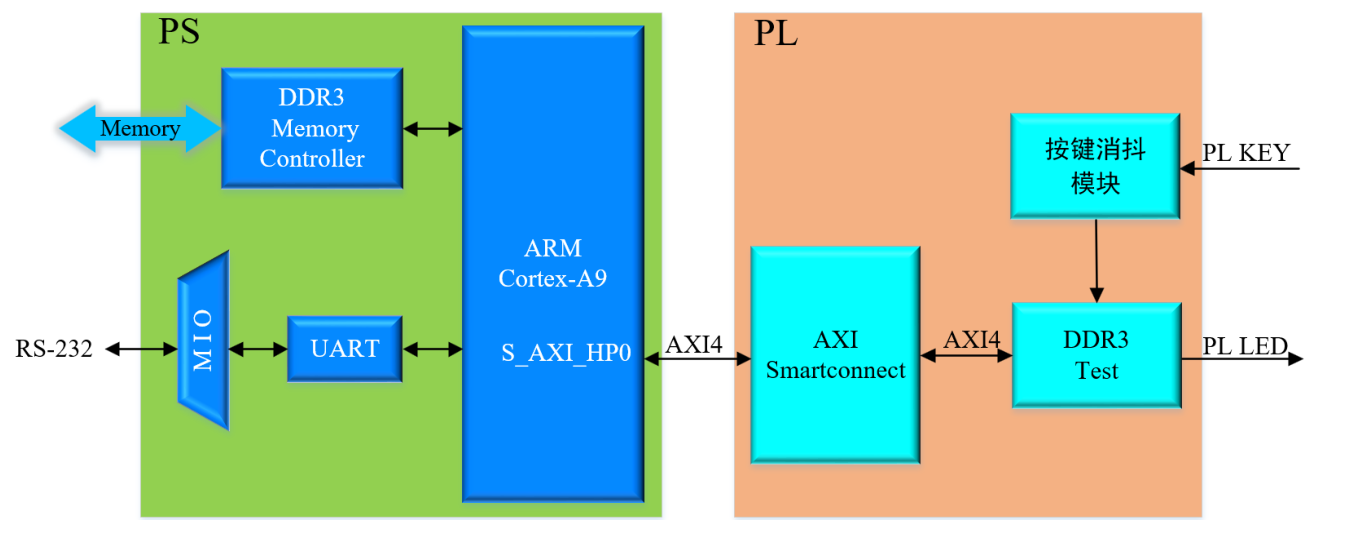

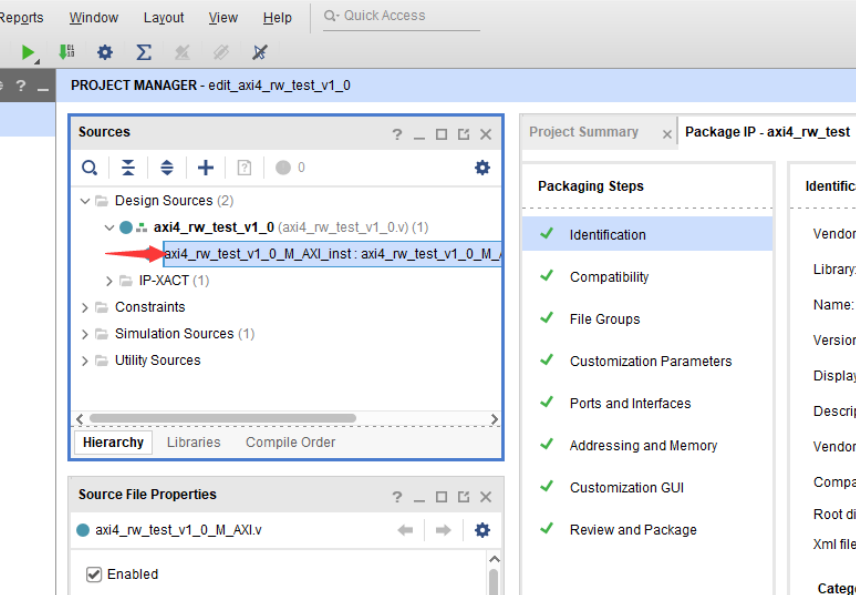

自定义IP核axi4_rw_test IP核:

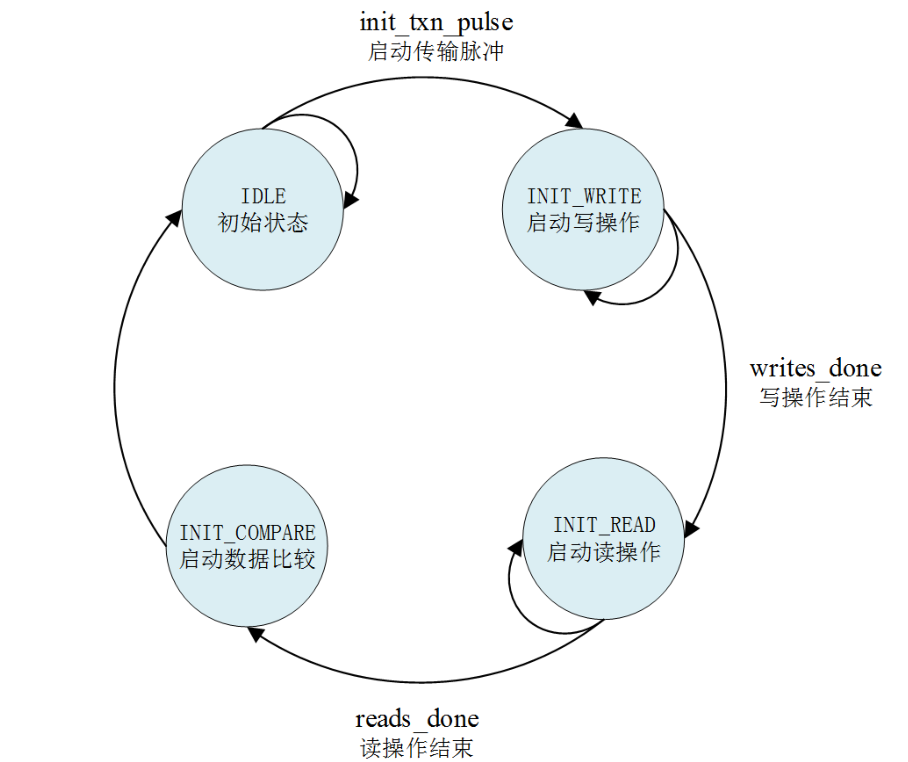

该IP核里有两个模块,最底层模块是读写控制模块,状态机控制逻辑:

该IP核里有两个模块,最底层模块是读写控制模块,状态机控制逻辑:

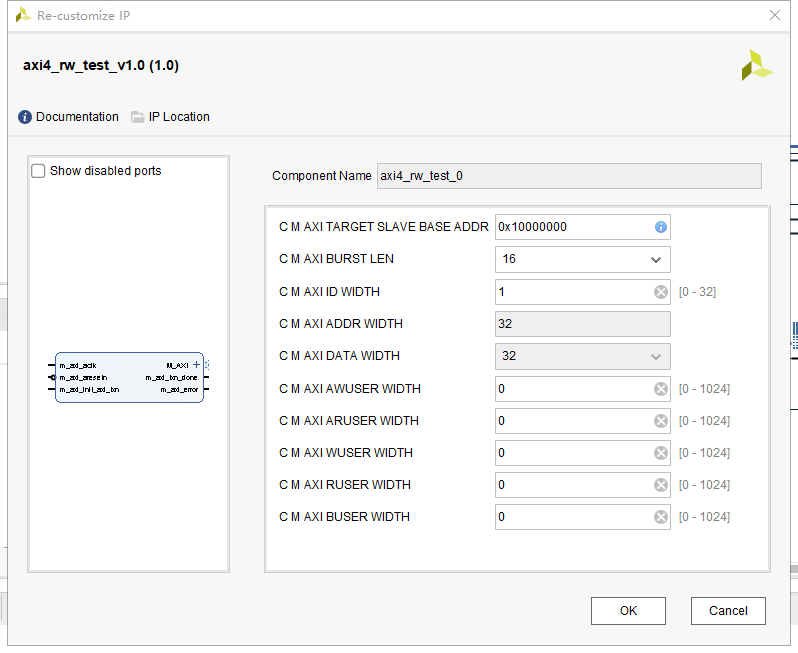

硬件block design:

生成bit流导出至vitis平台:

#include "stdio.h"

#include "xil_cache.h"

#include "xil_printf.h"

#include "xil_io.h"

int main()

{

int i;

char c;

Xil_DCacheDisable();

printf("AXI4 PL DDR TEST");

while(1)

{

scanf("%c",&c);

if(c == 'c'){

printf("start\r\n");

for(i=0;i<4096;i=i+4)

{

printf("%d is %d\n",i,(int)(Xil_In32(0x10000000+i)));

}

}

}

return 0;

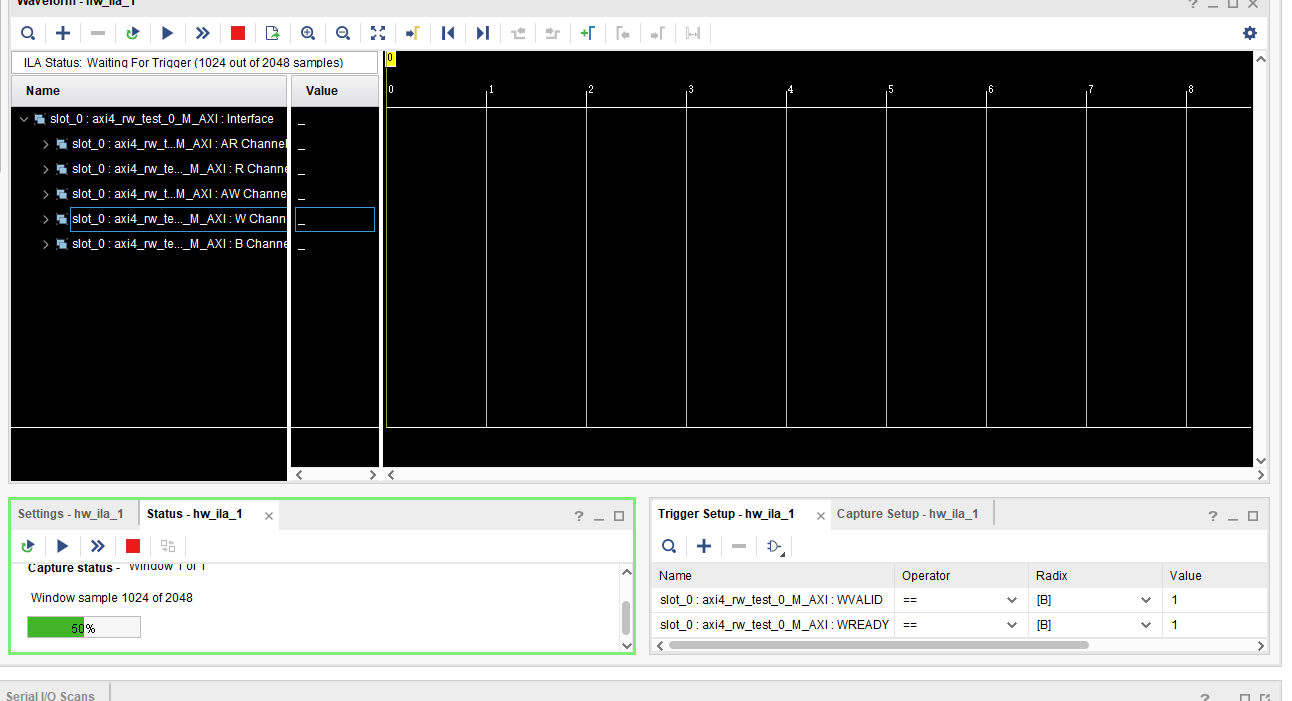

}烧录代码:可以看见串口和ILA抓出的数据通道并没有数据,等待着PL key按键按下后触发

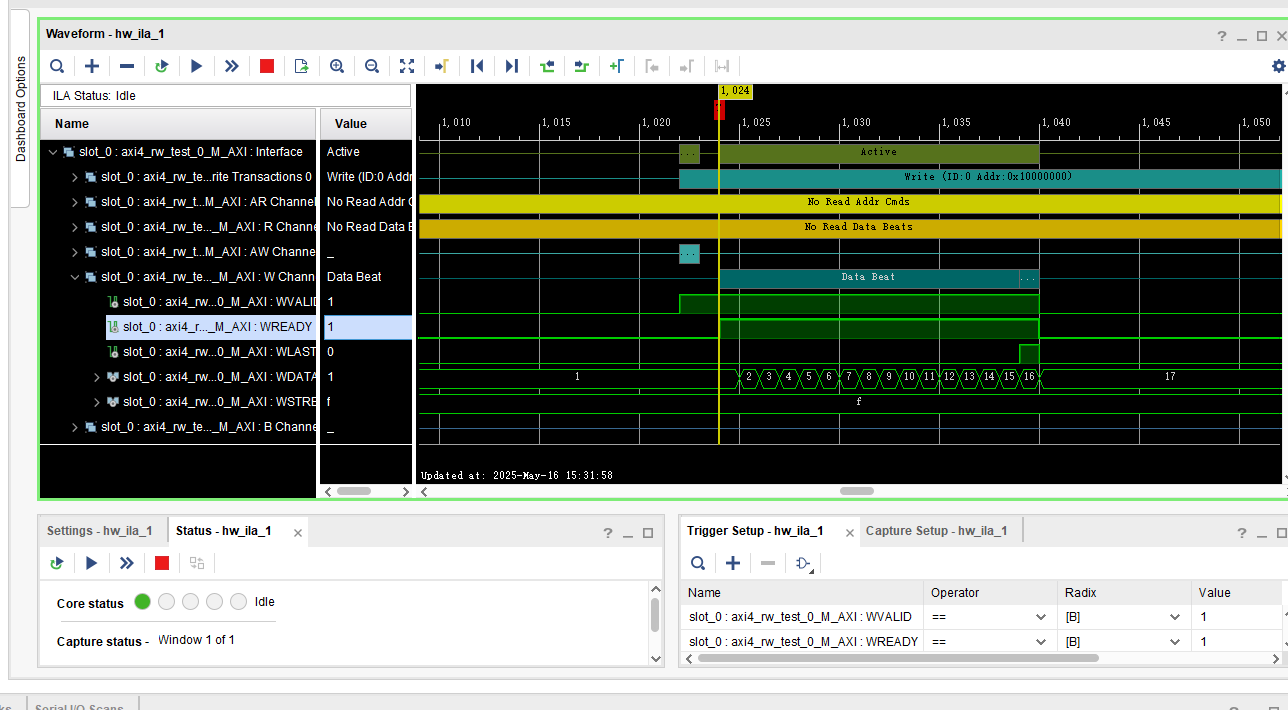

按下PL端按键后:当捕获到数据通道的valid和ready信号都拉高后,开始发送数据

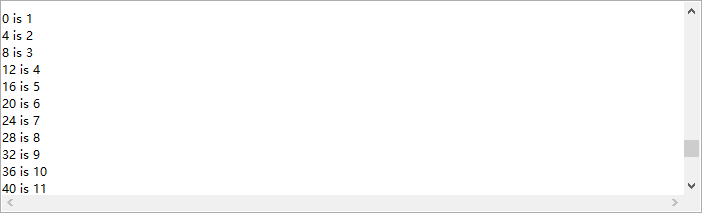

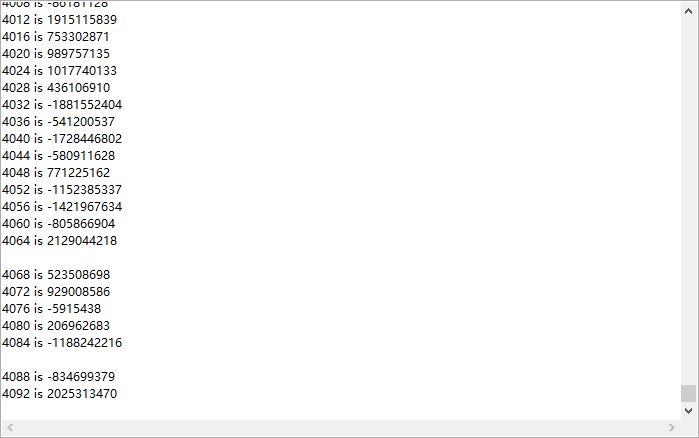

此时PS串口也能读出数据: