本文参考Xilinx官方文档UG470

加载配置

配置文件类型

a)在AMD ISE中,BitGen用于将布局布线后的NCD文件转换为配置文件或比特流。PROM文件生成工具PROMGen则可将一个或多个比特流文件转换为PROM文件。在AMD Vivado中,功能等效的Tcl命令分别为WRITE_BITSTREAM和WRITE_CFGMEM。生成的PROM文件可呈现为多种格式,且不仅限于在PROM器件中使用;这些文件可存储于任何位置,并通过任意方式传输至目标系统。

b)

1)BIT文件:二进制配置文件,包含头部信息(无需下载到FPGA)。用于通过编程电缆,配合iMPACT工具或Vivado设备编程器对器件进行编程;

2)RBT文件:BIT文件的ASCII等效格式,包含文本头部以及用ASCII字符1和0表示的配置数据(每个配置位占用8个字符);

3)BIN文件:纯二进制配置文件,不含头部信息。适用于自定义配置方案(例如由微处理器控制),或在某些情况下用于对第三方PROM进行编程;

4)MCS文件:一种ASCII PROM文件格式,除配置数据外,还包含地址和校验和信息。主要用于设备编程器和iMPACT工具;

5)HEX文件:一种ASCII PROM 文件格式,仅包含配置数据。主要用于自定义配置方案。

总线位宽自动检测

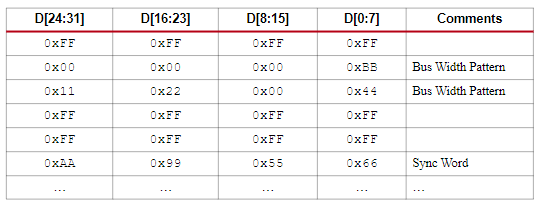

a)在所有比特流的起始位置,均会插入一个总线宽度自动检测模式。此功能应用于并行配置模式下,以自动识别配置总线的位宽。由于该模式出现于同步字之前,串行配置模式会将其忽略。对于并行配置模式,配置逻辑会自动检测总线宽度。一个总线宽度检测模式被放置在比特流的最前面。配置逻辑最初只检查并行总线的低8位。根据接收到的字节序列,配置逻辑能自动切换到相应的外部总线宽度。

b)总线宽度自动检测对大多数用户是透明的,因为AMD工具生成的所有配置比特流(BIT或RBT文件)都已包含总线宽度自动检测模式。如果模式引脚被设置为主串行、从串行、JTAG或SPI模式,配置逻辑将忽略这些模式。

1)对于x8总线,配置总线宽度检测逻辑首先在D[0:7]引脚上找到0xBB,紧接着是0x11;

2)对于x16总线,配置总线宽度检测逻辑首先在D[0:7]引脚上找到0xBB,紧接着是0x22;

3)对于x32总线,配置总线宽度检测逻辑首先在D[0:7]引脚上找到0xBB,紧接着是0x44。

c)如果在0xBB之后立即出现的字节不是0x11、0x22、0x44,总线宽度状态机将重置,并继续搜索下一个0xBB,直到找到有效的序列。随后,它会切换到相应的外部总线宽度,并开始寻找同步字。一旦检测到总线宽度,SelectMAP接口将被锁定为该宽度,直至发生电源循环、PROGRAM_B脉冲、JPROGRAM复位、IPROG复位。

生成存储文件

a)PROM文件可由比特流文件生成。在ISE中使用PROMGen实用程序,或在Vivado中使用Tcl命令WRITE_CFGMEM。用户可直接从命令行访问PROMGen,或通过iMPACT的文件生成模式间接访问。PROM文件的作用是:为PROM编程重新格式化比特流文件,并为串行菊花链组合多个比特流文件。

b)串行菊花链的配置数据需要特殊格式化,因为不能简单地将多个独立的BIT文件连接起来对菊花链进行编程。这种特殊格式化在通过多个比特流生成PROM文件时,由PROMGen(或iMPACT)完成。要生成PROM文件,需使用PROMGen的-n、-u、-d选项,或使用iMPACT文件生成向导来指定多个比特流。对于WRITE_CFGMEM Tcl命令,请使用参数-loadbit "up|down <bitfile1.bit> <bitfile2.bit>"。

c)PROMGen通过将下游配置数据嵌套到上游器件的配置包中,来重新格式化配置比特流。若试图通过向第一个器件发送多个比特流来编程整个链,将导致第一个器件完成自身配置后,忽略后续的所有数据。

d)MCS文件格式最常用于编程AMD的配置PROM,这些PROM进而以SelectMAP模式对单个FPGA进行编程。对于自定义配置解决方案,BIN和HEX文件因其原始数据格式而成为最容易使用的PROM文件格式。某些情况下可能需要额外的格式化。如果一个SelectMAP配置的多个配置比特流存放在单个存储器件中,则不得将这些比特流合并成一个串行菊花链PROM文件。相反,应使用多个BIN或HEX文件对目标存储器件进行编程。

e)PROMGen中的-d和-u选项、iMPACT文件生成向导或write_cfgmem命令的-loadbit参数,用于为第三方闪存器件创建PROM文件。应选择第三方编程器支持的输出格式。某些BPI器件在编程PROM文件时需要启用字节序交换。请参考闪存供应商的文档。

f)位交换

1)位交换是指交换一个字节内的比特位。MCS PROM文件格式通常始终进行位交换,除非使用针对SPI配置模式的PROMGen -spi选项或write_cfgmem -interface spi1|spi2|spi4选项。HEX文件格式可根据用户选项选择是否进行位交换。比特流文件(BIT、RBT、BIN)则从不进行位交换。

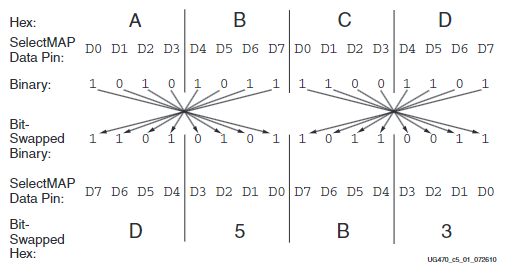

g)并行总线比特顺序

1)在SelectMAP x8模式下,配置数据以每个CCLK周期一个字节的速率加载,其中每个字节的最高有效位(MSB) 提供给D0引脚。尽管这一约定(D0 = MSB,D7 = LSB)与许多其他器件不同,但在所有AMD FPGA中保持一致。此位交换规则同样适用于7系列FPGA的BPI x8模式和ICAPE2接口。在7系列器件中,位交换规则被扩展至x16和x32总线宽度,即数据在每个字节内部进行位交换。

h)延迟配置

1)如需延迟配置,应在初始化阶段将INIT_B引脚保持为低电平。一旦INIT_B变高,便无法再通过将其拉低来延迟配置。

2) 从上电复位或PROGRAM_B复位开始,INIT_B被驱动为低,表示FPGA正在初始化(清除)其配置内存。在模式引脚被采样之前,INIT_B是一个输入,可将其保持为低以延迟配置。在模式引脚被采样之后,INIT_B是一个开漏、低电平有效的输出,指示配置期间是否发生CRC错误、配置后是否发生回读CRC错误(若启用):①0表示发生CRC或IDCODE错误(DONE为低),或发生回读CRC错误(DONE为高且回读CRC已启用);②1表示无CRC错误,初始化完成。

3)INIT_COMPLETE是内部信号,可通过7系列FPGA状态寄存器访问,指示INIT_B信号是否已在内部释放。

4)MODE_STATUS[2:0]是内部信号,可通过7系列FPGA状态寄存器访问,反映状态寄存器被读取时所采样的模式引脚值。

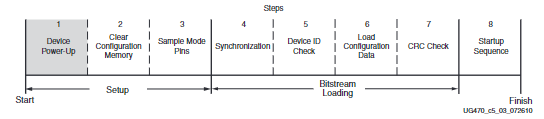

加载顺序

a)

b)步骤1:上电

1)配置7系列器件需要为VCCINT、VCCAUX、VCCBRAM、 VCCO引脚供电。电源时序要求在相应的7系列FPGA数据手册中描述。

2)所有JTAG配置引脚都位于一个独立的专用存储区,具有专用的电压供给VCCO0。多功能引脚位于bank14和15。所有专用输入引脚工作在VCCO0的LVCMOS电平。所有活动的专用输出引脚工作在VCCO0电压电平,输出标准设置为LVCMOS,12mA驱动,快转换率。如果使用了Persist选项,所选配置模式的双模式I/O在配置后保持活动状态,I/O标准设置为LVCMOS,12mA驱动,慢转换率。对于所有使用多功能I/O的模式,相关的 VCCO14/VCCO15必须连接到适当的电压,以匹配配置器件的I/O标准。这些引脚在配置期间也是LVCMOS,12 mA驱动,快转换率。→①在配置阶段,对于用作配置接口的I/O引脚,FPGA内部强制它们工作在快压摆率(以及LVCMOS, 12mA驱动)模式。这是为了确保配置数据通信的可靠性和时序裕量,用户无需也无法选择;②在用户模式(即配置完成后),如果信号频率较高(>50MHz),走线较长且存在阻抗不连续,且总线上负载较多时,选择快压摆率;如果信号频率较低,为了降低EMI,且对信号完整性要求不高时,选择慢压摆率。

3)上电时,VCCINT电源引脚必须由1.0V或0.9V(对于-2L器件)电源供电。除了VCCO0之外,其他I/O电压在7系列FPGA的JTAG模式配置时无需供电。当选择使用多功能引脚的配置模式(即串行、主BPI、SPI、SelectMAP)时,也必须为VCCO14、VCCO15或两者供电。强烈建议将这两个电源的电压设置得与VCCO0完全相同。因为配置接口的引脚可能横跨这三个Bank,统一电压可避免复杂的电平转换和潜在的启动问题(如0-1-0毛刺)。

4)

①VCCINT:核心逻辑电源。为FPGA内部所有可编程逻辑(CLB、DSP、BRAM控制器、时钟网络等)供电。是功耗最高、最需要干净、稳定的电源。纹波和噪声要求极高。必须使用高质量电源并遵循布局布线指南;

②VCCBATT:AES解密器密钥存储器备份电源。如果未使用密钥存储器,用户应将此引脚连接到VCCAUX或GND;

③VCCAUX:为配置电路、JTAG、MMCM/PLL、XADC、电平转换器等关键模拟和辅助模块供电。必须在配置前稳定。其稳定性影响配置可靠性、时钟性能、全局复位网络;

④VCCAUXIO:辅助I/O电路电源。为HP Bank的I/O缓冲区中的某些辅助电路供电;

⑤VCCBRAM:BRAM电源。专门为FPGA内部的BRAM存储单元供电。通常与VCCINT使用同一电源轨。在要求严格的应用中可独立供电以优化BRAM性能;

⑥VCCO0:配置组电源电压;

⑦VCCO14/15:多功能配置引脚输出电源电压。

5)

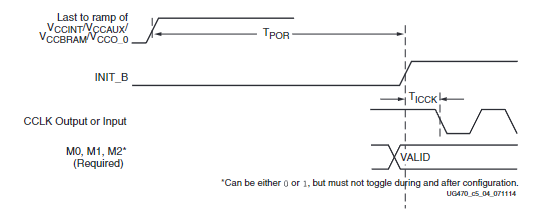

其中Tpor是上电复位延迟;Tcclk是CCLK输出延迟。

6)为确保正确的上电行为,必须遵循相应7系列FPGA数据手册中的指南。电源应在数据手册规定的电源上升时间范围内单调上升。所有电源电压都应在推荐的工作范围内,任何低于VDRINT的 VCCINT跌落或低于VDRI(具体值见相应的7系列FPGA数据手册)的VCCAUX跌落都可能导致配置数据丢失。

7)如果无法实现单调上升,可在系统电源达到VCCO0、VCCAUX、VCCBRAM、VCCINT的最小推荐工作电压之前,通过将INIT_B引脚保持为低电平来延迟配置。某些配置模式涉及bank14或15,当这些存储区参与配置时,其各自的电源 VCCO14/15也必须在INIT_B释放为高电平之前达到其最小推荐工作电压。

8)上电后,可以通过将PROGRAM_B引脚置为低电平来进行重新配置。

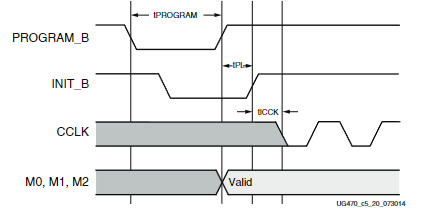

c)步骤2:清除配置内存

1)每当器件上电、PROGRAM_B引脚被脉冲拉低、使用JTAG JPROGRAM指令、使用IPROG命令、在回退重试配置序列期间,配置内存都会被顺序清除。BRAM被重置为其初始状态,触发器通过断言全局置位复位GSR被重新初始化。在此期间,除少数配置输出引脚外,I/O通过使用全局三态GTS被置于高阻状态,并且如果PUDC_B为低电平,内部将有上拉电阻。在上电情况下,INIT_B在初始化期间被内部驱动为低电平,然后在TPOR之后释放;在其他情况下,则在TPL之后释放。如果INIT_B引脚被外部保持为低,器件将在此初始化过程中等待,直到该引脚被释放,并且满足TPOR或TPL延迟。PROGRAM_B的最小低脉冲时间由TPROGRAM时序参数定义。

d)步骤3:采样模式引脚

1)当 INIT_B 引脚转换到高电平时,器件对M[2:0]模式引脚进行采样,如果处于主模式则开始驱动CCLK。此时,器件开始在配置时钟的上升沿对配置数据输入引脚进行采样。对于BPI和SelectMAP模式,总线宽度初始为x8,状态寄存器反映了这一点。在总线宽度检测序列之后,状态寄存器被更新。模式引脚仅在通过电源循环或断言PROGRAM_B进行重新配置时才会被重新采样。

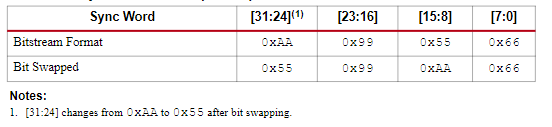

e)步骤4:同步

1)对于BPI、从SelectMAP、主SelectMAP模式,必须首先检测总线宽度。总线宽度检测模式被从串行、主串行、SPI、JTAG模式忽略。然后,必须向配置逻辑发送一个特殊的32位同步字(0xAA995566)。同步字通知器件即将到来的配置数据,并将配置数据与内部配置逻辑对齐。在同步之前,配置输入引脚上的任何数据都会被忽略。同步对大多数用户是透明的,因为工具生成的所有配置比特流都包含总线宽度检测模式和同步字。

f)步骤5:检查器件ID

1)器件同步后,在加载配置数据帧之前必须通过器件ID检查。这可以防止使用为其他器件格式化的比特流进行配置。如果配置期间发生ID错误,器件将尝试进行回退重新配置。器件ID检查内置于比特流中,使此步骤对大多数设计者透明。器件ID检查是通过比特流中的命令对配置逻辑执行的,而不是通过此情况下的JTAG IDCODE寄存器。

g)步骤6:加载配置数据帧

1)加载同步字并检查器件ID后,将加载配置数据帧。此过程对大多数用户是透明的。

h)步骤7:循环冗余校验

1)加载配置数据帧时,器件会根据配置数据包计算循环冗余校验(CRC)值。加载配置数据帧后,配置比特流可以向器件发出检查CRC指令,后跟预期的CRC值。如果器件计算的CRC值与比特流中的预期CRC值不匹配,器件会将 INIT_B 拉低并中止配置。默认情况下,配置比特流包含CRC检查,但设计者可以根据需要禁用它。如果禁用CRC检查,则存在加载错误配置数据帧的风险,可能导致设计行为不正确或损坏器件。

2)对于加密比特流(当 BITSTREAM.ENCRYPTION.ENCRYPT 属性为Yes时),CRC检查被禁用,取而代之的是HMAC对加密比特流数据进行身份验证。比特流数据中的错误在BOOTSTS寄存器中报告为HMAC错误。

3)如果FPGA作为配置主机的模式下配置期间发生CRC错误,器件可以尝试进行回退重新配置。在BPI和SPI模式下,如果回退重新配置再次失败,只能通过脉冲PROGRAM_B引脚并从头重新启动配置过程来重新同步BPI/SPI接口。JTAG接口仍然有响应,器件仍然存活,只是BPI/SPI接口无法操作。在SelectMAP模式下,可以脉冲PROGRAM_B引脚为低,或发起ABORT序列

4)7系列器件使用32位CRC检查。CRC检查旨在捕获传输配置比特流时的错误。存在一种情况,传输配置比特流时的错误可能被CRC检查遗漏:某些时钟错误,例如双时钟,可能导致32位比特流包与配置逻辑之间失去同步。同步丢失后,任何后续命令都无法被理解,包括检查CRC的命令。在这种情况下,配置会失败,DONE为低,INIT_B为高,因为CRC被忽略了。在BPI模式异步读取中,地址计数器最终会溢出或下溢导致回绕,从而触发回退重新配置。BPI同步读取模式不支持回绕错误条件。

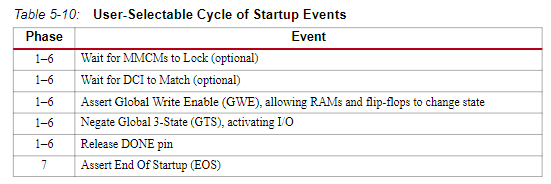

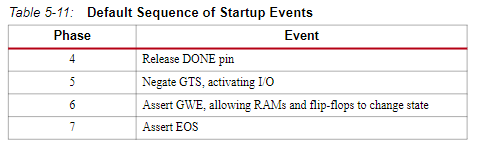

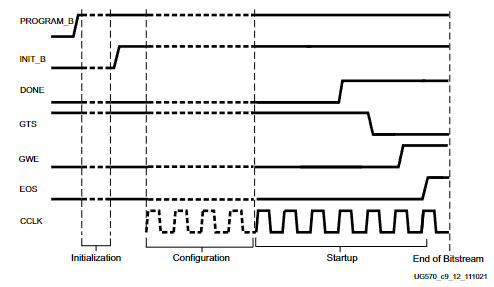

i)步骤8:启动阶段

1)加载配置帧后,比特流指示器件进入启动序列。启动序列由8相(阶段0-7)顺序状态机控制。

2)具体启动事件的顺序(EOS断言除外)可通过比特流选项进行用户编程。

3)通过适当的选项,可以强制启动序列等待MMCM锁定或DCI匹配。这些选项通常用于防止在MMCM锁定和/或DCI匹配之前断言DONE、GTS和GWE(从而阻止器件运行)。

4)DONE信号由启动序列器在用户指示的周期释放,但启动序列器要等到DONE引脚实际检测到逻辑高电平时才会继续。DONE引脚是一个开漏双向信号。通过释放DONE引脚,器件停止驱动逻辑低电平,该引脚被内部上拉电阻拉高。默认情况下,DONE_PIPE被启用,以在DONE引脚和配置逻辑之间添加一个寄存器。

5)与启动序列器相关的信号

①DONE:指示配置完成。可外部保持为低以与其他FPGA同步启动。

②Release_DONE:指示器件是否已停止驱动DONE引脚为低。如果该引脚被外部保持为低,Release_DONE可能与DONE引脚的实际值不同。

③GWE:断言时,GWE启用CLB和IOB触发器以及FPGA上的其他同步元件。GWE与配置时钟(CCLK)同步断言,并且在整个芯片上具有显著的偏移。因此,时序元件不会与用户的系统时钟同步释放,并且在启动期间可能发生时序违规。建议在启动后复位设计和/或应用其他同步技术。

④GTS:断言时,GTS禁用除少数配置引脚外的所有I/O驱动器。

⑤EOS:EOS指示配置和启动过程的绝对结束。

⑥DCI_MATCH:指示所有DCI控制器何时已将其内部电阻与外部参考电阻匹配。

⑦MMCM_LOCK :指示所有时钟管理模块何时就绪。默认情况下该信号被断言。如果在MMCM上使用了LOCK_WAIT选项,并且在生成比特流时使用了LockCycle选项,则此信号有效。

⑧

j)

1)启动结束前的时钟要求:默认情况下,DONE在启动阶段4释放,并且启用DONE_PIPE以增加一个额外的时钟周期延迟。DONE指示配置已完成且所有数据已加载,但需要施加一些额外的时钟周期以确保启动序列一直正确完成到阶段7(启动结束)。DONE变高后所需的时钟周期数建议保守估计为64;这将满足最常见的使用情况。比特流选项LCK_cycle或Match_cycle将增加未定义的额外时钟周期数。

2)启动结束时的I/O转换:在Spartan7、Artix7、Kintex7系列中,多功能配置引脚位于HR I/O bank上,如果bank的VCCO为1.8V或更低,并且该bank上的引脚为低电平或浮空,则在配置启动期间,输入到互连逻辑可能会发生0--1--0转换。由于此转换发生在GWE启用内部逻辑之后,可能会影响配置后器件的内部状态。该转换发生在EOS(启动结束)后的一个CFGCLK周期。为避免此转换,请将VCCO14/15设置为2.5V或3.3V,或者外部驱动引脚为高电平。否则,设计逻辑应以忽略这些受影响的输入信号,直到至少在EOS上升沿之后一个CFGCLK周期后的200纳秒。CFGCLK和EOS可以使用STARTUPE2原语进行监控。

3)在多功能配置引脚上使用DCI:如果在I/O bank14或15中的任何配置引脚在用户设计中分配了DCI I/O标准,则设计中还应包含并使用 DCIRESET原语。设计应脉冲DCIRESET的RST输入,然后在断言LOCKED信号之后,再使用具有DCI标准的多功能配置引脚上的任何用户输入或输出。当多功能配置I/O引脚作为配置引脚运行时,它们会忽略器件初始化期间发生的初始DCI校准。

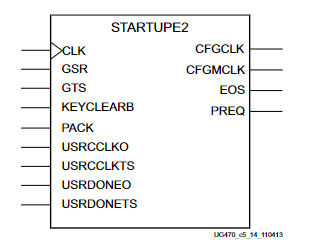

STARTUPE2 原语

a)STARTUPE2原语在用户逻辑与配置逻辑的控制和状态信号之间提供了一个接口。其许多引脚与启动序列相关,包括CLK信号,允许用户指定启动时钟。

b)

1)CLK:这是启动序列的用户自定义时钟源输入。默认情况下,启动序列(包括释放DONE、撤销GTS、断言GWE等)由配置时钟(CCLK)驱动。通过此引脚,用户逻辑可以提供一个更精确或与系统同步的时钟来驱动这些关键事件的时序。当在比特流中设置BITSTREAM.STARTUP.STARTUPCLK=UserClk时,启动序列器将在阶段0等待此引脚上的时钟有效,然后使用该时钟进行后续的启动状态机转换。Spartan-7 7S6和7S15不支持此功能。具体例子:多器件同步启动。在一个由多个FPGA组成的系统中,需要确保所有FPGA在同一时刻激活I/O。可以将一个全局的系统时钟连接到每个FPGA STARTUPE2的CLK输入,并设置使用用户时钟启动。这样,所有FPGA的启动序列(GTS撤销、GWE断言)都将由同一个系统时钟同步,避免了因各FPGA内部CCLK频率微小差异导致的时序偏差。

2)GSR:这是一个异步的、全局性的复位信号,会直接影响所有CLB触发器的初始状态。由于是异步信号且在整个芯片上存在布线延迟(偏斜),不同区域的触发器可能在不同时间被释放,极易引发亚稳态问题。该信号的功能与上电配置期间自动执行的GSR初始化完全相同,但在用户模式下使用风险极高。在设计中将其永久拉低。系统复位应通过用户设计的同步复位网络实现。具体例子:紧急全局复位。在极端情况下(如检测到无法恢复的系统错误),逻辑可以拉高GSR,使所有触发器瞬间回到初始值。但必须意识到,这会异步于所有时钟,复位后系统状态高度不确定。更安全的做法是触发重配置(通过IPROG或PROGRAM_B)。

3)GTS:当此信号为高时,所有用户I/O(除了配置Bank 0、14、15中用作配置的引脚)的输出驱动器将被禁用,进入高阻态。这与配置期间的行为一致。该控制是即时生效的,不受时钟控制。具体例子:总线隔离与热插拔。当FPGA作为共享总线(如并行数据总线)上的一个节点时,在FPGA上电、掉电或进入低功耗模式前,用户逻辑可以拉高GTS,使所有I/O变为高阻,防止损坏总线或干扰其他器件通信。待就绪后再拉低GTS恢复驱动。

4)KEYCLEARB:这是一个安全销毁功能。当此引脚被持续拉低超过TPROGRAM时间(典型值约数毫秒,见数据手册),存储在电池备份RAM(BBRAM)中的AES解密密钥将被永久擦除。此操作不可逆。之后,任何使用该BBRAM密钥加密的比特流将无法配置此FPGA。仅影响BBRAM中的密钥,不影响eFUSE中的密钥。具体例子:防篡改响应。在安全设备中,可将物理防篡改传感器(如机箱开关)的信号连接到KEYCLEARB。一旦检测到机箱被非法打开,立即拉低此引脚,销毁密钥,使设备中的加密IP失效,保护核心知识产权。

5)PREQ (输出) & PACK (输入) - 重配置握手信号:这是一对握手信号,用于实现用户控制的重配置。仅在比特流中设置PROG_USR属性后生效。当外部触发重配置(PROGRAM_B引脚被拉低,或通过JTAG发送JPROGRAM指令)时,配置逻辑不会立即执行,而是先拉高PREQ(请求)。用户逻辑检测到PREQ变高后,执行必要的安全关闭序列(如保存关键状态、停止对外部器件操作、将接口置于安全状态)。准备就绪后,用户逻辑拉高PACK(确认)。配置逻辑收到PACK后,才正式开始清除配置内存的重配置流程。具体例子:通信系统业务无损切换:在一个软件定义无线电(SDR)设备中,FPGA需要在线加载新的波形文件(重配置)。在重配置请求到来时,用户逻辑通过PREQ获知,并首先命令射频前端停止发射/接收,将数据链路层状态保存到外部存储器,然后拉高PACK。这样可以避免重配置期间信号中断对系统造成损害或数据丢失。

6)USRCCLKO (输入) & USRCCLKTS (输入) - 用户CCLK控制:用户逻辑通过USRCCLKO驱动一个时钟,该时钟将在配置完成后输出到FPGA的CCLK引脚上。前3个时钟周期用于内部切换,不会出现在外部引脚。USRCCLKTS为高时,强制CCLK引脚为高阻态;为低时,CCLK引脚输出USRCCLKO的时钟。从USRCCLKO到CCLK引脚输出的延迟TUSRCCLKO在数据手册中定义,需要考虑在高速应用时。具体例子:配置后访问SPI Flash。许多系统将FPGA比特流和处理器启动代码存放在同一个SPI Flash中。配置完成后,FPGA内的软核处理器(如MicroBlaze)需要读取Flash中的程序。此时,用户逻辑可以生成SPI时钟,通过USRCCLKO送到CCLK引脚,并连接到SPI Flash的CLK输入端,从而直接复用配置阶段的硬件连接来访问Flash,节省I/O资源。

8)USRDONEO (输入) & USRDONETS (输入) - 用户DONE控制:用户逻辑驱动USRDONEO,将直接反映到DONE引脚的电平上(当USRDONETS为低时)。USRDONETS为用户DONE三态控制,高电平时,DONE引脚为高阻;低电平时,DONE引脚输出USRDONEO的值。这允许用户逻辑完全接管DONE引脚的行为。具体例子:多FPGA配置同步(线或逻辑)。当多个FPGA的DONE引脚需要连接在一起(线或)以指示整个系统配置完成时,可将每个FPGA的USRDONETS设为低,USRDONEO初始为低。每个FPGA在自身配置完成且准备好后,将USRDONEO置高。只有当所有FPGA都置高时,共享的DONE网络才为高,实现了硬同步。

9)CFGCLK:输出配置逻辑在主模式下使用的时钟。频率由比特流的ConfigRate选项决定(典型值如3MHz, 66 MHz)。如果启用了Persist选项,该时钟在配置完成后仍保持活动。这是观察配置逻辑内部时序的窗口。具体例子:Persist模式下的外设通信.在Master SPI模式下,如果启用了Persist,配置引脚在配置后不会释放,FPGA可以继续与SPI Flash通信。此时,用户逻辑可以使用CFGCLK作为时钟基准,来产生符合SPI Flash时序的读/写命令,实现配置后对Flash的数据读写。

10)CFGMCLK:固定输出约65 MHz的时钟,源自芯片内部的环形振荡器。该时钟在配置初期即存在,只要VCCAUX上电就始终有效,即使FPGA未配置。这是一个非常稳定的早期可用时钟源。具体例子:配置逻辑的辅助时钟。在某些需要与配置过程并行执行的操作(罕见)中,可以作为参考时钟。更常见的用法是,在调试时用其评估内部振荡器的频率稳定性。

11)EOS:这是一个高电平有效的标志信号,在启动序列的最后一个阶段(阶段7) 被断言。它标志着配置和启动过程彻底结束,FPGA完全进入用户模式,所有用户逻辑开始正式运行。这是释放整个系统复位的理想信号。具体例子:系统全局复位生成。将EOS信号连接至用户设计中的复位发生器,作为上电后整个系统释放复位的条件。确保在FPGA完全就绪前,所有逻辑保持复位状态。

c)STARTUPE2原语上的USRCCLKO输入允许用户逻辑在配置后驱动CCLK引脚。当USRCCLKO和POST_CRC回读功能同时使用时,USRCCLKO也可以为POST_CRC回读逻辑提供时钟。从内部USRCCLKO到CCLK引脚的延迟在数据手册中定义为 TUSRCCLKO。在启动结束(EOS)之后,USRCCLKO上的前三个时钟周期用于切换时钟源,不会输出到外部CCLK引脚。这有助于防止从内部振荡器切换到用户时钟时CCLK出现毛刺。然而,如果配置时使用了外部主控CCLK引脚EMCCLK,则在USRCCLKO的三个时钟周期允许切换到新的用户时钟之前,CCLK上将继续呈现EMCCLK信号。

比特流组成

a)在器件上电且初始化完成(由INIT_B引脚释放指示)后,配置过程即可开始。初始化完成后,数据包处理器会忽略呈现在配置接口上的所有数据,直至识别出一个特定的数据模式(通常是同步字)。对于外部并行接口(BPI或SelectMAP模式),首先由总线宽度自动检测模式设置配置接口的总线宽度。总线宽度设置完成后,对于所有配置接口,在识别出同步字之前,配置逻辑将忽略接口上的所有数据。完成同步后,配置逻辑将每个32位数据字作为一个配置数据包或多个字的配置数据包的一部分进行处理。

b)比特流远非简单的配置数据堆砌,而是一个结构严谨的、驱动FPGA内部配置状态机完成从初始化到启动全过程的命令和数据序列。

1)前导与同步 (Preamble & Synchronization)

①哑填充字 (Dummy Words, 例如 FFFFFFFF):提供初始的时间裕量,确保配置接口(尤其是时钟和数据)在关键命令到来之前达到稳定状态。也用于填充到特定的对齐边界。

②总线宽度自动检测模式 (Bus Width Auto-Detect Pattern, 000000BB, 11220044):对于并行配置模式,此模式允许FPGA自动识别数据总线是x8、x16、x32宽度。FPGA监控D[7:0],根据0xBB后紧跟的是0x11、0x22还是0x44来决定总线宽度。

③同步字 (Sync Word, AA995566):如果配置失败且DONE为低、INIT_B为高,通常是未能成功同步(如CCLK时序问题、数据位序错误)。在调试中,验证同步字是否正确发送是第一步。

2)配置寄存器初始化与全局设置 (Register Initialization & Global Settings)

①空操作 (NOOP, 20000000):无操作指令。用于在命令间提供延迟,满足内部状态机转换或寄存器写入的时间要求。工具自动插入,确保时序合规。用户通常无需关心,但在手动构造或分析比特流时需识别。

②TIMER寄存器:设置看门狗定时器初值。如果配置时间超过此定时器值,会触发Fallback。用于系统可靠性要求高的场合,防止因配置源故障导致FPGA永久挂死在配置状态。

③WBSTAR (Warm Boot Start Address) 寄存器:存储MultiBoot的备用启动地址。实现黄金映像回退或多种应用映像切换。当主映像损坏或通过用户命令触发时,FPGA从此地址加载备用比特流。

④CMD寄存器:发送配置命令。如RCRC(复位CRC计算器)、SWITCH(切换CCLK频率)、START(启动启动序列)等。SWITCH命令用于在比特流加载过程中从低速初始CCLK切换到高速CCLK,以缩短总配置时间。

⑤COR0/COR1 (Configuration Option Registers):COR0设置核心选项,如启动时钟源(CCLK/UserClk)、CCLK频率(ConfigRate)、启动阶段顺序、是否使能Persist模式等。COR1设置更多选项,如是否使能配置后CRC检查(POST_CRC)、BPI闪存的页模式参数等。用户最常通过BitGen/Vivado选项修改的部分。例如,选择更快的ConfigRate以加速配置,或使能POST_CRC以进行SEU检测。

⑥IDCODE寄存器写入与检查:比特流中包含目标FPGA的IDCODE。配置逻辑会将其与芯片硅片内的ID进行比较。

⑦控制寄存器写入 (CTL0/CTL1 with MASK):CTL0寄存器控制关键行为,如是否使能比特流加密(Decrypt)、读保护(Readback)、Fallback使能。MASK寄存器用于在写入时保护某些位(只更新MASK中为1的对应位)。如设置CTL0的DEC位以启用AES解密。

3)核心配置数据加载 (Core Configuration Data Load)

①帧地址寄存器设置 (FAR, Frame Address Register):指定接下来要写入的配置帧的起始地址。配置内存按帧组织,FAR用于寻址。这是部分重配置(Partial Reconfiguration)的基础。通过改变FAR并发送新的帧数据,可以动态修改FPGA的特定区域,而不影响其他部分。

②写配置数据命令 (WCFG Command):告诉配置逻辑,接下来的数据是实际的配置帧数据,准备开始写入。

4)校验、启动、清理 (Verification, Startup, and Cleanup)

①CRC校验值写入:比特流末尾包含一个根据之前所有配置数据(从RCRC命令后开始)计算出的32位CRC值。FPGA将自己计算的结果与此值比较。

②启动序列触发命令:GRESTORE全局复位恢复,用于某些特定配置上下文恢复。START正式启动FPGA,此命令使配置状态机进入启动序列(启动时钟、释放DONE、撤销GTS、断言GWE等)。

③去同步命令 (DESYNCH):使配置逻辑脱离同步状态,清空内部数据对齐状态机。为后续的配置操作做准备。例如,在MultiBoot链中,一个FPGA配置完成后,其DOUT引脚输出的数据需要被下游FPGA识别。DESYNCH确保上游FPGA的配置接口不会干扰下游的同步字识别。它也标志着一个完整配置会话的结束。

配置寄存器

a)CRC Register (00000):对此寄存器的写入操作用于执行比特流数据的CRC校验。如果写入的值与当前计算的CRC值匹配,则CRC_ERROR标志被清除,并允许启动序列继续进行。

b)Frame Address Register (00001)

1)7系列器件分为上、下两个部分。所有帧的长度固定且相同,均为3,232比特(即101个32位字)。

2)帧地址寄存器分为五个字段:块类型、上/下半区位、行地址、列地址、次地址。地址可以直接写入,也可以在每帧结束时自动递增。典型的比特流从0开始,自动递增至最终计数值。

c)FDRI Register (00010)/FDRO Register (00011)

1)FDRI是帧数据输入寄存器。向此寄存器写入数据,可将配置帧数据写入到FAR寄存器所指定的帧地址处。

2)FDRO是帧数据输出寄存器。此只读寄存器提供回读数据,用于读取从FAR寄存器指定地址开始的配置帧。

d)Command Register (00100)

1)命令寄存器用于指示配置控制逻辑触发全局信号并执行其他配置功能。每次向FAR寄存器加载新值时,CMD寄存器中当前存在的命令都会被执行。

2)命令寄存器代码

①WCFG:00001,写配置数据,在向FDRI写入配置数据之前使用。

②MFW:00010,多帧写,用于将单帧数据写入到多个帧地址。

③DGHIGH/LFRM:00011,末帧,撤销GHIGH_B信号,激活所有互连。GHIGH_B信号由AGHIGH命令断言(置为有效)。

④RCFG:00100,读配置数据,在从FDRO读取配置数据之前使用。

⑤START:00101,开始启动序列,在成功执行CRC校验和DESYNC命令后,启动序列开始。

⑥RCAP:00110, 复位CAPTURE信号,在单次触发模式中执行回读捕获后,复位CAPTURE信号。

⑦RCRC:00111,复位CRC,复位CRC寄存器。

⑧AGHIGH:01000,断言GHIGH_B信号,将所有互连置于高阻态,以防止写入新配置数据时发生冲突。此命令仅用于关机重配置。互连通过LFRM命令重新激活。

⑨SWITCH:01001,切换CCLK频率,将主CCLK的频率更新为COR0寄存器中OSCFSEL位指定的值。

⑩GRESTORE:01010,脉冲GRESTORE信号,根据用户配置,对IOB和CLB触发器进行置位/复位。

①SHUTDOWN:01011,开始关机序列,启动关机序列,完成后禁用器件。关机操作在下一次成功的CRC校验或RCRC指令(通常是RCRC指令)时激活。

②GCAPTURE:01100,脉冲GCAPTURE,用当前寄存器状态加载捕获单元。

③DESYNC:01101,复位DALIGN信号,在配置结束时使用,用于使器件去同步。去同步后,配置数据引脚上的所有值都将被忽略。

④IPROG:01111,内部PROG,用于触发热启动。

⑤CRCC:10000,(当选择回读CRC时) 重配置后,配置逻辑重新计算第一个回读CRC值。切换GHIGH具有相同效果。当重配置期间未切换GHIGH时,可使用此命令。

⑥LTIMER:10001,重载看门狗定时器。

⑦BSPI_READ:10010,BPI/SPI重新启动比特流读取。

⑧FALL_EDGE:10011,切换到负边沿时钟,将配置数据捕获的时钟沿改为下降沿。

e)Control Register 0 (00101)

1)控制寄存器0(Control Register 0, COR0)是一个关键的配置选项寄存器。写入该寄存器的值用于控制多项配置行为,主要包括:配置时钟选项(例如,切换至外部主配置时钟EMCCLK,以及通过ConfigRate选项设置内部主CCLK的频率)、启动阶段配置(如等待DCI匹配或MMCM锁定),以及安全设置(例如使能HMAC身份验证)。

2)控制寄存器0用于配置 7 系列器件。对CTL0寄存器的写入操作受MASK寄存器中的值屏蔽(这允许在无需重新指定SBITS和PERSIST位的情况下切换GTS_USR_B信号)。

3)

①EFUSE_KEY:选择AES密钥源,0表示电池备份RAM (默认);1表示eFUSE。此位在DEC位被设置时会再次被内部锁存。此后,为防止密钥源切换,此位不可更改,尽管它仍可被读写。

②ICAP_SELECT:ICAPE2端口选择。0启用顶部ICAPE2端口 (默认);1启用底部ICAPE2端口。

③OverTempPowerDown:启用XADC过温关断功能。0禁用过温关断 (默认);1启用过温关断。

④ConfigFallback:配置失败时停止,并禁用回退到默认比特流。 对应的比特流选项是ConfigFallback:Enable/Disable。0启用回退;1禁用回退 (默认)。

⑤GLUTMASK_B:全局LUT屏蔽信号。 屏蔽任何可更改存储单元的回读值。1不屏蔽可更改存储单元(如分布式RAM或SRL)的回读值;

0屏蔽可更改存储单元的回读值 (默认)。

⑥FARSRC:决定FAR[23:0]配置寄存器的输出源。0输出EFAR,即ECC错误帧的地址。1输出FAR,即RBCRC的地址 (默认)。

⑦DEC:AES解密器使能位。

⑧SBITS[1:0]:安全级别。 7 系列FPGA的安全级别已扩展至加密比特流。此设置适用于配置端口,而非ICAPE2。安全级别在加密比特流结束时,或对于未加密比特流则在EOS(启动结束)后生效。

⑨PERSIST:由M2:M0定义的配置接口在配置结束后保持有效。 通常仅与SelectMAP接口一起使用,以允许重配置和回读。

⑩GTS_USR_B:低有效全局I/O三态控制。 如果GTS_CFG_B也有效,则同时关闭上拉电阻。

f)Status Register (00111)

1)

①BUS_WIDTH:配置总线宽度自动检测结果。 对于BPI和SelectMAP模式,在模式引脚被采样后、总线宽度检测完成前,该值被设为01 (x8)。如果启用了ICAPE2,此字段在配置完成后反映ICAPE2的总线宽度。

②STARTUP_STATE:配置启动状态机状态。

③XADC_OVER_TEMP:XADC过温报警。

④DEC_ERROR:在解密操作之前或之后尝试写入FDRI。

⑤ID_ERROR:尝试在未成功进行DEVICE_ID检查的情况下写入FDRI。

⑥DONE:DONE引脚上的电平值。

⑦RELEASE_DONE:内部DONE信号的值。

⑧INIT_B:INIT_B引脚上的电平值。

⑨INIT_COMPLETE:表示初始化已完成的内容信号。

⑩MODE:模式引脚 (M[2:0]) 的状态。

①GHIGH_B:GHIGH_B的状态。

②GWE:GWE的状态。

③GTS_CFG_B:GTS_CFG_B的状态。

④EOS:来自启动模块的启动结束信号。

⑤DCI_MATCH

⑥MMCM_LOCK

⑦PART_SECURED

⑧CRC_ERROR

g)Configuration Options Register 0 (01001)

1)PWRDWN_STAT:将DONE引脚功能改为掉电状态指示引脚。

2)DONE_PIPE

3)DRIVE_DONE:DONE引脚驱动模式:0表示DONE引脚为开漏输出 (默认); 1表示DONE引脚被主动驱动为高电平 (不推荐)。

4)SINGLE:回读模式设置: 0表示非单次回读模式,每次在CAPTUREE2原语上触发CAP信号时,都会加载新的捕获值,也可以通过 CMD寄存器中的GCAPTURE指令执行捕获; 1表示单次回读模式,在连续两次回读操作之间,必须在CMD寄存器中加载RCAP指令。

5)OSCFSEL:在主模式下选择CCLK频率 (范围:2MHz -- 60MHz)。

6)SSCLKSRC:启动序列时钟源选择。

7)DONE_CYCLE/MATCH_CYCLE/LOCK_CYCLE/GTS_CYCLE/GWE_CYCLE。