文章目录

1.上电配置流程

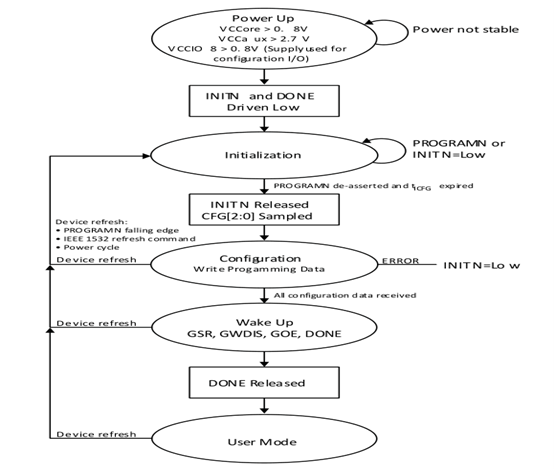

LatticeECP3上电配置流程按照先后顺序分为Power On、Initialization、configuration Mode、User Mode(或者叫Function mode)四个阶段。 如图所示,首先要等待电源就绪,内部会有POR(Power on reset)电路监测电压,当监测到V CCcore > 0.8 V;V CCaux > 2.7 V;V CCIO8 > 0.8 V这三个条件都满足的时候,会将initn信号拉低,指示从power on sequence进入initialization阶段。在initialization阶段,FPGA将会清除所有的SRAM memory,经过tICFG时间之后,Initn上升沿就标志着进入configuration阶段。tICFG时间在datasheet中定义,master mode最大23ms,slave mode最大6ms。Initn拉低指示当前正在clear all of the SRAM Memory,还有另一个作用是作为输入禁止从initialization状态到configuration状态。Configuration状态将开始根据配置管脚CFG[2:0]决定从哪里读取数据,在配置阶段如何initn出现下降沿,说明配置过程出错,如果是multiboot模式,有可能回退指安全区。当所有配置数据正确接收之后,DONE信号拉高,标志着从配置阶段进入User mode阶段,有一个叫做wake-up描述这个过程,唤醒(Wake-up)指的是 FPGA bit流加载完毕, 从配置模式进入功能模式 的过程。当器件正确接收到 全部配置数据 后,唤醒过程开始,该过程要做以下四件事,①拉高done,如果有外部器件把 DONE 引脚保持为低电平,那么 LatticeECP3 的唤醒过程不会继续。②Global Output Enable(GOE),FPGA 的 所有 I/O 输出端口 会离开高阻状态,开始执行它们在配置中设定的输出功能。Assign的组合逻辑就是这时候开始操作的;③GSR 是一个内部控制脉冲。当它被assert时,会对以下带有 "GSR 使能属性" 的元件进行 置位/清零(Set/Clear)④Global Write Disable(GWDIS)是一个控制信号,用来 屏蔽 FPGA 内所有 RAM 的写使能。之后进入user mode之后标志FPGA进入复位释放过程。

2.三个配置引脚

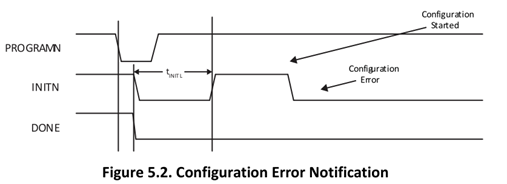

Initn引脚 是低电平有效的双向专用引脚。其功能和作用如下①在上电或者programn使能之后或者Jtag、SSPI收到refresh指令之后,initn会拉低表示正在initialization阶段,正在SRAM清除。②当tICFG时间之后,INITn 会释放(即变为高电平),表示 FPGA 已准备好接收配置数据。FPGA 会 采样 CFG[2:0] 输入引脚,以决定具体的配置方式,在 Master 模式 下,FPGA 会开始从外接非易失性存储器读取配置位流。在 Slave 模式 下,FPGA 会等待通过 CFG[2:0] 所选接口传来的配置数据。③在Initn拉高之前,外部器件可以将 INITn 拉低,以阻止 FPGA 开始读取配置数据。其应用是多个FPGA同时启动时,可以将所有的Initn信号线与在一起,这样会等待最后拉高initn的设备同步进入配置过程。④如图所示,在配置阶段,如果检测到错误,会通过拉低 INITn 来报告错误。

DONE引脚 是一个专用双向引脚,并带有内部弱上拉,有两个作用,首先作为输出,指示FPGA进入用户模式(User Mode)。其次作为输入,与DONE_EX属性共同发挥作用(在spreadsheet view界面的sysconfig处配置)。默认情况下DONE_EX为OFF,此时外部拉低done不起作用,done信号用作输出指示进入user mode。设置DONE_EX==ON时,外部设备拉低done信号以延迟进入用户模式。这么做解决一个问题是,多个FPGA链式配置时希望同步启动,如果有FPGA先启动,则SPI时钟将不在起作用,后续节点可能无法完成配置,因此需要确保DONE为低,直到所有 FPGA 完成配置。此外,Done拉低的时隙与Initn拉低时隙一致。

Programn引脚,下降沿敏感,用于推出用户模式进入配置模式,可以理解为是让bit重新加载FPGA的使能信号。PROGRAMn是FPGA的一个异步、低有效输入引脚(active low),其低电平保持时间必须满足最小脉宽tPRGM。它的功能就是让FPGA重新进入初始化(Initialization)状态,也就是清空配置单元,准备重新加载 bitstream。当flash中的固件升级完成后,可以拉低该引脚完成系统重启,完成重启之后要再次拉高,配置流程才能离开Initialization状态,开始接收配置数据。

3.FPGA启动速度

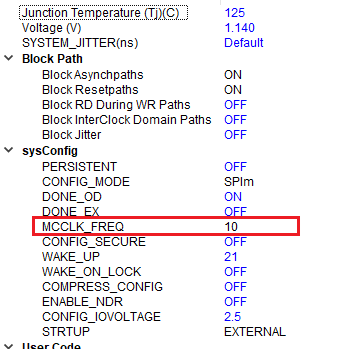

当使用SPI Master模式启动时,从上电到done拉高的时间可理解为启动时间,该时间与SPI的时钟速度息息相关。测量flash上时钟管脚,根据其频率结合bit流的大小可大致计算done拉高的时间,与示波器看到的done时间应该一致才对。在对启动时间有要求的系统里,可以通过配置SPI的速率让FPGA相对快速启动。 默认的Master Clock Frequency是2.5 MHz,以通过Diamond软件的Spreadsheet View工具设置 MCCLK_FREQ全局参数来更改主时钟频率。但需要注意,要同时满足频率值在Flash支持的范围之内。如图所示,执行配置的时候勾选到更改频率之后,要键入enter确认,然后spreadsheet view提示待保存的星,点击保存,否则不起作用。

4.传送门

|-----|

| END |

📡文章原创,首发于CSDN论坛。

📡欢迎点赞♥♥收藏⭐⭐打赏💵💵!

📡欢迎评论区或私信指出错误💉,提出宝贵意见或疑问😱。