目录

[一. 实验内容](#一. 实验内容)

[二. 实验步骤](#二. 实验步骤)

[三. 实现效果](#三. 实现效果)

[四. 实验环境](#四. 实验环境)

[五. 实验小结及思考](#五. 实验小结及思考)

一. 实验内容

设计一个简易的计算器:

在上一个实验当中,你已经成功设计好了一个cpu,在该cpu基础之上,请你利用软硬件协同设计思想,在此基础之上设计一个简单的整数"加,减,乘,除"计算器,对于计算器计算的结果,你需要用七段数码管进行展示。

二. 实验步骤

(1)七段数码管显示模块

在这个简易计算器中,我们最终需要将结果显示七段数码管上面。在这里我们首先需要设计一个译码器,使得输入0~9可以显示在七段数码管上面。

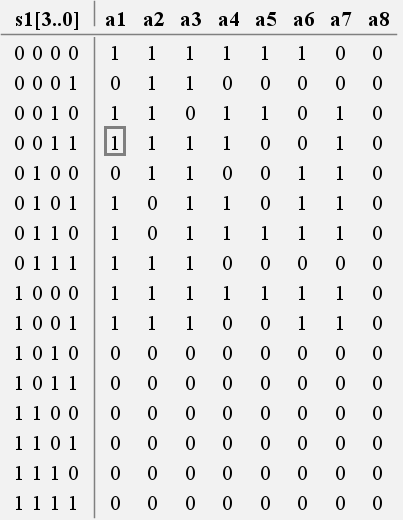

利用一个真值表,输入一个4bit的数,可以表达0~9,并且成功点亮七段数码管8个LED灯的相应LED灯。真值表如下:

(10~15不显示结果)

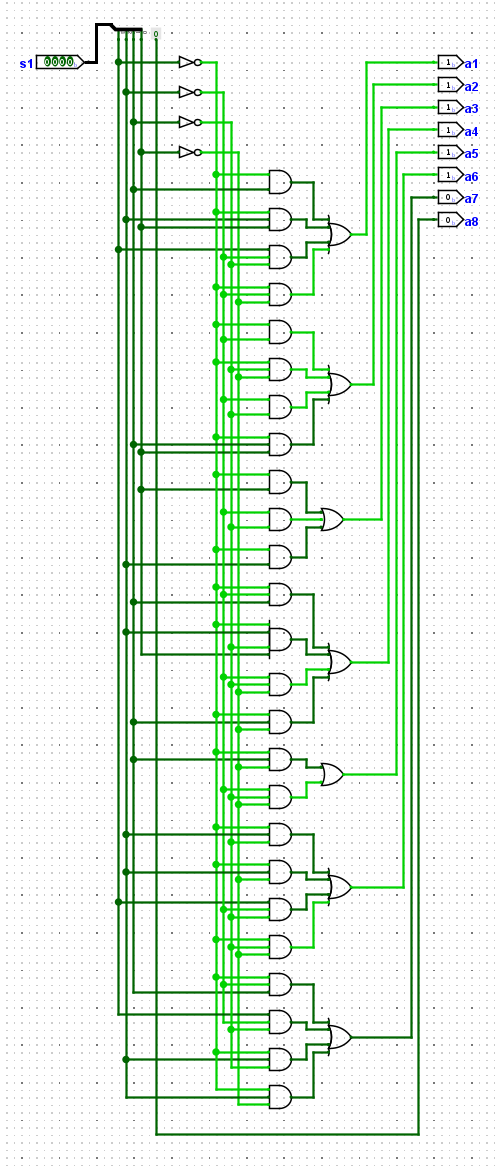

利用如上的真值表,就可以设计出以下电路:

来实现输入对应的0~9可以在数码管上面显示出来。

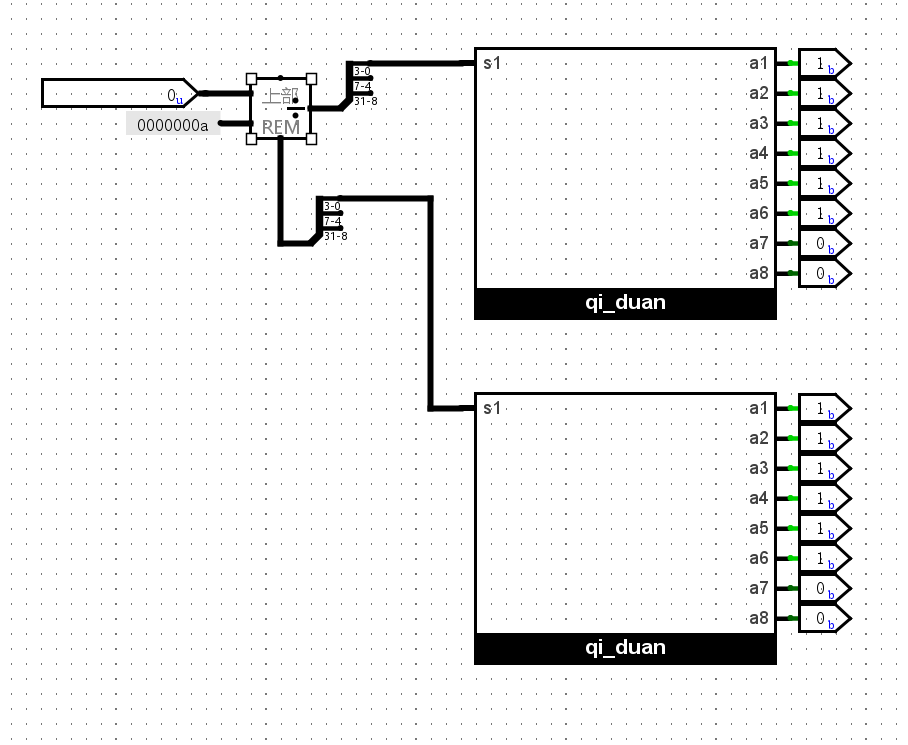

由于输出的结果是16进制的数,且是32bit的,需要转化为两个十进制的数来显示。可以将得到的结果利用分隔线这个运算器来实现除A(10)的操作,把商的低4位给第一个数码管(十位)。把余数的低4位给第二个数码管(个位)。电路连接如下:

**(2)**指令模块

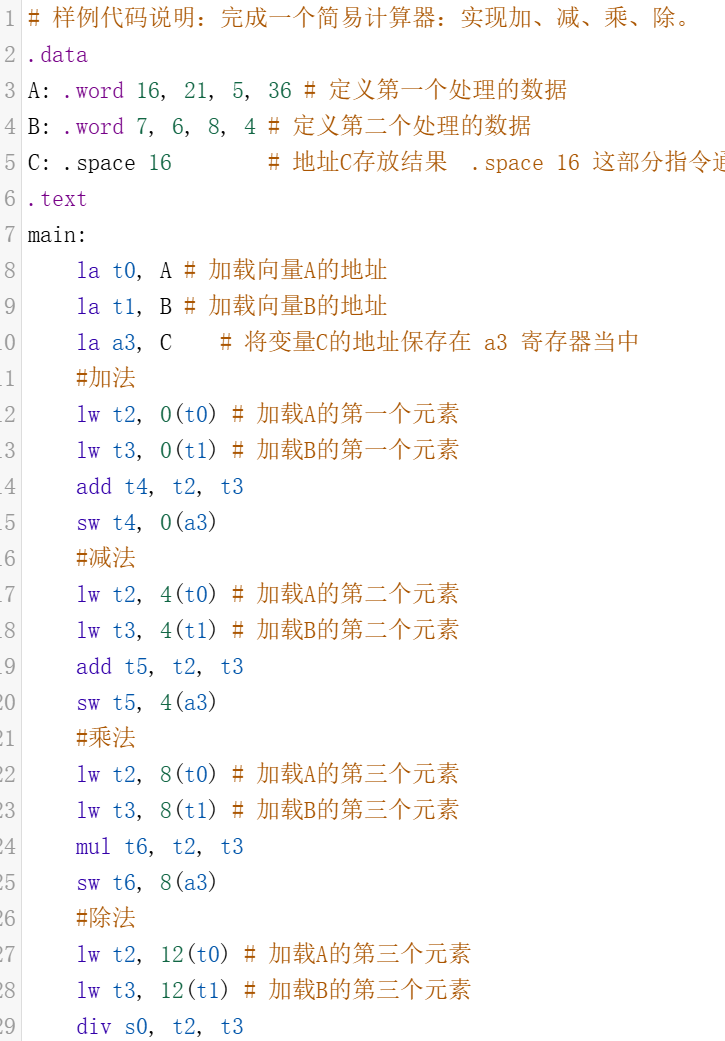

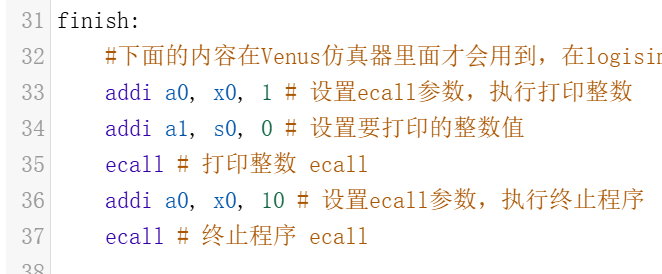

我们需要重新写一段代码,翻译成机器码,存储到ROM中。

以上是在venus仿真器中编写的代码。实现每次从内存中取两个数据,分别进行加减乘除运算后,再把结果写回到内存中的运算。我们将以上代码翻译为机器码后,再复制到CPU的ROM中。

**(3)**控制模块

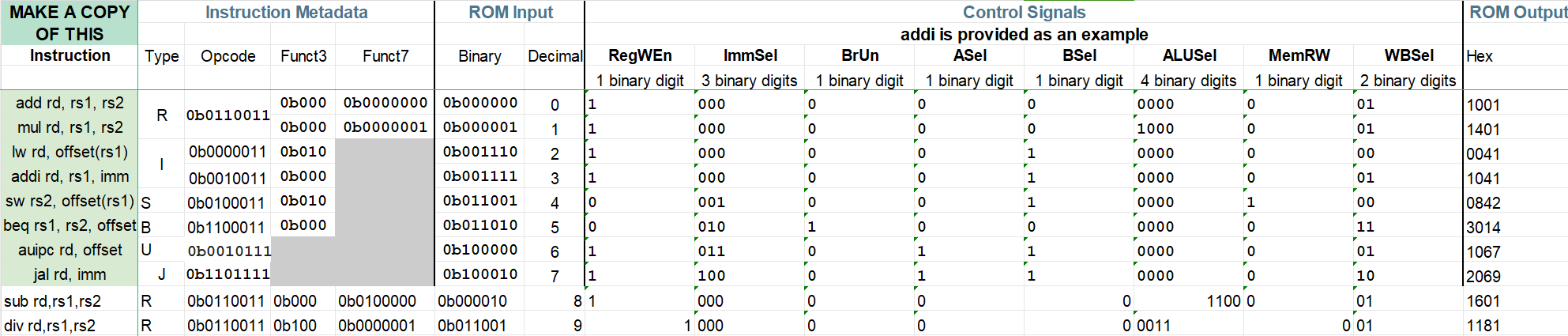

因为在实验二中,并没有用到sub和div这两条指令。所以在这个模块中,我们需要添加这两条指令。查询RISC-V指令集手册,可以补全实现二的表格。如下:

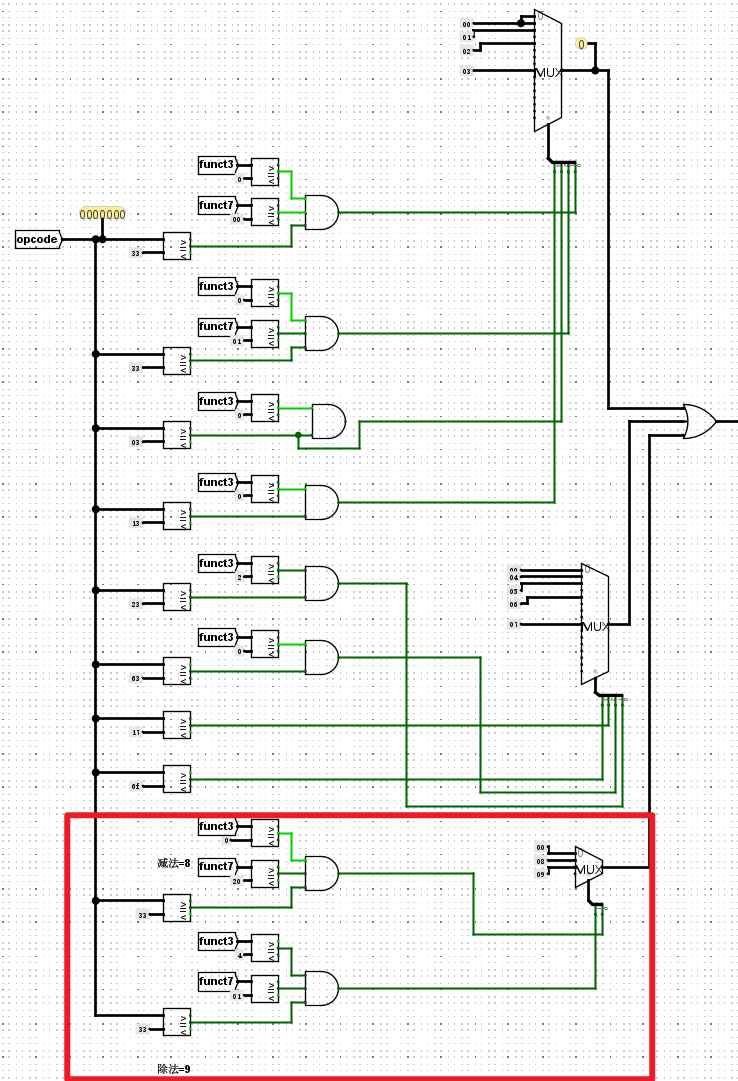

然后需要在control模块中添加这两条模块的识别电路,通过opcode、fun3、fun7来共同实现。再添加一个复用器,选择位设定为2,来控制当识别为sub或div指令的时候,选择ROM中的第8和第9条机器码来识别一些控制信号。电路如下:

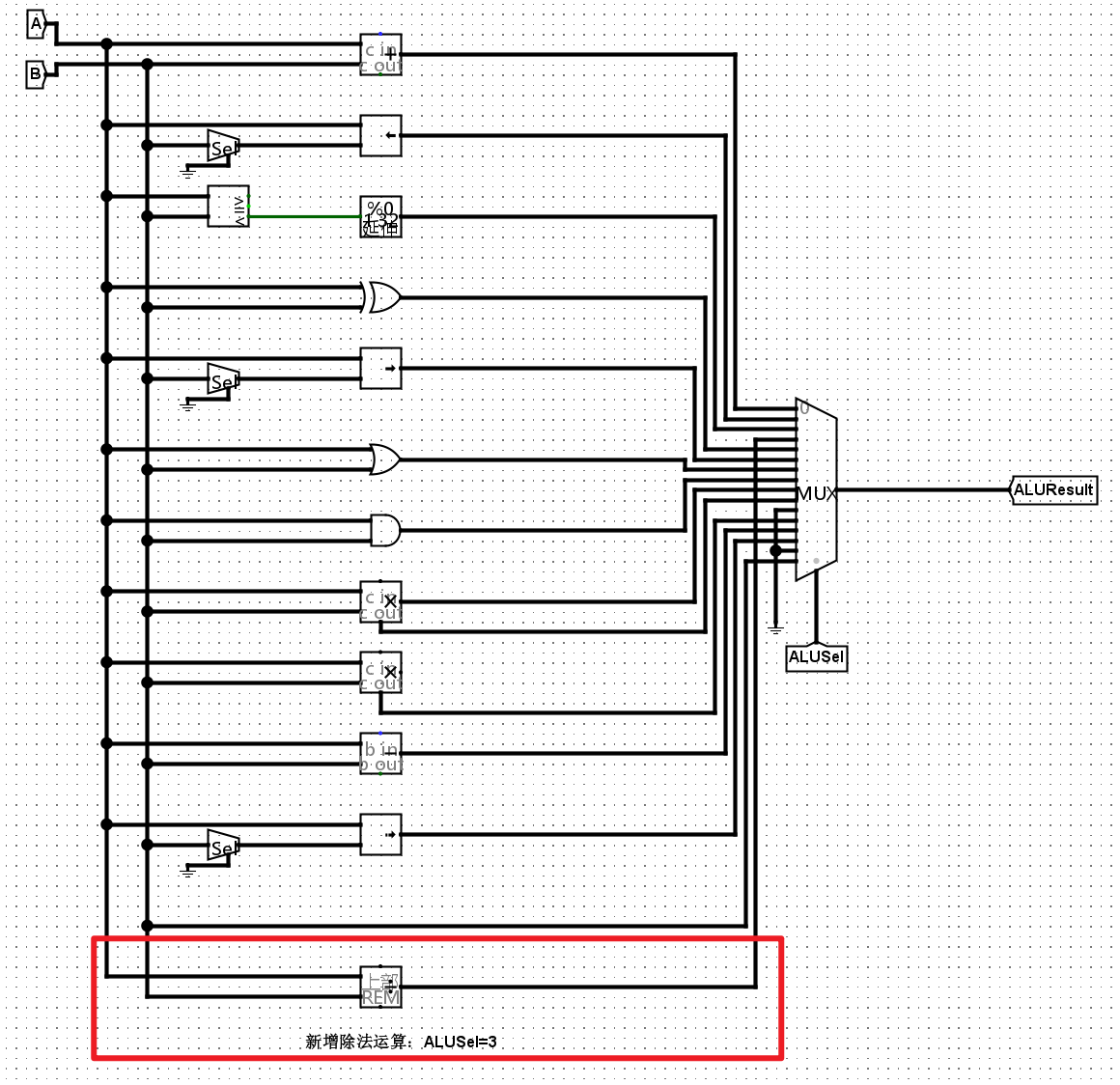

**(4)**ALU模块

在ALU模块中,原本没有除法运算,所以需要添加除法运算的电路模块。在实验二里,AULSel的0011是未使用的,在这里就可以用于除法的使用。利用一个分隔器来实现除法运算,电路如下:

**(5)**CPU模块

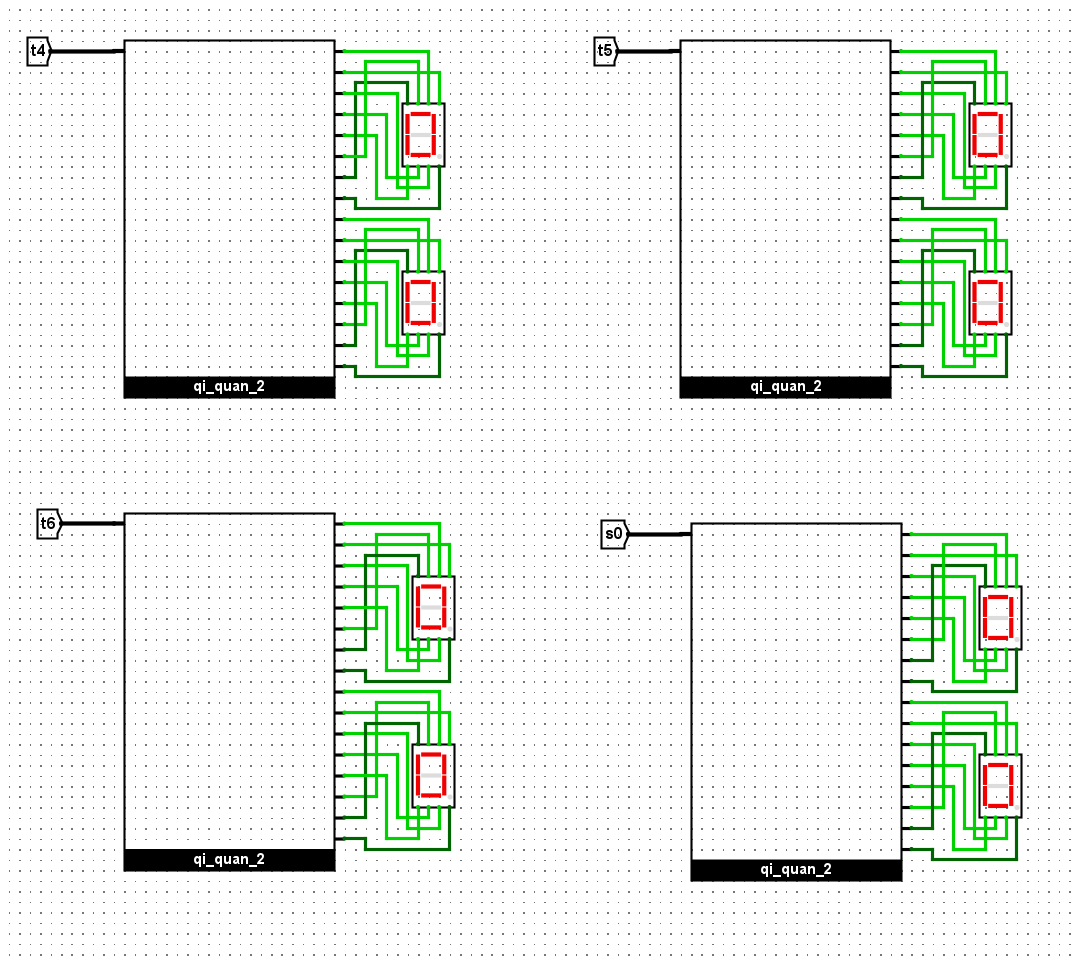

由于将四则运算的结果分别存到t4、t5、t6、s0寄存器里,所以在在CPU中,只需要将对应寄存器的值传输给译码器后,再连接七段数码管即可。电路如下:

三. 实现效果

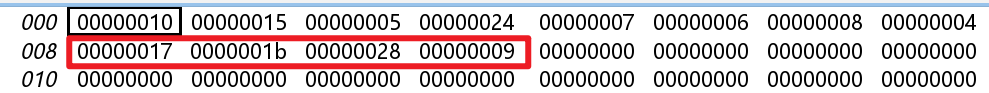

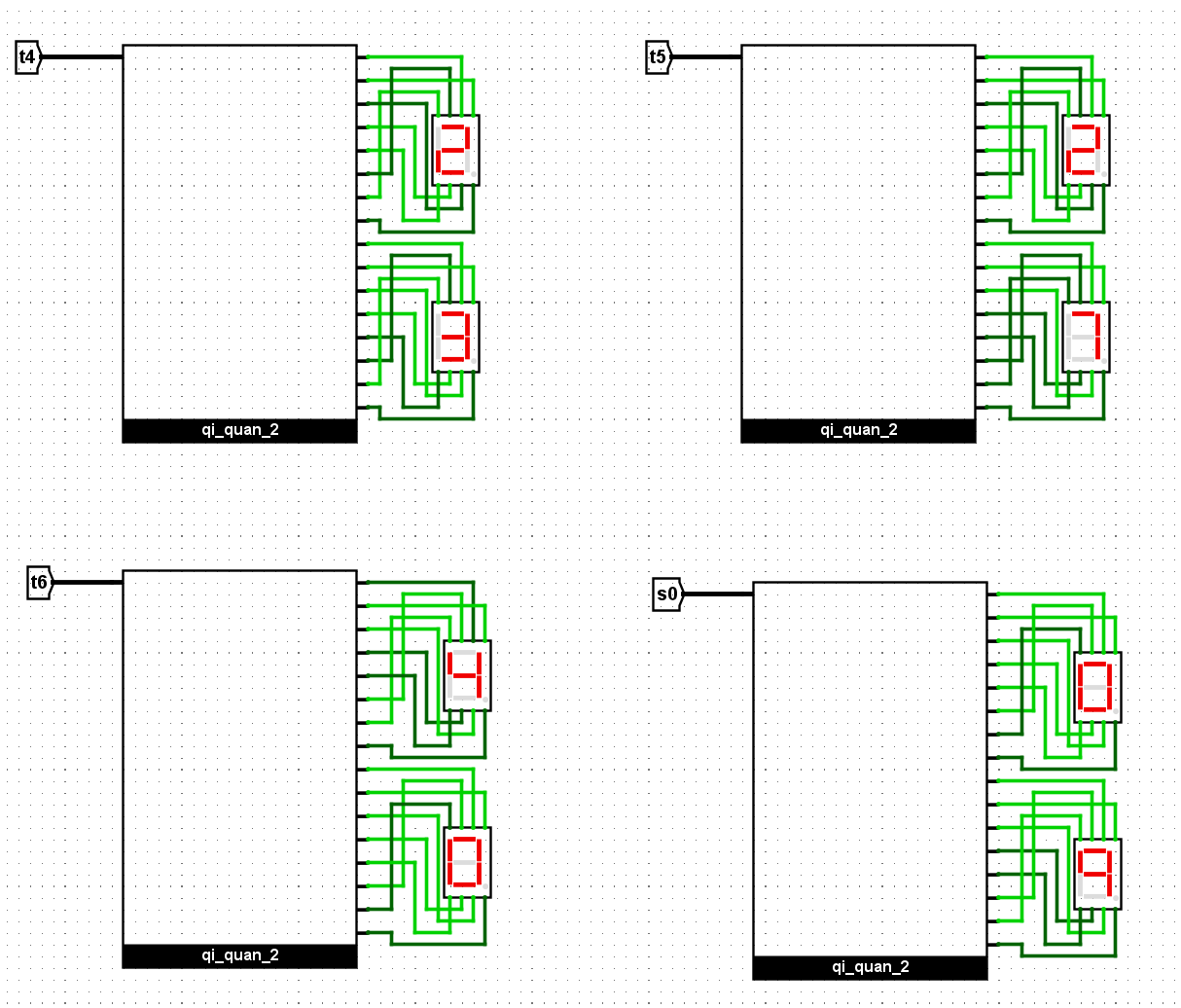

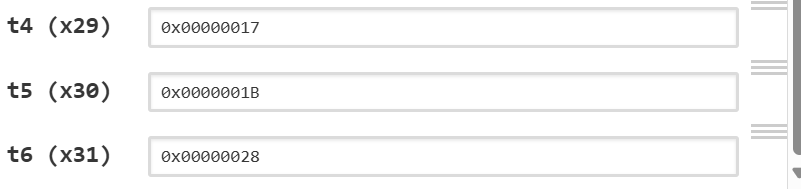

将机器码加载到ROM中,将数据加载到RAM中,开始运行,即可得到如下效果:

在RAM中:

数码管显示:

此结果与venus仿真器中的结果一致:

四. 实验环境

使用Logisim完成RISC-V处理器的设计和调试。

使用Venus仿真器完成测试程序的运行和调试、内存转储(memory dump)。

五. 实验小结及思考

1.了解了ALUSel是什么。

ALUSel信号用于ALU中,选择对应的运算。它的值需要根据我们具体设置的ALU来设定。

2.在汇编语言中懂得了.word 和 .space 是两种常用的伪指令(pseudo-instruction),它们用于在数据段中定义和初始化数据。

.word 用于在内存中定义一个或多个32位(或根据目标处理器架构可能是其他位宽)的整数。

这些整数可以是立即数(即直接给出的数值),也可以是标签(代表另一个内存位置的值,但这在 .word 中不常见,通常用于其他类型的指令或伪指令中)。

.space 用于在内存中分配一定大小的空间,但不初始化这些空间(即这些空间的内容是未定义的,可能是随机的或零,取决于系统的内存管理)。.space 通常需要一个参数,指定要分配的空间大小(以字节为单位)。

3.学会了如何读入外设,以及如何把数据输出到外设中。

可以通过设置使能端和其他控制信号将外设数据输入寄存器文件中和把数据输出到外设中。