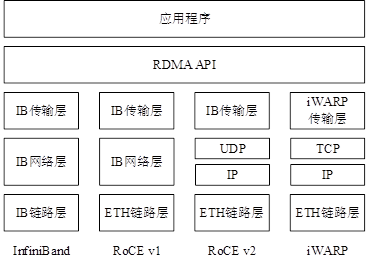

RDMA协议共有四种子协议,分别为InfiniBand、iWARP、RoCE v1和RoCE v2协议。这四种协议使用统一的RDMA API,但在具体的网络层级实现上有所不同,如图1所示,接下来将分别介绍这四种子协议。

图1 RDMA四种子协议网络层级关系图

InfiniBand:InfiniBand是一种专为RDMA设计的网络,其传输层、网络层及链路层均遵循IB协议规范,没有类似以太网的复杂协议交互计算,从硬件级别保证传输可靠,但成本较为高昂,需要使用专用的IB交换机和IB网卡才可以正常路由。

RoCE v1与RoCE v2:RoCE协议即RDMA over Ethernet,其在以太网上承载IB协议,与IB协议具有相同的传输层,仅在网络层和链路层与IB协议存在差异。RoCE协议有v1和v2版本,其中RoCE v1只能部署于二层网络,其报文结构是在原有IB协议报文基础上增加二层以太网报文头,通过ETH Type标识RoCE报文。而RoCE v2基于UDP/IP协议承载RDMA,可部署在三层网络环境下,在原有IB协议报文基础上增加UDP头、IP头和ETH头,通过UDP端口号4791标识RoCE v2报文。使用普通以太网交换机搭配IB网卡即可实现网络路由。

iWARP:iWARP协议是基于TCP/IP协议的RDMA网络,能够工作在任何TCP/IP协议的网络上层,同时将TCP/IP处理流程从CPU卸载到RDMA网卡处理。仅需要使用普通以太网交换机和iWARP网卡即可实现路由。但在大规模部署时,由于TCP/IP协议点对点连接的特性,将会占用大量的内存资源,对系统规格的要求更高

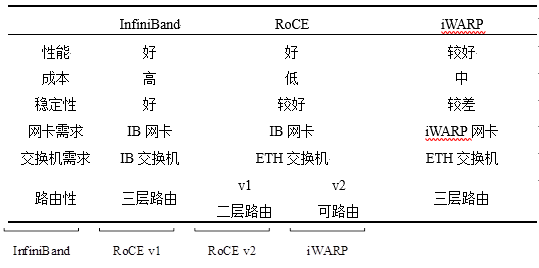

在对比这四种子协议时,将RoCE v1与RoCE v2协议放在一起讨论,RDMA的子协议的比较如表1所示。

表1 RDMA四种子协议的比较

在当今数据中心应用中,综合考虑到成本、性能、硬件需求等因素的前提下,RoCE v2协议正逐渐成为主流RDMA协议。

相关视频感兴趣者,请搜B站用户名: 专注与守望

或链接: