《FPGA经典例程及解读--基于xilinx K325T平台》系列导航

本专栏主要针对与想学习FPGA的同学,从基础的点灯到之后的复杂功能实战例程,从入门到进阶,通过这些例程的学习和了解,希望可以帮助你从一个FPGA小白进阶到FPGA中级阶段,能够处理工作中大多数的FPGA使用场景。

本篇是该系列的第四篇内容

**下一篇:**关注我,第一时间获取更新!!

设计程序参考:FPGA例程(4):按键消抖实验资源-CSDN下载

1 引言

按键的消抖,是指按键在闭合或松开的瞬间伴随着一连串的抖动,这样的抖动将直接影响设计系统的稳定性, 降低响应灵敏度。因此,必须对抖动进行处理,即消除抖动的影响。

实际工程中,有很多消抖方案,如 RS 触发器 消抖,电容充放电消抖,软件消抖。本章利用 FPGA 内部来设计消抖,即采取软件消抖。

按键的机械特性,决定着按键的抖动时间,一般抖动时间在 5ms~10ms。消抖,也意味着,每次在按键闭合或 松开期间,跳过这段抖动时间,再检测按键的状态。只要通过简单的延时就可实现按键的消抖动。

2 硬件环境

开发环境使用vivado2019.1

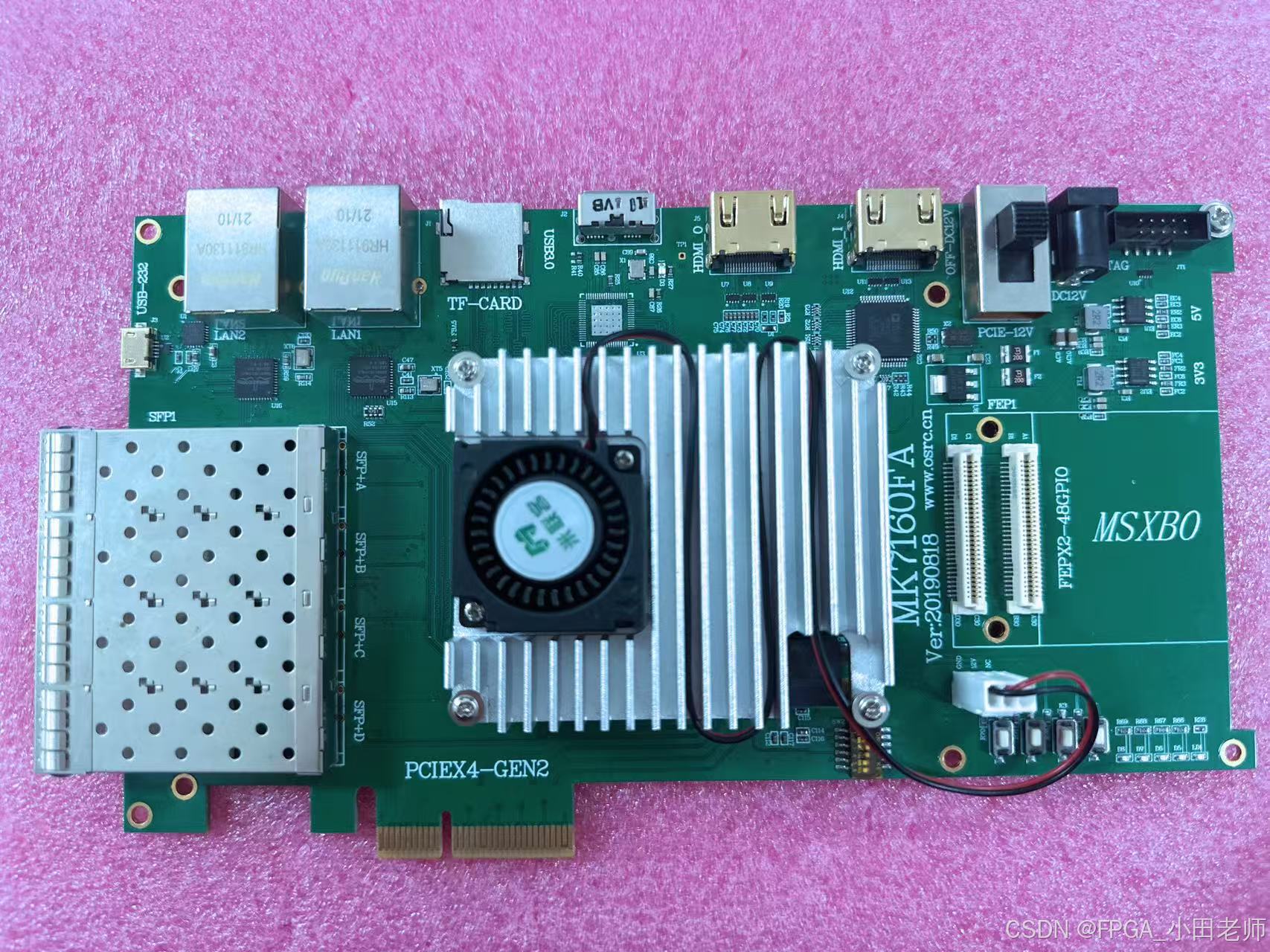

开发板使用米联客的MK7160FA

3 程序实现说明

3.1 未消抖的按键实验

3.1.1 程序设计

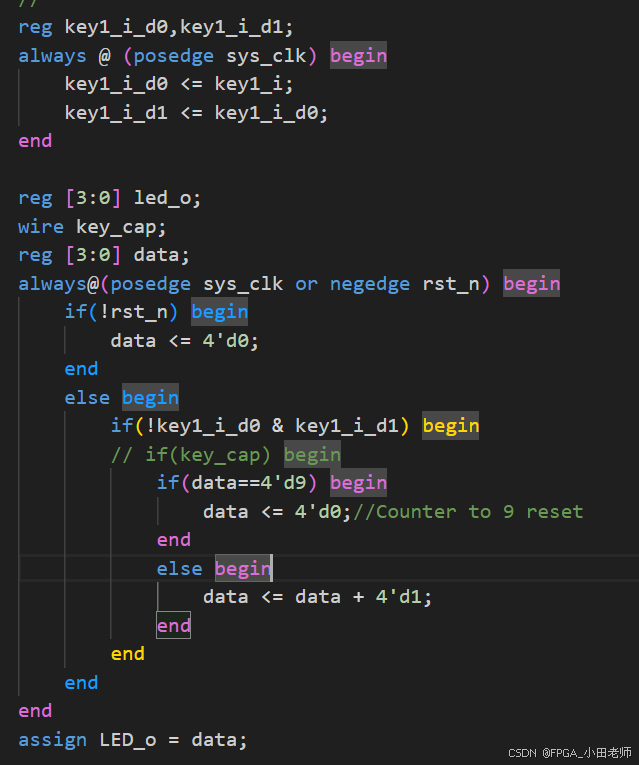

我们先来看这一段程序,程序的功能比较简单

- key1_i是外部输入的按键信号(按钮按下为0,不按为1)

- 先取这个按键的下降沿;

- 当检测到一次这个按键的下降沿的时候,就给data+1

- 随着按键的按下,data[3:0]的值就会从0加到9再到0

- data[3:0]的数值,直接反应到了LED_o(4个LED灯)上

3.1.2 实验结果

我们对程序进行综合实现并下载到板子中,可以看到其结果如下:

我们可以看到4个LED灯,它并没有按照我们预想的那样,按下一次,就增加一个计数值,那样的规律进行闪烁,这是为什么呢?

不消抖的按键

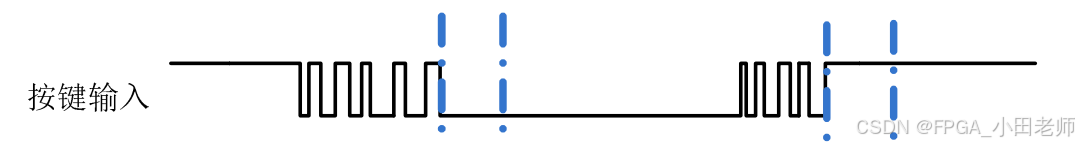

这是因为,按键在按下或松开的时候,按键输入值是又抖动的,无论你按下去的时候多么的平稳,都会存在这个抖动,就像这样子,所以我们必须进行消抖。

3.2 消抖后的按键实验

3.2.1 程序设计

本次消抖使用的方式如下:

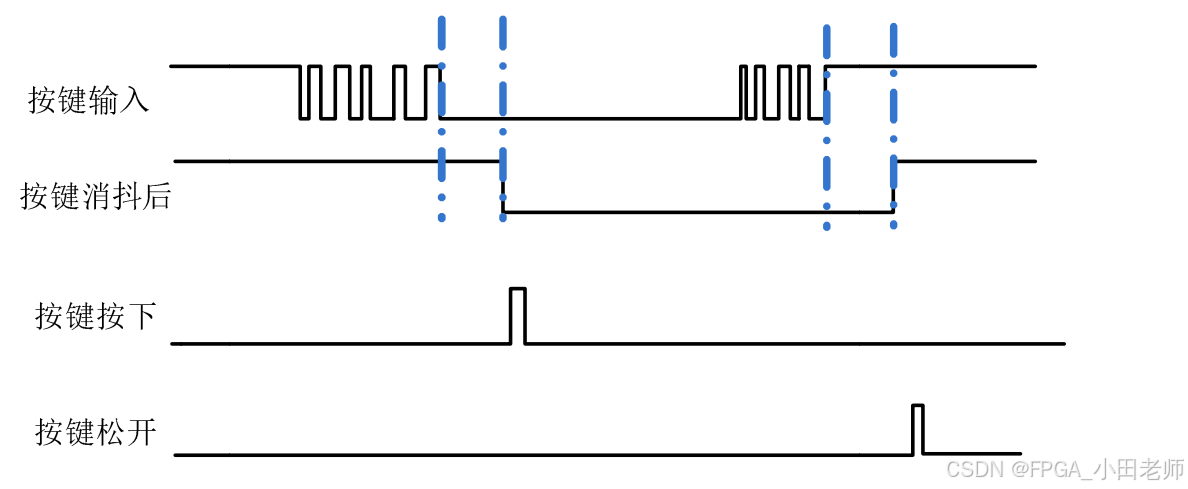

- 设计10ms的消抖时间。

- 在设计的状态机中,分 4 个状态

- KEY_S0:判断按键是否按下,如果是,转移到状态 KEY_S1;

- KEY_S1:10ms 后再次判断按键是否按下,如果是,转移状态到 KEY_S2,否则继续回到 KEY_S0;

- KEY_S2:判断按键是否抬起,如果是,转移状态到 KEY_S3

- KEY_S3:10ms 后再次判断按键是否抬起,如果是,转移状态到 KEY_S0,否则继续回到 KEY_S2;

- 当状态从 KEY_S1 转到 KEY_S2 代表一次按钮按下, key_cap 输出一次高电平。

那咱们去抖之后的按键时序就变成了这样子:

3.2.2 实验结果

我们使用去抖之后的按键信号进行测试:

大家可以看到 消抖之后 随着我们按键按下 data进行了正常的+1操作,我们的LED灯也符合了我们的规律:

消抖之后的按键

4 总结

这样的消抖方式,在实际工作中常被用于CPLD控制CPU启动的初始化时序中,有经验的朋友也能发现,在Aurora IP核的使用中,对于Reset信号的处理官方也是加了4位去抖。