Introduction

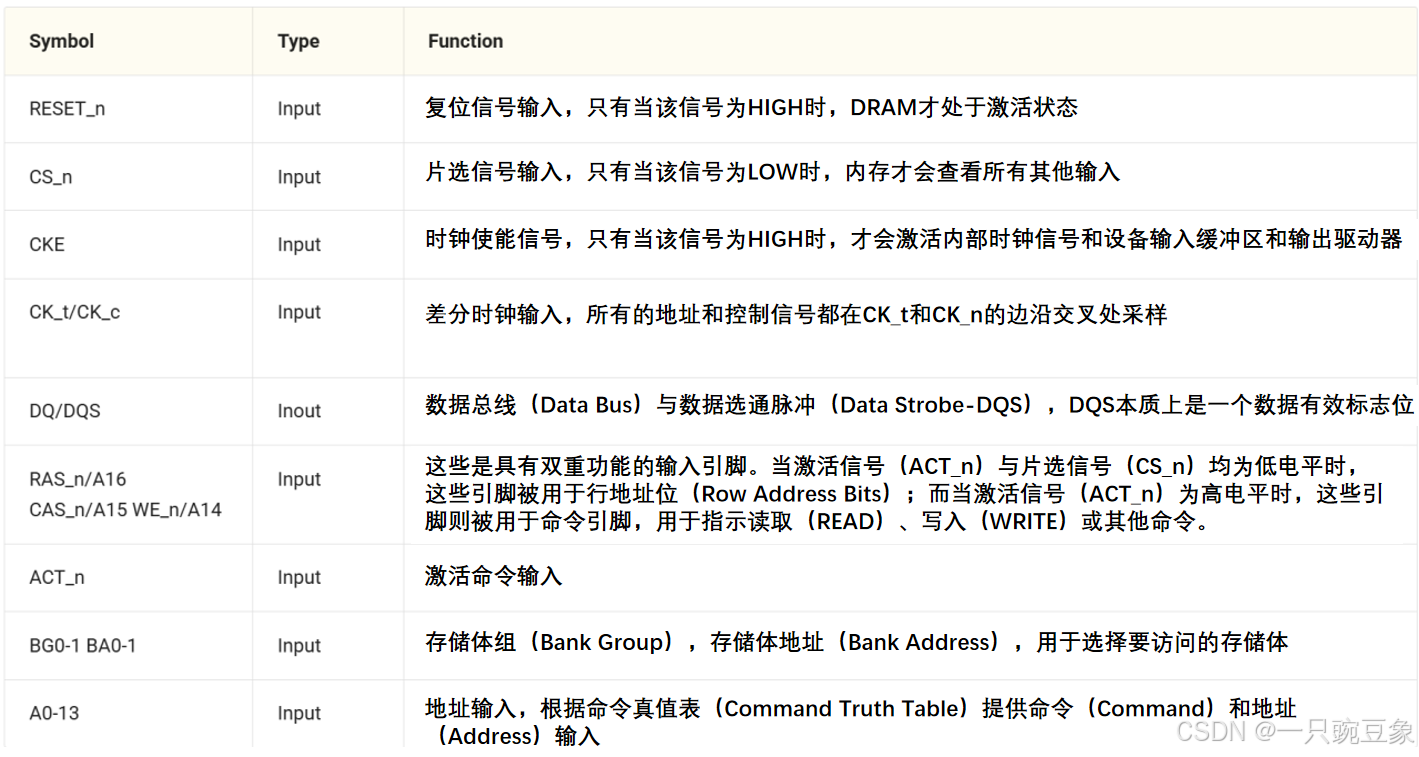

动态随机存取存储器(DRAM)有时钟、复位、片选、地址和数据输入等信号,下表详细介绍了它们的功能:

上述的控制信号会组合形成DRAM工作过程中的各项指令,称之为命令真值表,接下来的内容描述中,会陆续使用到该表中的各种命令术语。

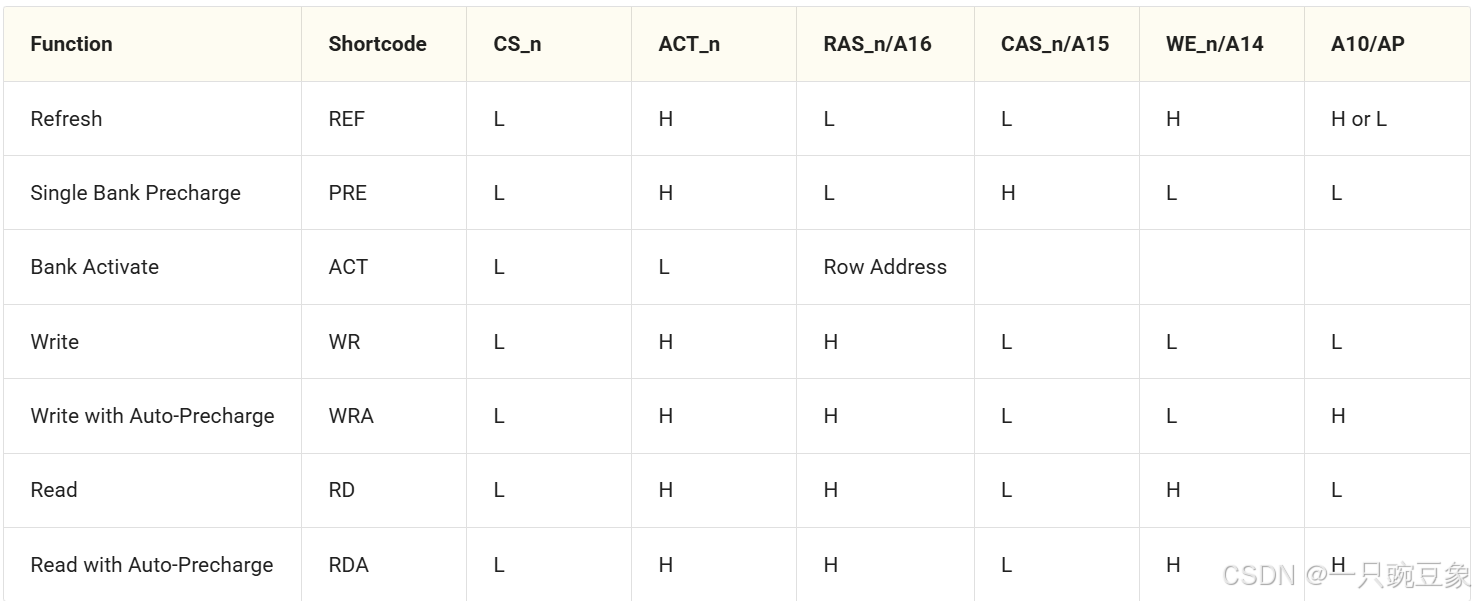

Bank Group, Bank, Row, Column

如图所示是存储器的顶层架构形式,从内存中读取数据时,需要提供一个地址;而向内存写入数据时,除了需要提供地址外,还需提供要写入的数据。用户所提供的这个地址通常被称为"逻辑地址"。在将该逻辑地址呈现给动态随机存取存储器(DRAM)之前,它会先被转换为物理地址。这个物理地址由以下几个字段构成:

- Bank Group

- Bank

- Row

- Column

使用这些单独的字段来确定要读取或写入的内存中的确切位置,用取档案的过程来形容这些物理地址的作用如下:

- 存储体组(Bank Group):用于标识"楼层"编号;

- 存储体地址(Bank Address):用于标识在该"楼层"中,存放所需文件的"文件柜";

- 行地址(Row Address):用于标识文件柜中哪个"抽屉"存放着该文件。将数据读取到感应放大器(Sense Amplifiers)中,就相当于打开\拉出这个文件抽屉;

- 列地址(Column Address):用于标识该抽屉内的"文件编号"。

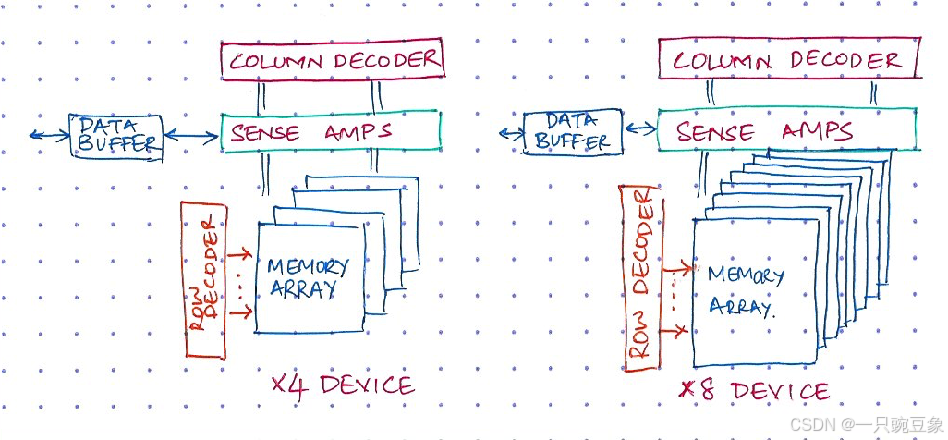

进一步深入探究,每个存储体(Bank)内部会看到以下组件:

- 存储阵列(Memory Arrays)

- 行解码器(Row Decoder)

- 列解码器(Column Decoder)

- 感应放大器(Sense Amplifiers)

一旦确定了存储体组(Bank Group)和具体的存储体(Bank),地址中的行(Row)部分就会激活存储阵列中的一条线。这条被激活的线被称为"字线"(Word Line),激活字线会将数据从存储阵列读取到感应放大器(Sense Amplifiers)组件中。随后,列(Column)地址会读取已加载到感应放大器中的字的一部分,列的宽度被称为"位线"(Bit Line)。

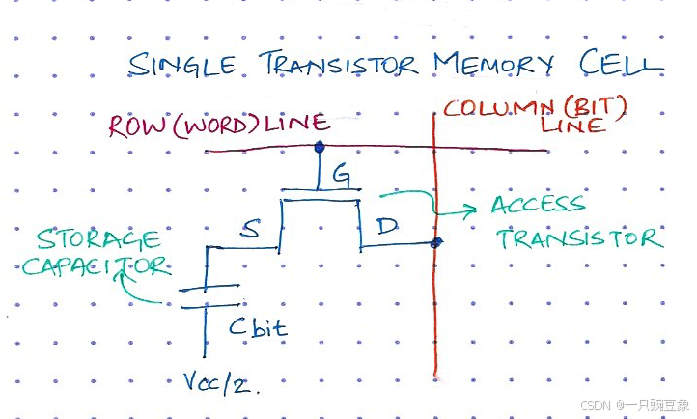

一个比特(bit)本质上是由一个用于存储电荷的电容器(capacitor)和一个充当开关作用的晶体管(transistor)组成的,而一个个晶体管就分布在Word Line和Bit Line所构成的网络中。

DRAM Sizing & Addressing

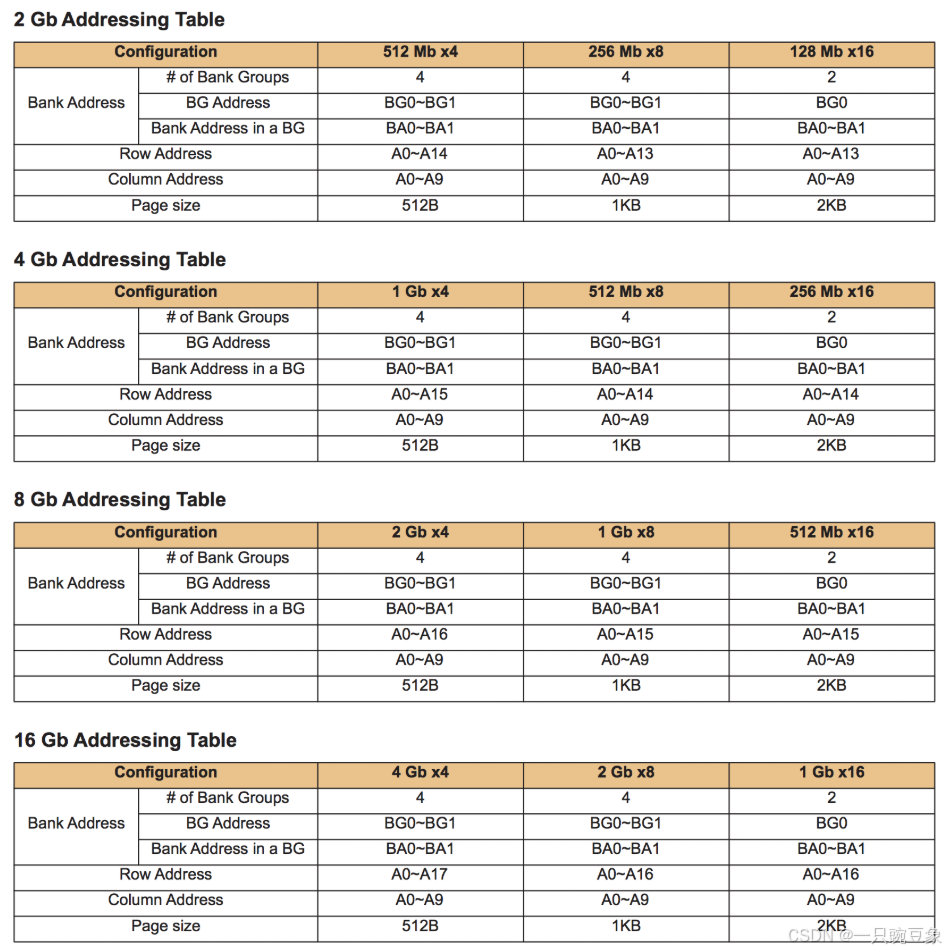

DRAM具有标准化的尺寸规格,这些规格在JEDEC的标准规范中都有明确规定。如下图所示,DRAM的行(ROW)和列(COLUMN)位数会根据其容量大小而变化。例如,8Gb(2Gbx4配置)的DRAM比2Gb(512Mbx4配置)的DRAM具有更多的可寻址内存空间,因此8Gb的DRAM需要17位行地址(A0~A16)来进行寻址,而2Gb的DRAM则仅需15位行地址(A0~A14)。

与行地址(Row address)不同,无论DRAM的容量大小如何,它始终仅具备10位列地址位,即A0~A9。这意味着其列地址空间仅有2^10,即1024列。

页面大小(Page size)本质上是指每行(ROW)所包含的位数。换言之,它就是在激活一行时,被加载到感应放大器(Sense Amplifiers)中的位数。由于列地址(Column address)的宽度是10位,因此每行有1024条位线(Bit Lines)。所以,对于x4设备而言,每行的位数是1024 x 4,即4096bit(或512B)。同理,对于x8设备,每页是1KB;而对于x16设备,每页则是2KB。

清楚上述原理之后,就可以根据DRAM的这些基本参数快速进行容量计算,举例如下:

/* 4Gb x4 Device */

Number of Row Address bits: A0-A15 = 16 bits

Total number of rows = 2^16 = 64K

Number of Column Address bits: A0-A9 = 10 bits

Number of columns per row = 1K

Width of each column = 4 bits

Number of Bank Groups = 4

Number of Banks = 4

Total DRAM Capacity =

Num.Rows x Num.Columns x Width.of.Column x Num.BankGroups x Num.Banks

Total DRAM Capacity =

64K x 1K x 4 x 4 x 4 = 4Gb

/* 4Gb x8 Device */

Number of Row Address bits: A0-A14 = 15 bits

Total number of rows = 2^15 = 32K

Number of Column Address bits: A0-A9 = 10 bits

Number of columns per row = 1K

Width of each column = 8 bits

Number of Bank Groups = 4

Number of Banks = 4

Total DRAM Capacity =

Num.Rows x Num.Columns x Width.of.Column x Num.BankGroups x Num.Banks

Total DRAM Capacity =

32K x 1K x 8 x 4 x 4 = 4Gb

Rank (Depth Cascading)

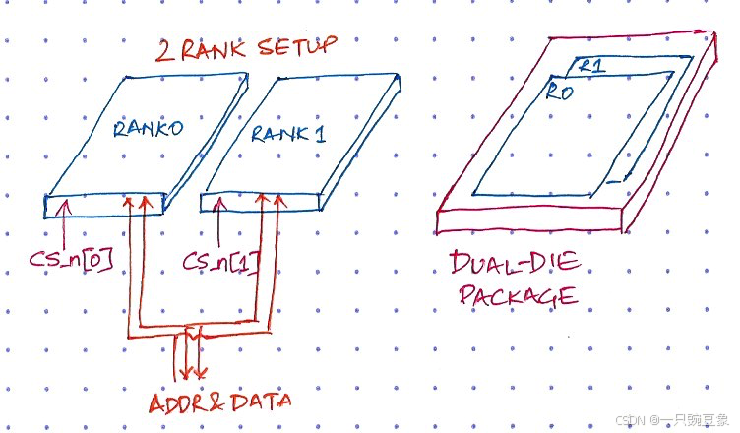

层级(Rank,也称为深度级联,Depth Cascading),在使用DRAM时,用户会遇到诸如单层级(Single-Rank)、双层级(Dual-Rank)或四层级(Quad-Rank)这样的术语。层级是DRAM架构中的最高逻辑单元,它通常被用来增加系统的内存容量。

假设你需要16Gb的内存容量,根据市场上可供选择的产品以及哪种方案成本更低,可以做出的选择如下:

- 使用单个16Gb的内存芯片(Die),此时,将其称为单层级(Single Rank)系统,因为只需要一个CS_n信号来读取内存中的所有内容;

- 选择在PCB上焊接两个独立的8Gb分立器件(因为两个8Gb器件的成本可能比一个16Gb器件更低),此时,这两个器件将连接到相同的地址总线和数据总线,但是,需要两个CS_n信号来分别寻址这两个器件,这种配置被称为双层级(Dual-Rank)系统;

- 选择双芯片封装"(Dual-Die Package, DDP),此时,虽然PCB上只焊接了一个DRAM芯片,但在封装内部,它实际上是由两层芯片(Die)堆叠而成的,每一层芯片会再次共享地址线和数据线,但会拥有各自的CS_n信号,这使得它成为一个双层级(Dual Rank)设备;

- 依此类推,还可能会选择使用四层芯片堆叠的DRAM,即Quad-Rank,但是成本可能会更高。

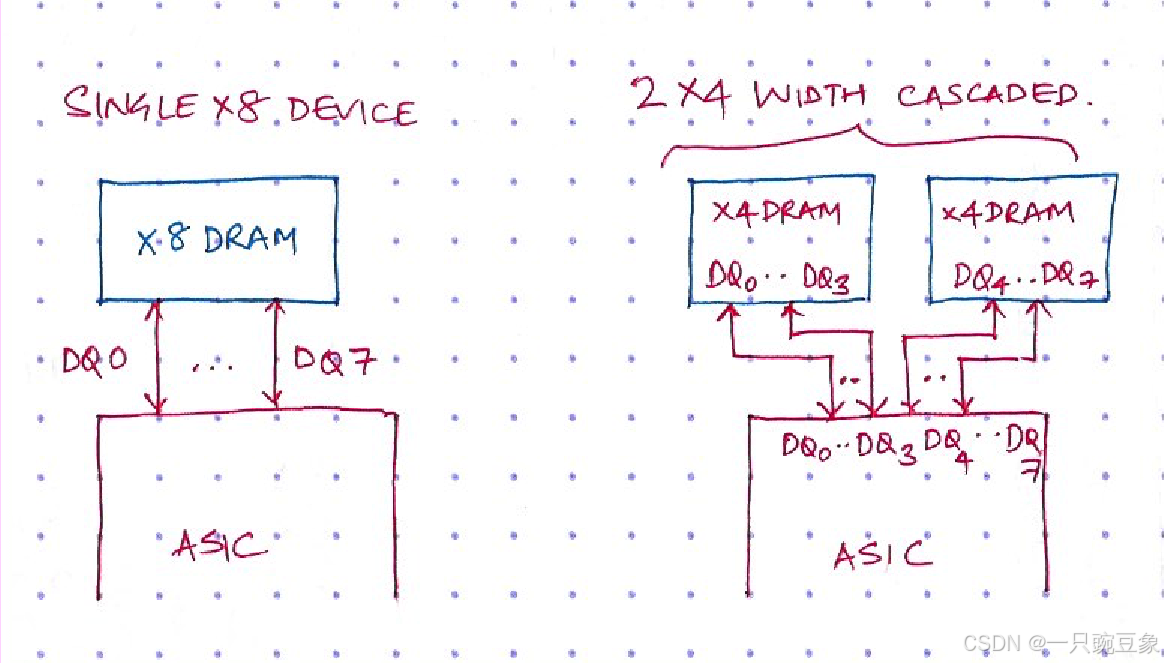

另一个例子,假设用户需要8Gb的内存,且与芯片连接的接口是x8位宽。那么,你可以选择一个单一的8Gb x8设备,或者选择两个4Gb x4设备,并将它们以"位宽级联"(Width Cascaded)的方式连接在PCB上。在位宽级联的配置中,这两个DRAM都连接到相同的CS_n信号、地址总线(Address)和命令总线(Command bus),但它们会使用不同的数据总线(DQ & DQS)。

如下图所示,在4Gb x4设备中,第一个x4 DRAM连接到DQ[3:0],而第二个x4 DRAM则连接到DQ[7:4]。

Accessing Memory

在清楚了DRAM的架构信息后,再来了解下如何访问DRAM地址和进行数据读写操作:

- 对DDR4 SDRAM的读写操作是以突发(Burst)为导向的。操作从用户指定地址所确定的某个选定位置开始,并持续进行突发长度为八个数据周期(burst length of eight)的突发传输,或者进行"截短"的四个数据周期突发传输('chopped' burst of four)。

- 读写操作是一个两步过程。首先执行激活命令(ACT Command),即在时钟周期内将ACT_n和CS_n信号置为低电平,然后,再发出读(Read)或写(Write)命令。

- 与激活命令同时锁存的地址位用于选择要激活的存储体组(Bank Group)、存储体(Bank)和行(Row)(BG0-BG1用于选择存储体组;BA0-BA1用于选择存储体;A0-A17用于选择行)。这一步骤也被称为行地址选通(RAS - Row Address Strobe)。

- 与读或写命令同时锁存的地址位则用于选择突发操作的起始列位置。这一步骤也被称为列地址选通(CAS - Column Address Strobe)。

- 每个存储体(Bank)只有一组感应放大器(Sense Amplifiers)。在对同一存储体中的不同行进行读写操作之前,必须使用预充电命令(Precharge command)将当前打开的行关闭,按照前述"取档案文件"的描述过程,该操作相当于关闭"文件柜"中的当前"抽屉",它会使感应放大器中的数据写回到行中。

- 除了发出显式的预充电命令来关闭一行之外,还可以使用带自动预充电的读命令(RDA,Read with Auto-Precharge)和带自动预充电的写命令(WRA,Write with Auto-Precharge),这些命令会指示DRAM在读写操作完成后自动关闭或预充电该行。由于列地址仅使用地址位A0-A9,因此CAS期间未使用的位A10被重载以指示自动预充。

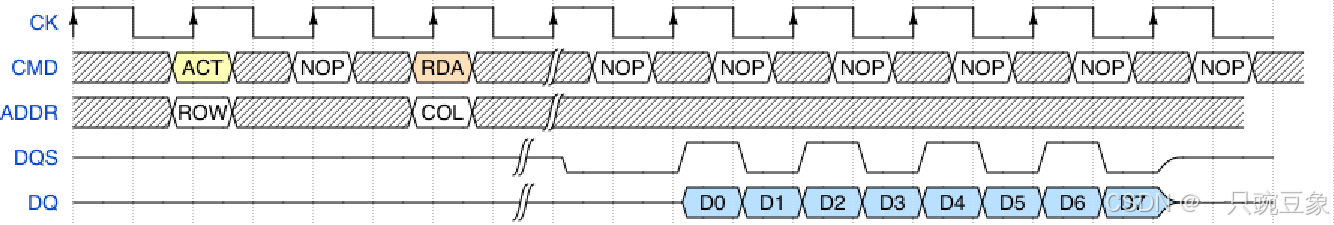

Read Operation

第一步是发出激活(ACT,Activate)命令,此时地址总线上的值表示行地址;

第二步是发出带自动预充电的读命令(RDA,Read with Auto-Precharge),此时地址总线上的值是列地址。

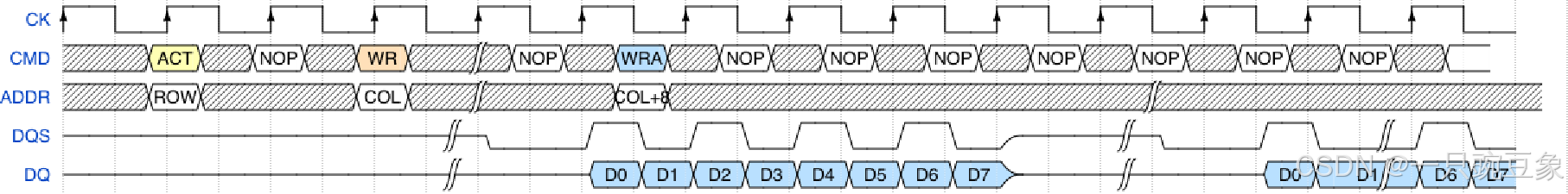

Write Operation

第一步是发出激活(ACT,Activate)命令,此时地址总线上的值表示行地址;

第二步是发出两条写(WRITE)命令,第一条命令(WR)是一个普通的写命令,用于寻址到列地址(COL),并保持该行处于激活状态。第二条命令(WRA)是一个带自动预充电的写命令(Write with Auto-Precharge,简称WRA),用于寻址到列地址加8(COL+8),并且,该命令在写操作完成后会使该行关闭。

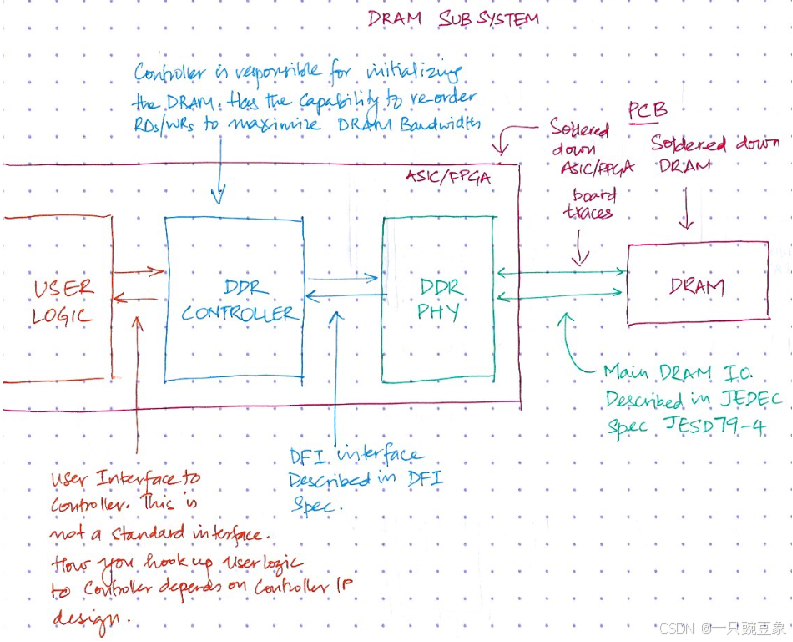

DRAM sub-system

作为一个完整的DRAM系统,它由三个主要组件构成:

- DRAM存储器本身,它包含了上述所有描述的内容;

- 一个DDR物理层接口(DDR PHY);

- 一个DDR控制器(DDR Controller)。

上图中展示的内容相当丰富,下面我们来逐一解析:

- DRAM被焊接在PCB上,而物理层接口和控制器,以及用户逻辑部分,通常都集成在同一个现场可编程门阵列(FPGA)或专用集成电路(ASIC)中;

- 用户逻辑与控制器之间的接口可以由用户自行定义,并不一定要遵循标准。当用户逻辑向控制器发出读或写请求时,它会提供一个逻辑地址;

- 随后,控制器会将这个逻辑地址转换为物理地址,并向物理层接口(PHY)发出相应的命令;

- 控制器和物理层接口之间通过一种称为DFI(DDR PHY Interface,DDR物理层接口)的标准接口进行通信;

- 接着,物理层接口负责所有低层次的信号处理,并驱动与DRAM之间的物理接口。

Summary

最后,将本文探讨的内容总结如下:

- DRAM的组织结构包括存储体组(Bank Groups)、存储体(Bank)、行(Row)和列(Column);

- 用户发出的地址被称为逻辑地址(Logical Address),在将其呈现给内存之前,该逻辑地址会由DRAM控制器转换为物理地址(Physical Address)。DDR4 DRAM根据DQ数据总线的宽度被分类为x4、x8或x16;

- 用户可以通过深度级联(depth cascade)或宽度级联(width cascade)DRAM来达到所需的存储容量;

- 读\写操作是一个两步过程。第一步是激活一行(Row),第二步是对内存进行读取或写入操作;

- DRAM子系统由内存(Memory)、物理层接口(PHY)和控制器(Controller)组成。