定义

低功耗设计被定义为:一系列旨在减少芯片整体动态和静态功耗的技术和方法。

在数字后端设计中,常常会提到PPA,即性能(Perforance),功耗(Power),面积(Area)这三个指标。随着便携式、手持式和电池供电设备中广泛普及,功耗在评价芯片优劣时所占的比重越来越高,低功耗设计也成为了很多芯片设计时的必经之路。

那么低功耗设计中又有哪些常用方法呢?在回答这个问题之前,先来简单介绍一下芯片中功耗分析的方式,以及芯片中各部分所占功耗的比例。

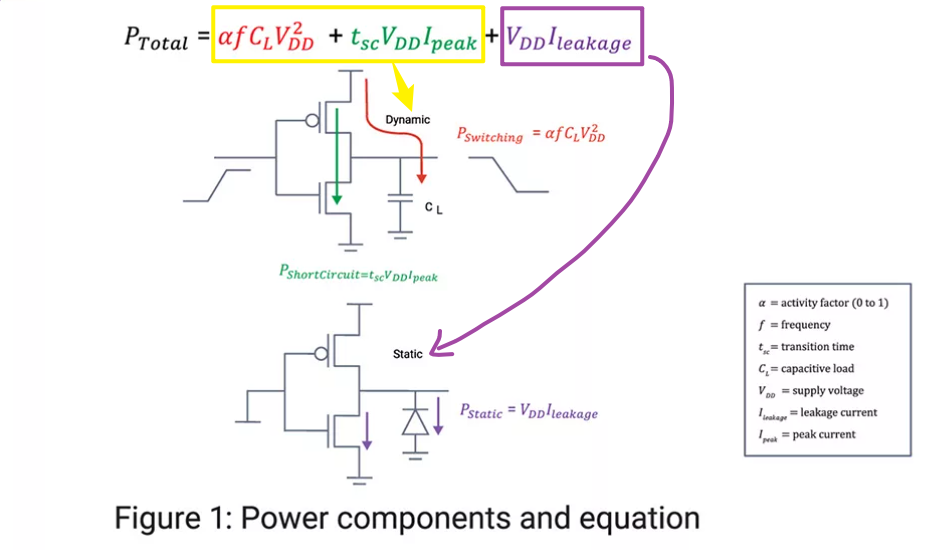

如图1所示,芯片总体功耗公式包含了动态功耗和静态功耗两大部分。

动态功耗(Dynamic Power)反映的是芯片中电路信号出现翻转时所产生的功耗。其又可分为翻转功耗(Switching power)和短路功耗(ShortCircuit power),翻转功耗简单来说就是在芯片正常工作过程中standard cell的状态随时钟或数据信号的变化而翻转(0→1之间的翻转)所产生的功耗,而短路功耗则是在信号翻转过程中出现的Pmos和Nmos同时导通,进而使VDD和GND短接而消耗的功耗

静态功耗(static power)也被称为漏电功耗(leakage power),也就是在没有翻转活动时流经MOS管的漏电流产生的功耗。尽管每个MOS管的漏电流很小,但由于每颗芯片中集成的晶体管也越来越多,导致芯片的整体leakage power也变得越来越高,在数字后端设计中,每个standard cell的leakage power都被记录在lib库中,因此计算静态功耗也十分方便。

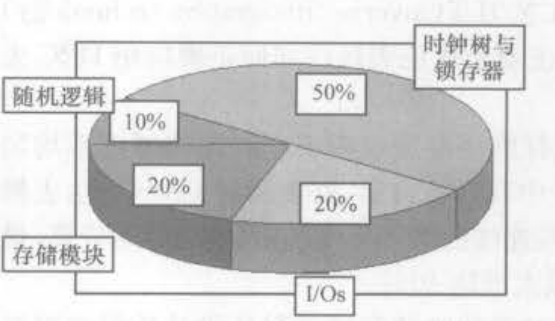

不同部分单元的功耗占比

在典型的芯片中,时钟电路的功耗约占总功耗的50%。存储校块和 I/0 功耗各约占 20% ,其余10 %的功耗为随机逻辑电路。

低功耗方法

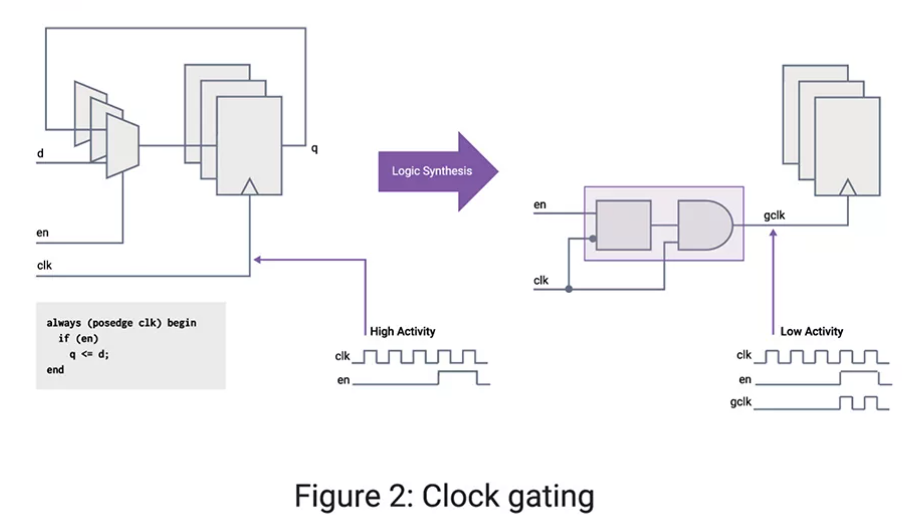

Clock Gating

从以上的功耗占比中,不难看出时钟电路在芯片的功耗中占了相当大的比重,而在低功耗设计中就有针对时钟电路的功耗优化方法---------Clock Gating

Clock gating通过在时序元件(如DFF)接收时钟的引脚前添加与门,进而可以通过使能信号来关断器件局部的时钟信号以降低功耗。它是一个目前较为成熟且广泛使用的低功耗设计技术。通常在RTL阶段,推荐使用带使能端的寄存器(如图2左侧RTL),那么在逻辑综合阶段,综合工具会自动进行Clock Gating的插入,进而通过减少寄存器上时钟的活动(Activity)来降低时钟电路的功耗。

根据实验结果,门控时钟方法功耗可以减少约50%左右的整体功耗。

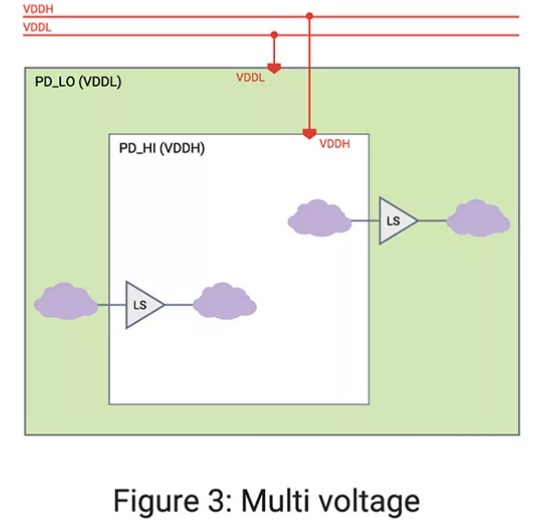

Multi Voltage

Multi Voltage,中文名"多电压域"技术。从图1的功耗方程可知,电压越高,每个组件消耗的功率就越高,导致整体功率增加。相反,电压越低,整体功率就越低。但电压又会影响器件的性能。因此为了在最低功耗下实现最佳性能,我们将设计进行性能划分 ------比如一个模块是高性能的,而芯片的其他部分性能较低,如图 3 所示。在高性能模块使用更高的电压;而为了在低性能模块上节省功耗,则使用较低的电压,这代替整个芯片同时在较高电压下的做法,进而降低芯片总体功耗,但也需要注意不同电压域中的逻辑要与相应的时序库对应。

根据实验结果,功耗可以减少约30%左右的整体功耗。

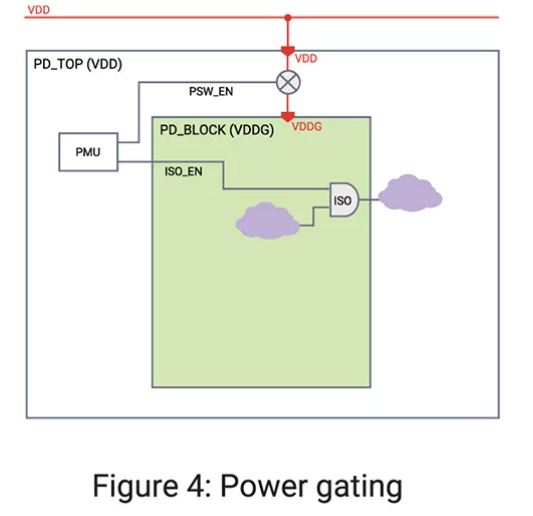

Power Gating

Power Gating,中文名"电源门控/电源关断"技术。它类似于多电压域技术,但这次电源域的电源直接连接到电源开关上,如图4所示。它通过关闭芯片中暂时不需要的某些模块来降低某些区域内的静态和动态功耗,使此区域功耗几乎为0。后端实现中通过使用power switch cell,来实现电源的ON/OFF,从而实现最激进的节能效果。并且,在外层需要实现一个电源管理单元(PMU),用于控制电源开关和隔离使能信号。

Multi-threshold voltage

Multi-threshold voltage,中文名"多阈值电压"技术。Foundary提供的标准单元通常会有多个不同阈值电压(Vth)的cell。常见的比如LVT, RVT,HVT。高阈值电压(Vth)的cell具有更小的漏电流,但相应的性能也会降低。因此可以在非关键的路径尽可能多地使用高阈值电压的cell(HVT cell),从而降低芯片静态功耗。

其他高级技术

专用低功耗库标准单元库、动态电压和频率调整(DVFS)、自适应电压和频率调整(AVFS)以及定制设计也是现在设计中常常使用的高级低功耗技术。

代码与文字齐飞,逻辑共创意一色 !若我的文章让你会心一笑,点个赞我们一起笑谈"IC人生"!