单通道 16bit 12GSPS/ 12bit 15.5GSPS/ 8bit 24GSPS

双通道 16bit 6.2GSPS/ 12bit 7.75GSPS/ 8bit 12GS/s

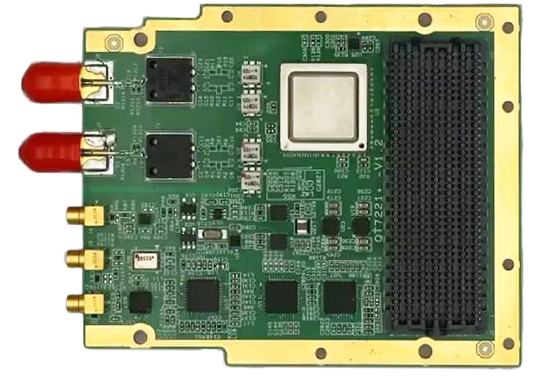

DAC FMC+子卡

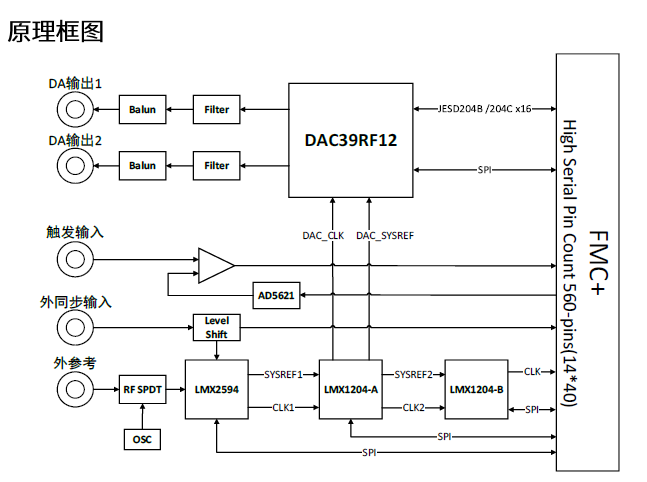

基于TI公司的高速DAC数模转换器DAC39RF12ACK和时钟芯片LMX2594而设计的标准单槽位的FMC+子卡。支持单通道模式或双通道模式,单通道模式下提供16bit 12GSPS、12bit 15.5GSPS(双边沿采集)或8bit 24GSPS(双边沿采集)D/A输出;双通道模式下提供16bit 6.2GSPS、12bit 7.75GSPS或8bit 12GSPS D/A输出D/A输出。输出阻抗50欧姆,采用交流耦合方式。支持1路触发输入以及1路外同步输入,时钟模式支持内部参考时钟输入、外部参考时钟输入两种。

板卡的电气与机械设计依据FMC+标准(ANSI/VITA 57.4),支持导冷散热,可适应于坤驰的多种FPGA载板,如Xilinx和Altera等的通用载板,以进行高性能的算法计算。

板卡必须配合能支持FMC+的FPGA载板安装使用,FMC+载板(FCC+)必须符合FMC+标准(ANSI/VITA 57.4)。该标准要求载板需要通过FMC+连接器为子卡提供直流3.3V、直流12V、直流VADJ三种电源。载板允许支持的VADJ/VIO_B的电压范围为1.65V~3.3V,一般建议VADJ/VIO_B运行电压为+2.5V或者+1.8V。

产品特点

-

DAC采用TI公司的DAC39RF12,支持最多2通道输出,最高24GSPS/8bit;

-

输出频率:

* 8位、单通道、DES 模式:24GSPS;

* 12位、单通道、DES模式:15.5GSPS

* 16 位、单通道:12GSPS;

* 8位、双通道:12GSPS;

* 12位、双通道:7.75GSPS;

* 16 位、双通道:6.2GSPS;

-

5个射频接口,其中2个为SMA形式,用作DA输出;3个为XSMP形式,1个用作外参考输入,1个用作外同步输入,1个用作外触发输入;

-

适应范围:完全符合Vita57.4规范,包括结构件,子卡尺寸,面板连接器,正反面器件的限高等,大大提供了子卡的通用性和适配性;

-

多种散热方式:导冷;

-

AC耦合输入;

-

内外部时钟可根据需要选择;

-

HSPC高引脚数连接器;

-

工作温度:-10℃~+55℃;