ps内核-----寄存器-------外设(通过配置寄存器来控制外设)

控制IO管脚的寄存器一般被称为GPIO;

那其实,PL就相当于PS的一个外设,就会有对应的地址和寄存器

AXI4总线主要用于主设备和从设备之间的通信(片内总线);因为是片内总线所以在FPGA内部主要功能有两个。1,FPGA内部两个模块的数据传输。2,ZYNQ中PS和PL的交互

AXI4是突发传输的;关于突发传输:是只发送一个地址,然后发送突发长度N个数据(这时地址会自动排列生成);下一次只需要从地址N+1开始发送即可

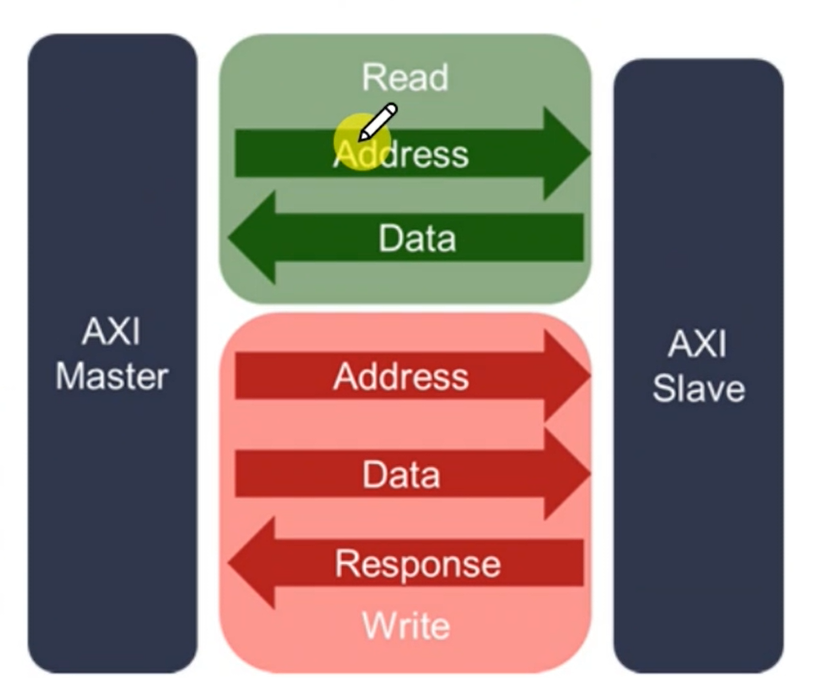

AXI的通道是读写分离的,如下

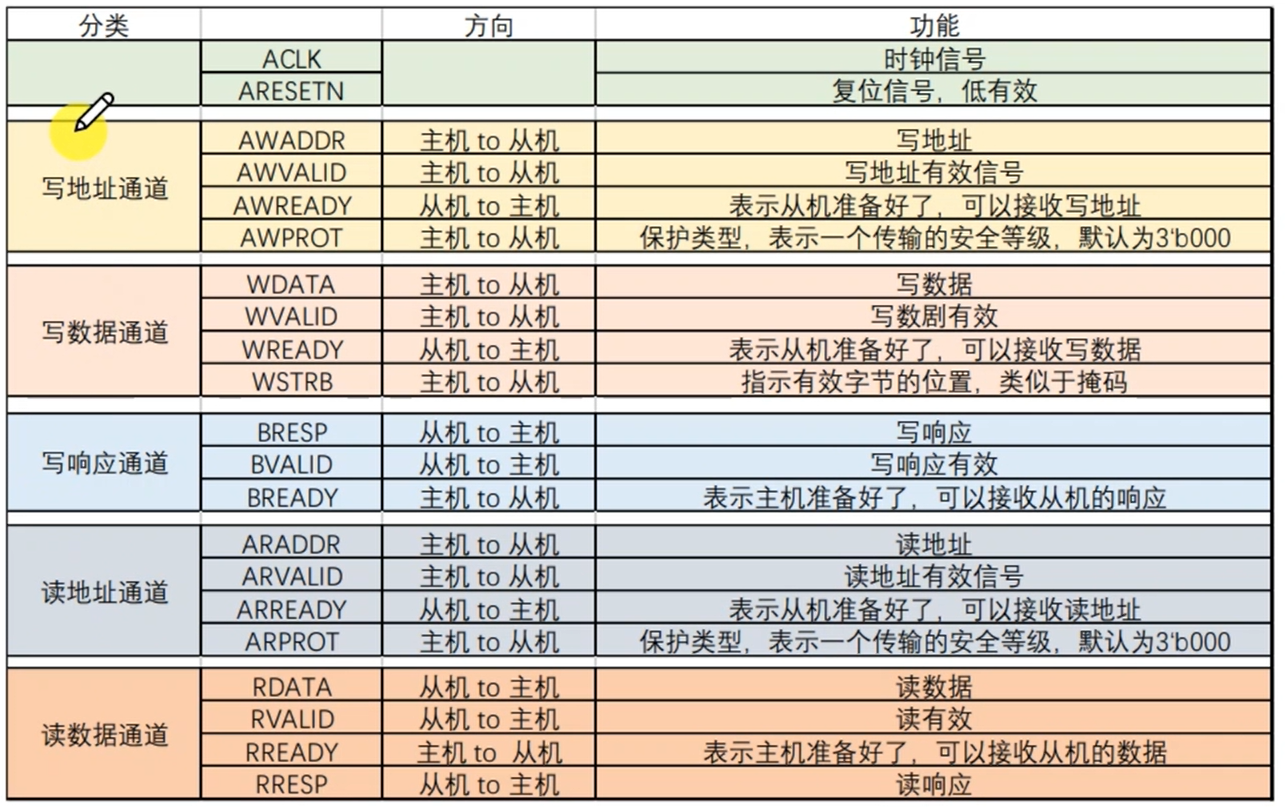

AXI传输采用握手信号:例如写数据时:当主机的写数据有效信号wvalid和从机响应的有效信号wready同时拉高(在clk上升沿检测到),主机才能将数据写入

需要注意的是,axi-lite最多32bit,

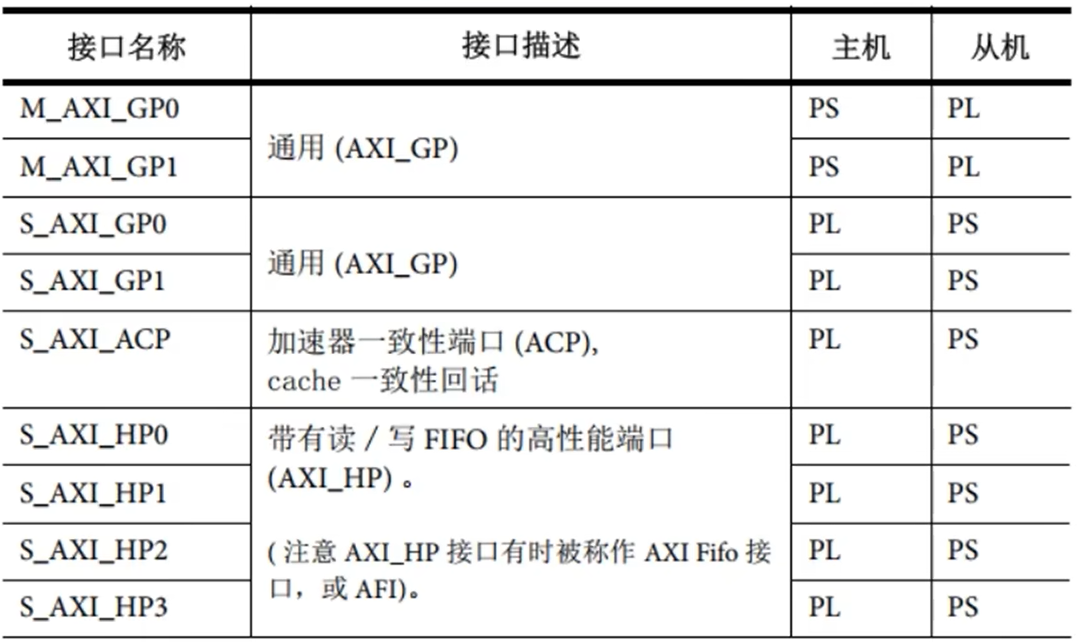

GP,HP,ACP都在PS端(ARM),用于与PL端(FPGA)通信。PS和PL之间的接口如下:

假设采用AXI-GP接口**(PL为主机,PS为从机)**,那么PS先将数据写入cache缓存,再写入DDR3控制器,最后到DDR;PL端则是通过GP接口将数据写入DDR3控制器再到DDR3,这样间接实现了PS与PL的交互。