【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

zynq最大的优势,就是把arm和fpga结合在一起了。这样一颗soc里面,就可以用软件去驱动外设ip,这是之前没有过的体验。因为以前,arm和fpga通信,大多数都是分列式设计,arm是单独的一颗soc,fpga也是单独的芯片,两者通过外部总线沟通,比如pcie等等。现在有了zynq,直接借助于axi总线就能通信。但是很多小伙伴呢,还是不太明白fpga该怎么开发,以及verilog、仿真、fpga和芯片设计的关系,正好借此机会聊一下。

1、verilog

verilog是一门描述语言,和它类似的还有vhdl。有了描述语言,我们就可以描述时序电路、组合逻辑电路,这两部分都是设计的基础。再加上输入接口、输出接口、时钟、复位、状态机,不管是硬件协议,还是算法电路,都可以去实现了。所以学好verilog的前提是数字电路,只要掌握了数字电路,就可以明白verilog的基本原理了。至于语法中的阻塞、非阻塞,以及综合、不可综合,这些概念遇到的时候处理一下即可。

2、仿真

verilog的仿真,就类似于c语言port到嵌入式开发板子前,先用windows平台仿真一下是一个道理。仿真不仅可以模拟出各种激励信号,还能实现自动化测试,非常适合上板之前的功能确认。**从工具层面,verilog不考虑布局布线,也不考虑功耗,只是从功能层面确认下实现是否ok。**而且,仿真的效率一般非常之高,有兴趣的小伙伴甚至可以自己写一个仿真器。

从大的地方说,仿真就是按照复位信号,组合逻辑、时序逻辑、组合逻辑一步一步往前走,按照这个思路,自己就可以写一个最简单的仿真器。比如,我们出现这样一个电路,

assign d = a ? b : c;如果改成c语言,基本就是这样的组合逻辑,

int get_data(int a, int b, int c)

{

if(a)

{

return b;

}

else

{

return c;

}

}

int d = get_data(a,b,c);哪怕是时序逻辑,也可以处理。计算的时候,如果clock没有到,先计算组合逻辑,然后clock来临之后,把组合逻辑的结果赋值给寄存器,这样就可以实现时序仿真了。

3、fpga

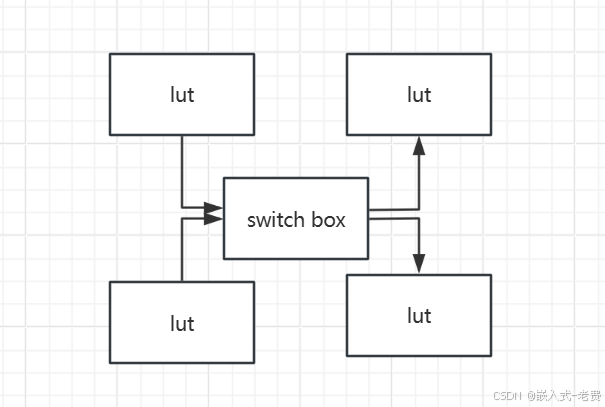

fpga是介于软件和硬件的产物。**本质上fpga是由一个一个的lut查找表、开关连线、外设三部分组成。**当然,除了这三部分,还是pll、rom、ram、fifo、dsp等资源。最主要的部分,还是刚才说的lut、switch box、io。

其中lut本质上就是查找表,它不知道什么与或非,我们需要什么功能,工具帮忙编译成对应的lut就可以了。比如一个或门,就可以是 0 0 0/ 0 1 1/ 1 0 1/ 111。前面两个输入,最后一个是输出。当然除了组合逻辑之外,lut内部一般还有d触发器,这个用来处理时序电路。因此,我们写的组合逻辑和时序逻辑都是由这样一个一个lut拼起来的。

既然是拼起来的lut,那么就会涉及到模块和模块的互联。比如下面这句话,

assign flag = (a|b) & (c|d);这个flag信号的处理,来自于a、b、c、d。假设lut最大只能处理两路信号,那么这个电路就需要三个lut才能实现。第一个lut处理a和b,第二个lut处理c和d,然后两个lut的处理结果送到第三个lut,这样才实现了基本的flag输出。那么lut直接按怎么通信呢,其实内部可以看成是这样一个结构,

有了swich box之后,就可以这样一直把信号传递下去。当然,换一个角度来看,switch box也是一种特殊的lut。至于输入输出模块也是一样,只不过这种输入、输出要涉及到fpga的引脚,本质上也是一种特殊的lut。

4、asic芯片

verilog本身作为描述语言,可以描述fpga,也可以描述芯片的设计。fpga下面除了lut,还有pll、dsp、fifo、rom、ram等很多资源,所以fpga看上去更像是搭积木,fpga的工具就是把用户的verilog的描述映射到这一个一个资源上面。虽然整体很方便,不过也容易出问题,比如布局布线,信号和信号之间会不会距离太长,需不需要加时间约束等等。所以对于fpga来说,前端设计和后端设计是一体的,后端设计是fpga厂家的工具帮助自动完成的。因此,很多芯片设计开发功能的时候,都是用fpga来做前端设计的,甚至是几块fpga芯片一起来仿真。

而asic设计,看上去更像是从0到1开始造房子。虽然也是用verilog开发,但是底层实现来自于代工厂的工艺库,里面有组合逻辑、时序逻辑、rom、ram模块等等。工艺库就是实实在在的mos管逻辑电路,而不是fpga那种查表机制的lut了。不过,soc里面有些ip需要从第三方购买,有些ip需要自己设计,这些ip都ok之后,通过总线连接在一起之后,这才相当于完成了基本的soc逻辑设计。接下来就是后端工程师的工作。

**芯片的前后端设计,非常类似于电路的前后端设计,电路的前端设计就是原理图设计,电路的后端设计就是pcb layout。**原理图ok不见得pcb就ok。比如电源摆放是不是合理,模数有没有分开,高频、低频有没有分开,发热有没有提前布局,这都是pcb layout考虑的。后端芯片设计也是一样,比如pin脚布局、时钟树设计、电源信号处理等等,既要有利于生产、提高良品率,也要考虑到后续客户的使用习惯。哪怕现在很多芯片后端设计都是外包的,至少发包方要在关键指标上提出明确诉求,不然很容易烂尾掉,毕竟芯片流片也不便宜。

fpga本身依赖于查表和ram机制,这是它自身的可编程性决定的,也是fpga得以存在的基础。因此不管是功耗上,还是频率上,都不如asic。但是fpga胜在一个灵活,因此只有量大的场景才会asic化,如果是非标类的应用,一般用fpga就可以了,尤其是图像和通信类领域。