一、研究背景与意义

在无线通信技术高速发展的当下,5G-A、6G等新一代通信系统对传输速率、时延、可靠性提出了更为严苛的要求。无线信道作为通信系统的核心组成部分,其特性直接决定了通信质量。然而,真实无线信道存在多径衰落、多普勒频移、噪声干扰等复杂问题,直接进行外场测试不仅成本高昂、周期漫长,还难以精准复现各类极端信道场景。

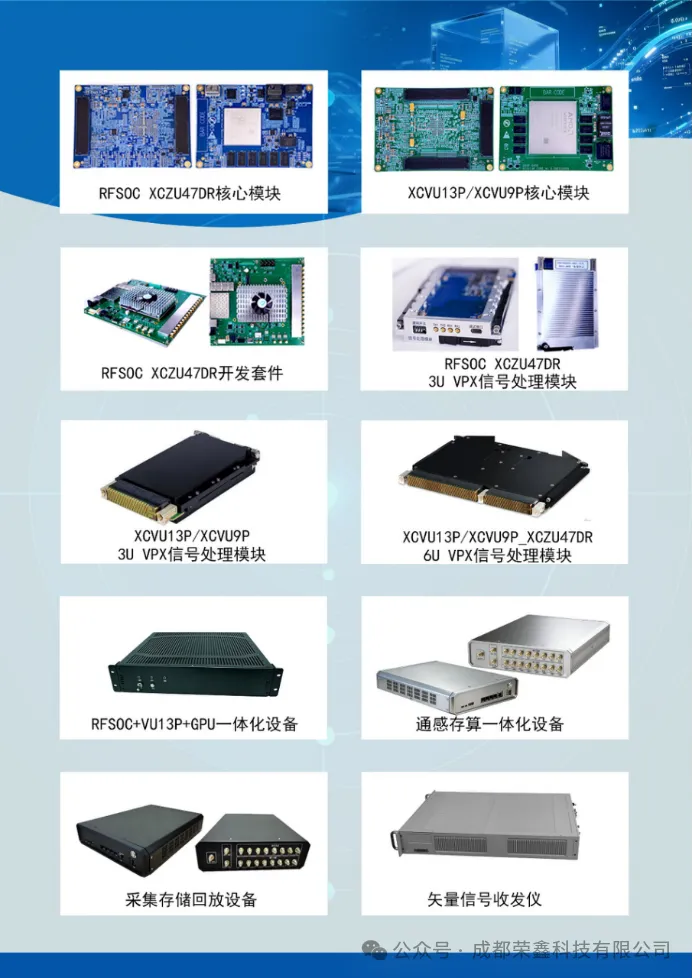

无线信道模拟技术通过在实验室环境中构建与真实场景等效的信道模型,为通信设备研发、算法验证、系统性能测试提供了高效、可控的解决方案。Xilinx的射频系统级芯片(RFSOC)与VU13P现场可编程门阵列(FPGA)开发板的组合,凭借其高集成度、强算力及灵活可配置的特性,成为当前无线信道模拟领域的核心技术方案之一,深入分析其技术应用具有重要的工程价值与理论意义。

二、核心组件概述

本次分析的核心硬件组合为RFSOC芯片与VU13P开发板,二者在功能上优势互补,共同支撑起高精度、高实时性的无线信道模拟需求。

RFSOC作为集成射频前端与处理核心的系统级芯片,内部包含高性能ARM处理器、FPGA逻辑单元、数模转换器(DAC)、模数转换器(ADC)及射频收发器等核心模块,可直接实现射频信号的采集、生成与初步处理,大幅简化了硬件系统的搭建流程。

VU13P是Xilinx推出的基于Virtex UltraScale+系列FPGA的开发板,其搭载的FPGA芯片拥有海量的逻辑资源、高速串行收发器(GTY)及丰富的外设接口,具备强大的数据并行处理能力与高速数据传输能力,能够承载信道模拟中复杂算法的实时运算,为系统提供充足的算力支撑。

三、RFSOC+VU13P无线信道模拟系统技术基础

3.1 无线信道模拟核心需求

无线信道模拟需满足"高保真、高实时、高灵活"三大核心需求。高保真要求模拟系统能够精准复现多径传播、多普勒效应、路径损耗、阴影衰落等真实信道特性;高实时要求系统对输入信号的处理延迟控制在微秒级甚至纳秒级,确保与真实通信场景的时间同步性;高灵活则要求系统能够根据不同通信标准(如5G、WiFi 6)和测试场景,快速调整信道参数与模型类型。

3.2 核心组件技术优势

RFSOC与VU13P的组合之所以能够满足上述需求,源于二者突出的技术优势。

RFSOC的优势在于"一体化集成",其内部集成的射频收发器可支持GHz级带宽信号的处理,ADC/DAC模块具备高采样率与高分辨率特性,能够精准捕获和生成射频信号;同时,其内置的ARM处理器可实现系统控制、参数配置等事务性处理,FPGA逻辑单元可完成初步的信号预处理,提升数据处理效率。

VU13P的核心优势在于"超强算力与扩展能力",其搭载的Virtex UltraScale+ FPGA拥有数万个人工智能引擎(DSP48E2)和大量的块随机存取存储器(BRAM),可并行执行信道均衡、多径叠加、噪声生成等复杂算法;高速GTY收发器支持高达28Gbps的数据传输速率,能够实现RFSOC与VU13P之间的高速数据交互,避免数据传输成为系统瓶颈。

四、RFSOC+VU13P无线信道模拟系统架构设计

4.1 系统整体架构框图

RFSOC+VU13P无线信道模拟系统采用"分层架构、分工协作"的设计思路,整体分为射频前端层、数据传输层、核心处理层、控制管理层及外部接口层五个部分,各层之间通过高速总线与接口实现数据交互与指令传输,系统架构框图如下所示:

4.2 各模块功能详解

1.射频前端层

该层基于RFSOC内置的射频收发器实现,主要功能为完成射频信号的接收与发射。接收端将外部设备(如基站信号源、待测终端)发送的射频信号进行低噪声放大、混频、滤波等处理,将其转换为适合ADC采样的中频信号;发射端则将DAC输出的中频信号进行上变频、功率放大,转换为符合通信标准的射频信号,发送至待测设备。RFSOC的射频收发器支持宽频段调节,可覆盖从Sub-6GHz到毫米波的主流通信频段,满足不同场景的测试需求。

2.数据转换层

由RFSOC内部的高分辨率ADC与DAC组成,是连接模拟射频信号与数字基带信号的桥梁。ADC负责将射频前端输出的模拟中频信号转换为数字基带信号,其高采样率(最高可达数GSps)确保了宽带宽信号的完整采集,高分辨率(12位及以上)则降低了量化噪声对信号质量的影响;DAC则将核心处理层输出的数字基带信号转换为模拟中频信号,输送至射频前端进行上变频处理,同样具备高采样率与高线性度特性,保证了模拟信号的保真度。

- 数据传输层

采用"高速SerDes接口+AXI总线"的混合传输架构,实现RFSOC与VU13P之间的高速数据交互及芯片内部的数据传输。其中,RFSOC与VU13P通过Virtex UltraScale+系列FPGA特有的GTY高速串行收发器连接,数据传输速率可达28Gbps,能够满足多通道、宽带宽信号的实时传输需求;芯片内部则通过AXI4-Stream总线实现FPGA逻辑单元、ARM处理器与ADC/DAC之间的低延迟数据交互,确保数据处理的连续性与实时性。

4.核心处理层

作为系统的"算力核心",由VU13P搭载的FPGA与RFSOC内置的FPGA逻辑单元协同组成,负责执行无线信道模拟的核心算法。其中,VU13P FPGA凭借海量的DSP资源与BRAM资源,承担主要的信号处理任务,包括多径信道建模、多普勒频移模拟、路径损耗计算、加性噪声生成等复杂并行运算;RFSOC内置的FPGA逻辑单元则负责数据的预处理(如信号滤波、降采样)与后处理(如信号合成、格式转换),减轻VU13P的算力负担,提升系统整体处理效率。二者通过数据传输层实现紧密协同,确保信道模拟的实时性与高精度。

5.控制管理层

以RFSOC内置的ARM处理器为核心,结合上位机软件实现系统的全流程控制与监控。ARM处理器负责解析上位机发送的配置指令(如信道模型参数、工作频段、信号带宽等),并将其转换为FPGA可执行的控制信号,实现对射频前端、ADC/DAC、数据传输及核心处理模块的参数配置;同时,ARM处理器还负责采集系统各模块的工作状态(如信号功率、数据传输速率、芯片温度等),并反馈至上位机,实现对系统的实时监控。上位机软件则提供可视化的操作界面,方便用户设置信道参数、选择信道模型及查看测试结果,降低系统的操作复杂度。

6.外部接口层

提供丰富的外部接口,实现系统与外部设备的连接及数据交互。主要包括以太网接口(用于上位机与系统的远程通信及数据传输)、USB接口(用于本地配置与调试)、JTAG接口(用于FPGA程序的下载与调试)以及射频接口(用于连接外部信号源与待测设备)。多样化的接口设计提升了系统的兼容性与易用性,使其能够灵活适配不同的测试场景。

五、RFSOC+VU13P无线信道模拟系统工作原理

5.1 核心工作流程

RFSOC+VU13P无线信道模拟系统的工作流程围绕"信号采集-信道建模-信号重构-信号输出"四个核心环节展开,各环节紧密衔接,实现对真实无线信道的精准模拟,具体流程如下:

-

系统初始化与参数配置:用户通过上位机软件设置信道模拟参数,包括信道模型(如瑞利信道、莱斯信道、COST 231模型等)、多径数量、多普勒频移大小、路径损耗系数、噪声功率等;上位机将配置指令通过以太网发送至RFSOC的ARM处理器,ARM处理器解析指令后,向RFSOC的射频前端、ADC/DAC及VU13P的FPGA发送控制信号,完成系统参数的初始化配置。

-

信号采集与转换:外部信号源(如基站模拟器)或待测终端发送的射频信号通过射频接口输入至RFSOC的射频前端,射频前端对信号进行低噪声放大、混频、滤波等处理,将其转换为中频模拟信号;随后,中频模拟信号输入至RFSOC的ADC模块,ADC将其转换为数字基带信号,并通过AXI总线将数字信号传输至RFSOC内置的FPGA逻辑单元进行预处理。

-

高速数据传输:RFSOC内置FPGA完成信号预处理后,通过高速SerDes接口(GTY)将数字基带信号以28Gbps的速率传输至VU13P的FPGA,确保数据在传输过程中无延迟、无失真,为后续的实时信道建模提供保障。

4.核心信道建模与处理:VU13P的FPGA作为核心处理单元,基于预设的信道模型对输入的数字基带信号进行处理,这一过程是无线信道模拟的核心,主要包括以下关键步骤:

多径信号生成:根据配置的多径数量,FPGA通过延迟单元为输入信号添加不同的时间延迟,模拟真实信道中信号经不同路径传播产生的多径效应;

-

多普勒频移模拟:通过数字混频器为不同路径的信号添加对应的频偏,模拟收发双方相对运动产生的多普勒效应,频偏大小可根据配置参数实时调整;

-

路径损耗与衰落处理:利用衰减器与随机数生成器,为各径信号添加对应的路径损耗与阴影衰落,其中路径损耗基于距离参数计算,阴影衰落通过高斯随机数模拟;

-

噪声叠加:通过噪声生成模块生成符合高斯分布的加性白噪声,根据配置的噪声功率将其叠加至处理后的信号中,模拟信道中的背景噪声干扰。

-

信号重构与回传:VU13P的FPGA完成信道建模与信号处理后,将处理后的数字基带信号通过高速SerDes接口回传至RFSOC的FPGA逻辑单元,RFSOC FPGA对信号进行后处理(如信号合成、格式转换),随后将其传输至DAC模块;DAC将数字信号转换为中频模拟信号,输送至射频前端。

-

模拟信号输出:RFSOC的射频前端将中频模拟信号进行上变频、功率放大等处理,转换为符合通信标准的射频信号,通过射频接口输出至待测设备(如终端接收机),完成整个信道模拟过程;同时,RFSOC的ARM处理器实时采集系统各模块的工作状态数据,回传至上位机,用户可通过上位机界面实时监控信号质量与系统运行状态。

5.2 关键技术支撑

系统能够实现高精度、高实时性的信道模拟,得益于两大关键技术的支撑:一是"异构计算架构",RFSOC的ARM处理器负责事务性控制,RFSOC FPGA负责数据预处理,VU13P FPGA负责核心并行运算,三者分工明确、协同高效,充分发挥了各硬件单元的优势;二是"高速数据传输技术",GTY高速SerDes接口的应用确保了数据在RFSOC与VU13P之间的高速传输,避免了数据拥堵,为实时信道建模提供了带宽保障。

六、技术系统性能优势与应用场景

6.1 系统性能优势

6.1.1 性能优势-高保真度

高保真度:RFSOC的高分辨率ADC/DAC(12位及以上)与高线性度射频前端,能够精准捕获和生成射频信号,降低量化噪声与非线性失真;VU13P FPGA强大的算力支持复杂信道模型的精准实现,可有效复现多径衰落、多普勒频移等真实信道特性,模拟误差控制在较低水平。

6.1.2 性能优势-高实时性

高速SerDes接口实现了数据的低延迟传输,结合FPGA的并行处理架构,系统对信号的处理延迟可控制在微秒级,能够满足实时通信场景的测试需求,避免因处理延迟导致的测试结果偏差。

6.1.3 性能优势-高灵活性

基于FPGA的可编程特性,系统可通过修改固件程序快速切换不同的信道模型(如从瑞利信道切换至莱斯信道),调整多径数量、多普勒频移等参数;RFSOC的宽频段射频前端支持不同通信标准(5G、WiFi 6、卫星通信等)的信号处理,适配多样化的测试场景。

6.1.4 性能优势-高集成度

RFSOC集成了射频前端、ADC/DAC、处理器与FPGA逻辑单元,大幅简化了系统硬件结构;VU13P开发板提供了丰富的外设接口与扩展资源,无需额外搭建复杂的硬件电路,降低了系统的体积与功耗。

6.2 典型应用场景

6.2.1 通信设备研发与测试

在基站、终端等通信设备的研发过程中,利用该系统模拟不同信道场景(如城市密集城区、高速移动场景),可快速验证设备的抗衰落、抗干扰能力,缩短研发周期;在设备量产测试阶段,通过标准化的信道模拟环境,实现对设备性能的批量、高效测试,提升测试效率与一致性。

6.2.2 通信算法验证

为信道编码、调制解调、波束赋形等通信算法的验证提供可控的信道环境。研发人员可通过调整系统的信道参数,测试算法在不同信道条件下的性能(如误码率、吞吐量),为算法优化提供数据支撑,加速算法的迭代升级。

6.2.3 教学与科研实验

在高校通信专业的教学与科研中,该系统可作为实验平台,直观展示无线信道的特性及信道模拟原理;科研人员可基于该平台开展新一代通信技术(如6G)的信道建模与仿真研究,为前沿技术突破提供硬件支撑。

七、总结与展望

总结:RFSOC与VU13P的组合通过"集成化射频处理+高速并行计算"的架构设计,构建了一套高精度、高实时性、高灵活性的无线信道模拟系统。该系统以RFSOC为核心实现射频信号的采集、转换与初步处理,以VU13P FPGA为算力核心完成复杂信道模型的实时运算,通过高速数据传输层实现二者的紧密协同,最终实现对真实无线信道的精准模拟。相较于传统的信道模拟方案,该系统在保真度、实时性、灵活性及集成度上均具备显著优势,能够有效满足通信设备研发、算法验证、教学科研等多场景的需求,为无线通信技术的发展提供了重要的硬件支撑。

相较于传统的信道模拟方案,该系统在保真度、实时性、灵活性及集成度上均具备显著优势,能够有效满足通信设备研发、算法验证、教学科研等多场景的需求,为无线通信技术的发展提供了重要的硬件支撑。

展望:随着5G-A、6G技术的进一步发展,无线信道模拟将面临更高带宽、更复杂场景(如空天地一体化通信)的挑战。未来,可从以下方向对RFSOC+VU13P系统进行优化升级:一是引入AI算法,实现信道模型的自适应调整与动态优化,提升对复杂信道场景的模拟能力;二是扩展系统的通道数量,支持多用户、多输入多输出(MIMO)场景的信道模拟;三是结合高速存储技术,实现信道数据的实时记录与回放,为后续的数据分析与算法优化提供便利。

相信随着技术的不断迭代,RFSOC+VU13P组合在无线信道模拟领域的应用将更加广泛,为新一代通信技术的发展注入更强动力。

成都荣鑫科技原创内容,欢迎技术交流及合作,盗者必追究

更多资料:RFSOC+VU13P在无线信道模拟中的技术应用分析报告