一:优化逻辑级数主要就是减少组合逻辑

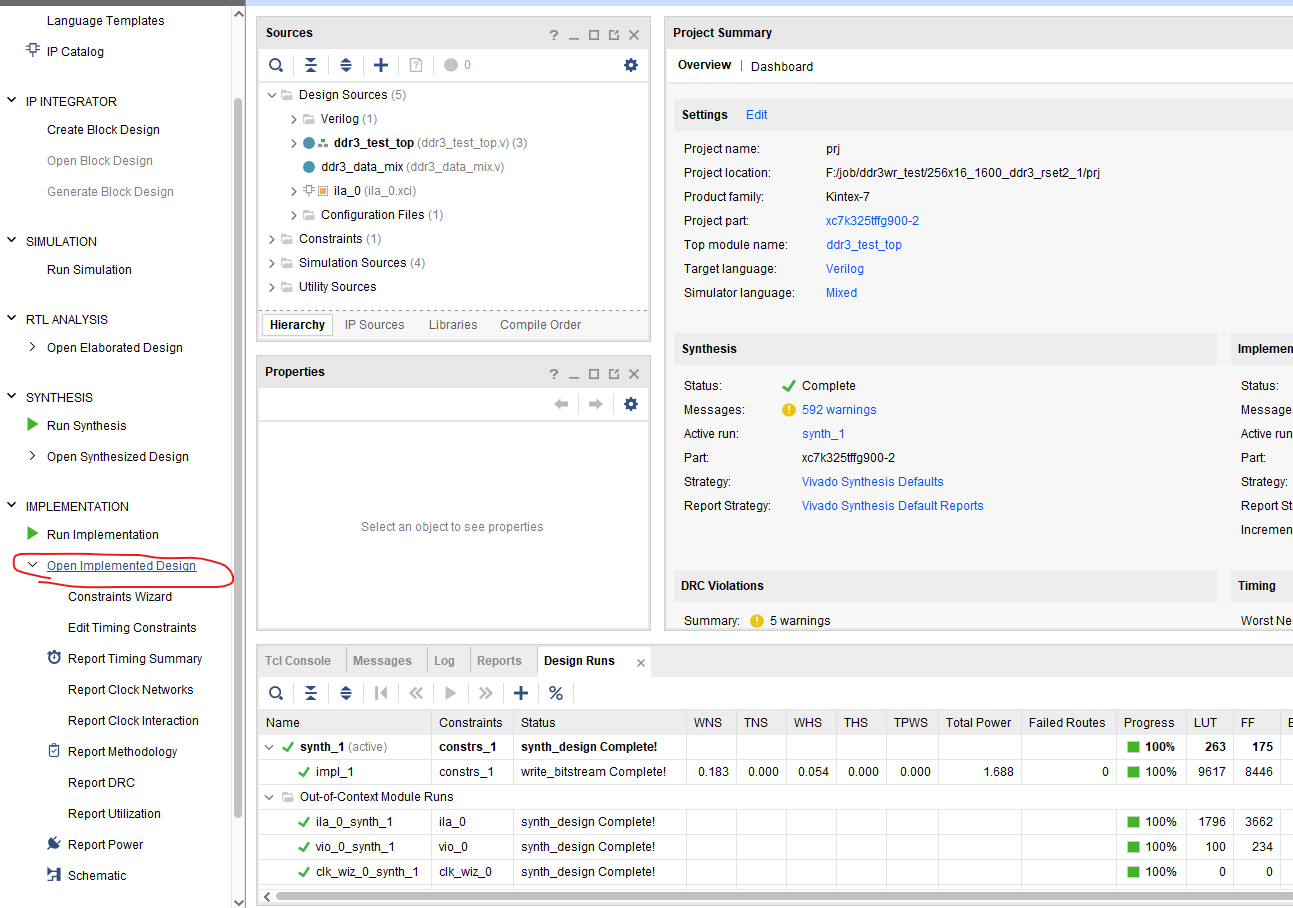

二:打开方式:

1:

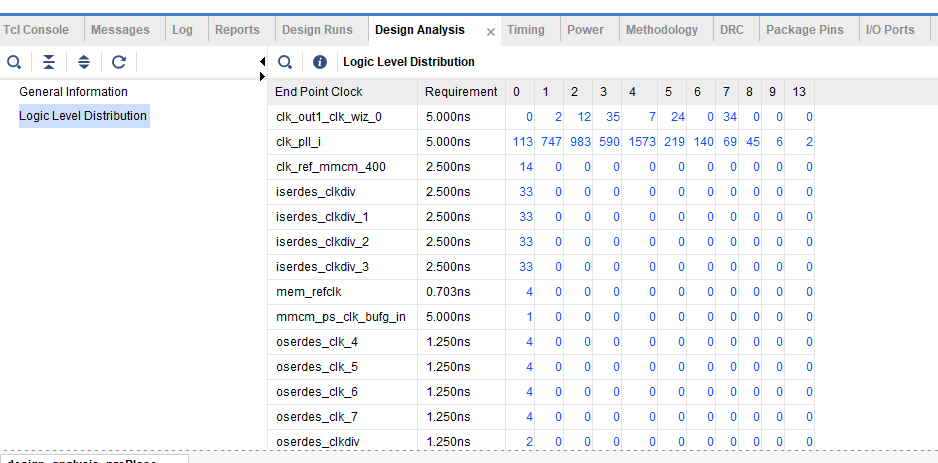

2:在tcl输入如下指令:

2:在tcl输入如下指令:

report_design_analysis -logic_level_distribution -logic_level_dist_paths 5000 -name design_analysis_prePlace

3

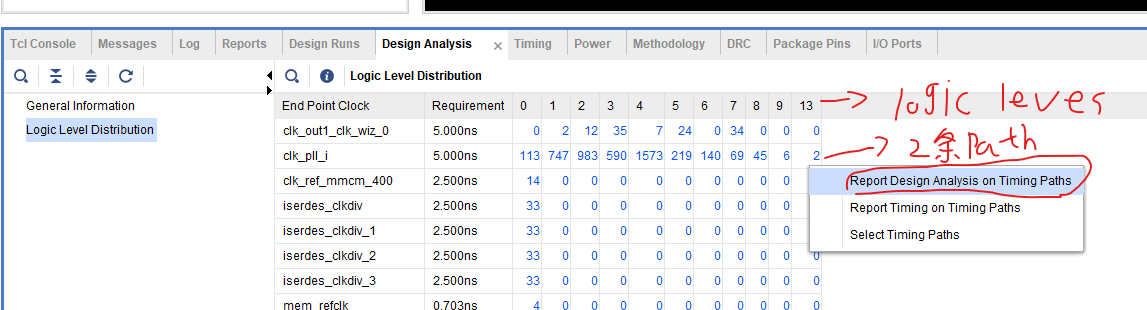

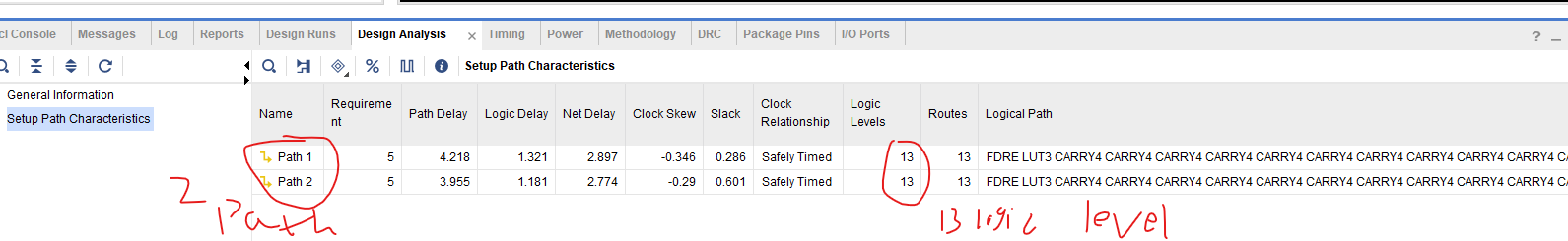

4:

5:

三:如何优化逻辑级数

1:ila位宽太大

2:计数器位数太高

3:用流水线代替组合逻辑

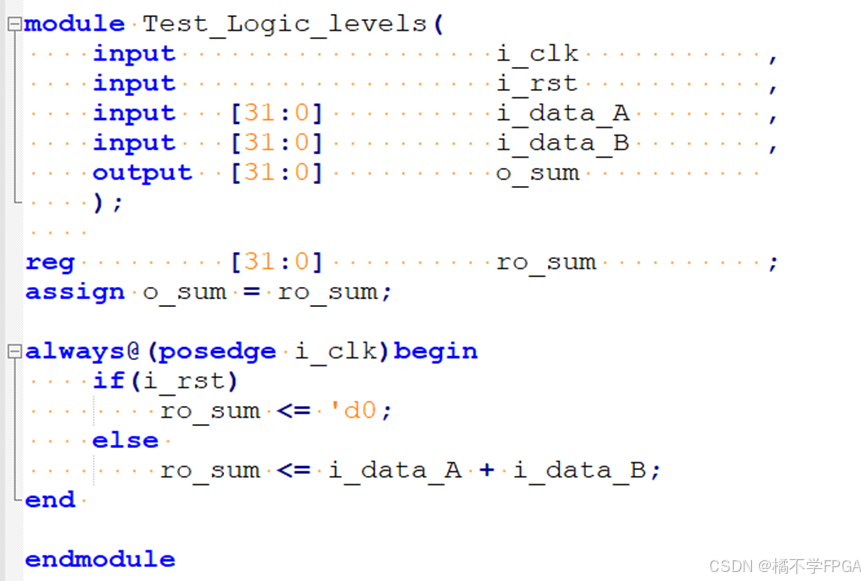

3.1ng

3.2ok

module Test_Logic_levels(

input i_clk,

input i_rst,

input [31:0] i_data_A,

input [31:0] i_data_B,

output [31:0] o_sum

);

// 拆分输入为高低16位

wire [15:0] A_low = i_data_A[15:0];

wire [15:0] A_high = i_data_A[31:16];

wire [15:0] B_low = i_data_B[15:0];

wire [15:0] B_high = i_data_B[31:16];

// 第一级:低16位加法结果+进位寄存器

reg [15:0] low_sum_reg;

reg carry_reg; // 低16位加法的进位

// 第二级:高16位加法结果寄存器

reg [15:0] high_sum_reg;

// 输出拼接

assign o_sum = {high_sum_reg, low_sum_reg};

// 第一级:低16位加法(组合逻辑)+ 寄存器打拍

always@(posedge i_clk) begin

if(i_rst) begin

low_sum_reg <= 16'd0;

carry_reg <= 1'b0;

end else begin

// 低16位加法,计算和与进位

{carry_reg, low_sum_reg} <= A_low + B_low;

end

end

// 第二级:高16位加法(含低16位进位)+ 寄存器打拍

always@(posedge i_clk) begin

if(i_rst) begin

high_sum_reg <= 16'd0;

end else begin

// 高16位加法,加上低16位的进位

high_sum_reg <= A_high + B_high + carry_reg;

end

end

endmodule