【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

前面我们学习了按键和led,虽然可以做一些基础的外设控制。比如,假设把led换成卷帘门的话,这就是卷帘门开关了。当然,这里用mcu也可以,用带网络的gpio设备也可以,用fpga有点大材小用,过于奢侈了。今天我们学一下pwm输出,其实pwm在电机控制领域很有用。

1、什么是pwm

所谓的pwm方波,就是在一段时间内,部分时间输出高电平,部分时间输出低电平。这一段时间就叫控制周期,可以是1ms,也可以是100us,根据实际情况而定。此外,控制周期内的高低电平比例,也是可以设定的,最小为0,最大为100%。

2、pwm的应用场景

很多场景下,都会使用到pwm,比如说光源,比如说电机。大家可能对电机比较熟悉,因为对电机的控制主要就两种,一种是直接电流控制,一种是pwm控制。如果是pwm控制,那就是说在控制板和电机之间,还有一个驱动板,我们给驱动板输入pwm信号,就可以控制电机的转速。

光源其实也是一样的,有的时候工业图像、或者医疗图像需要进行控光处理,这个时候如果需要图像亮一点,那就曝光时间长一点,反之则短一点,控制方式也是pwm。

3、pwm的两个参数

pwm本身比较简单,它的两个重要参数就是控制周期和占空比。后续我们写verilog代码的时候,本质也是对这两个参数进行设置。如果不是写verilog,而是写pwm驱动,或者是对pwm进行设置,本质上也是操作这两个参数。

4、pwm实现

本身pwm还是比较简单的,一方面通过count计数控制好周期,另外一方面通过阈值设置好占空比即可。需要注意的是,我们输出pwm的时候,在一个周期内,一般是先输出0,再输出1,这样比较合理。另外还有一点,就是周期恢复为0的时候,输出信号需要快速恢复为0。

module pwm(input clk,

input rst,

input ce,

output reg out);

reg[15:0] count;

`define FREQUENCY_COUNT 16'd29

`define PART_RATIO 16'd9

always@(posedge clk or negedge rst)

if(!rst)

count <= 16'h0;

else if(ce) begin // switch

if(count != `FREQUENCY_COUNT) // frequency

count <= count + 16'h1;

else

count <= 16'h0;

end else

count <= 16'h0;

always@(posedge clk or negedge rst)

if(!rst)

out <= 1'b0;

else if(ce) begin // switch

if(count < `PART_RATIO || count == `FREQUENCY_COUNT) // part ratio

out <= 1'b0;

else

out <= 1'b1;

end else

out <= 1'b0;

endmodule代码为了做仿真,FREQUENCY_COUNT和PART_RATIO设置都比较小,实际使用的时候一般都比较大。

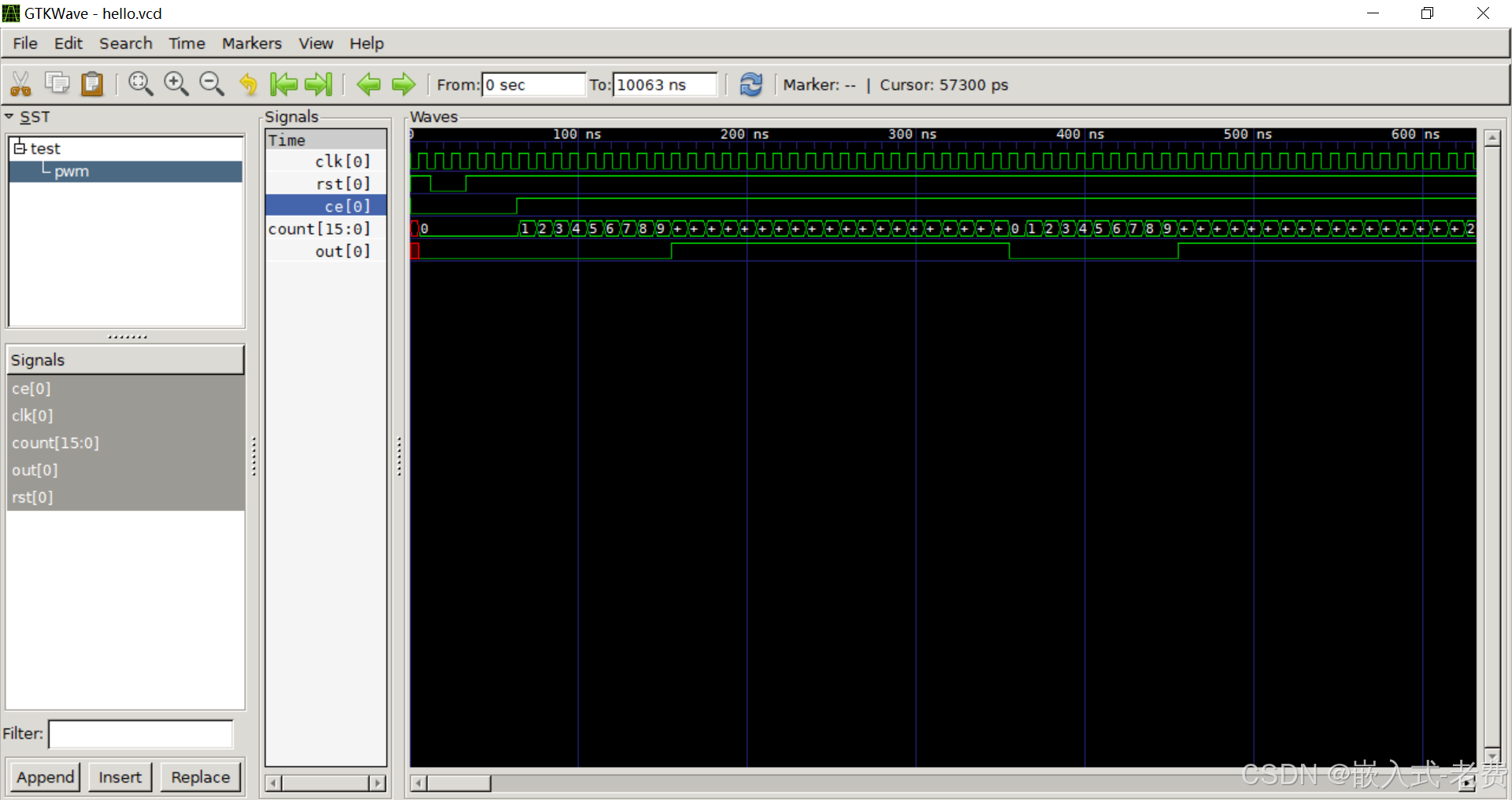

5、仿真和测试

在上板子验证之前,最好先借助于iverilog仿真下,不出意外的话,就可以看到这样的波形,

需要tb文件的朋友,可以参考下这里的tb文件,

`timescale 1ns/1ps

module test();

reg rst;

reg clk;

reg ce;

wire out;

initial

begin

rst = 1;

clk = 0;

ce = 0;

#12 rst = 0;

#21 rst = 1;

#30 ce = 1;

#10000 $finish;

end

initial

begin

while(1)

clk = #5 !clk;

end

pwm pwm(.rst(rst),

.clk(clk),

.ce(ce),

.out(out));

initial

begin

$dumpfile("hello.vcd");

$dumpvars(0, test);

end

endmodule