NIOS ii工程移植路径问题

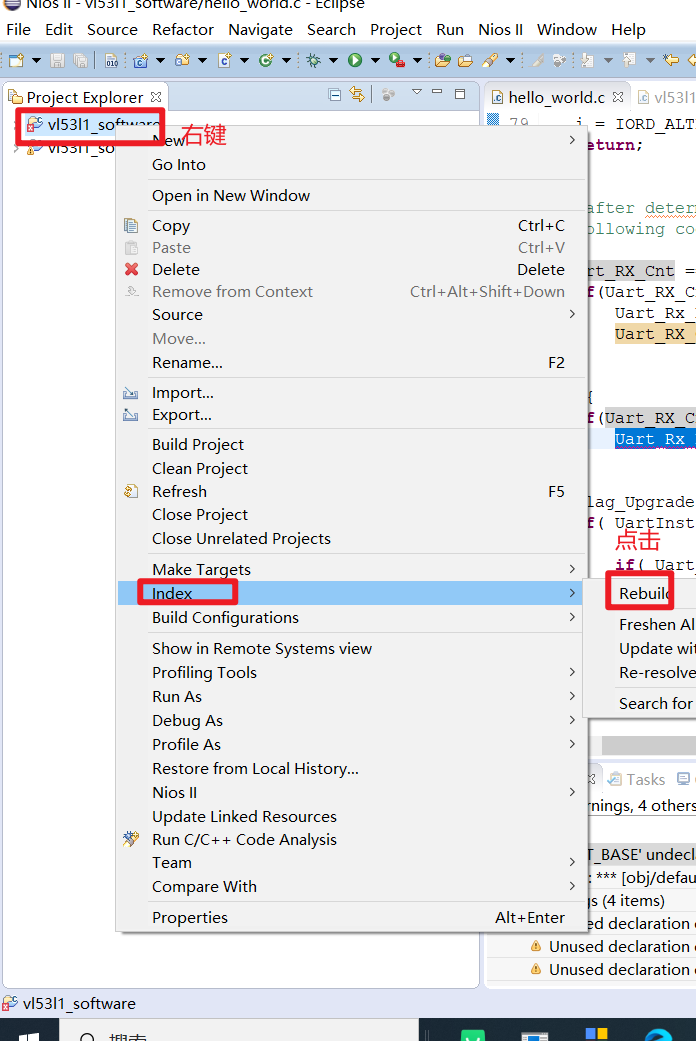

1、[nios ii EDS中出现Type 'xxxx_base' could not be resolved的解决方法]

明明添加system.h文件也能链接进去,但是就是代码就是报错

'UART_MCU_BASE' could not be resolved解决方法:

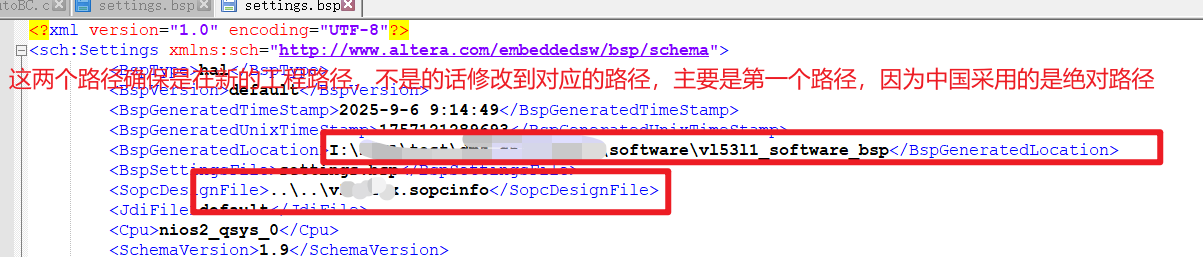

2、迁移quartus ii和nios工程时,nios工程链接到原来工程路径下的问题解决方法,软件版本是17.1。

第一步:

工程目录下打开setting.bsp文件:xx:\xx\xx\software\vl53l1_software_bsp路径下修改setting.bsp文件

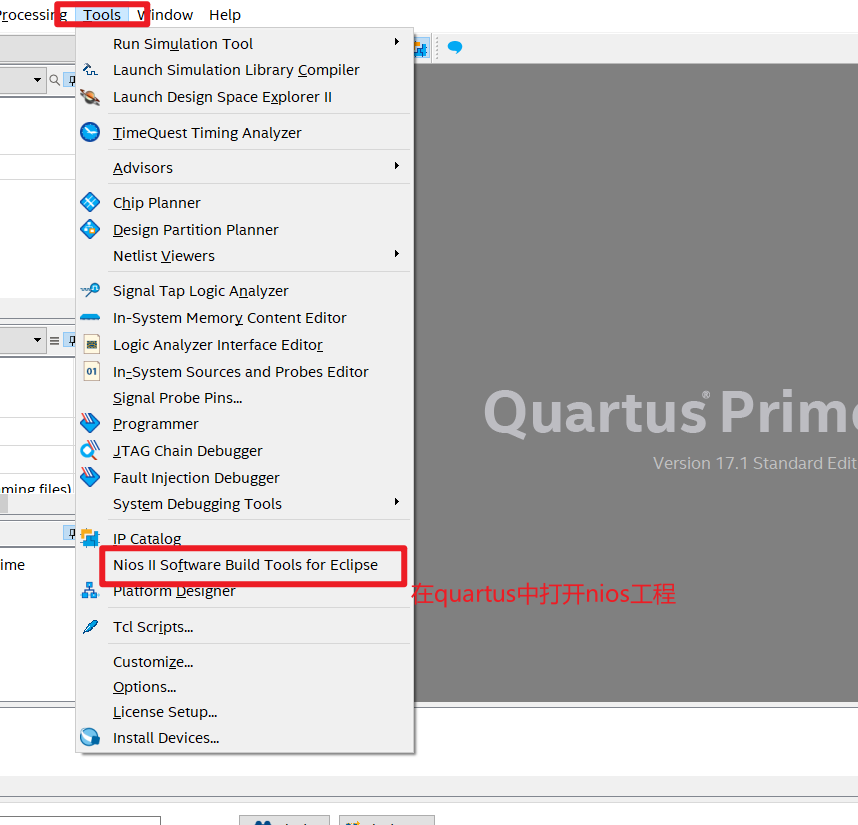

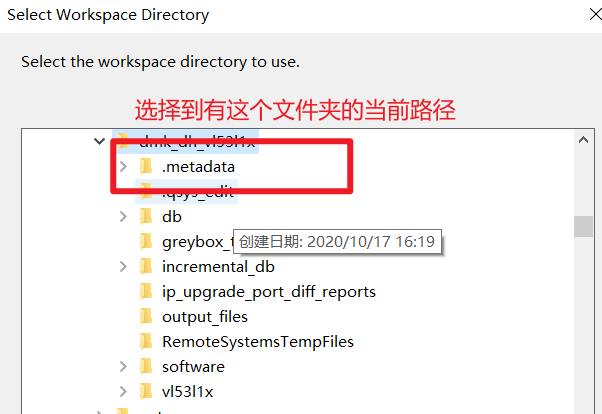

第二步:打开quartus工程。然后再打开nios工程。

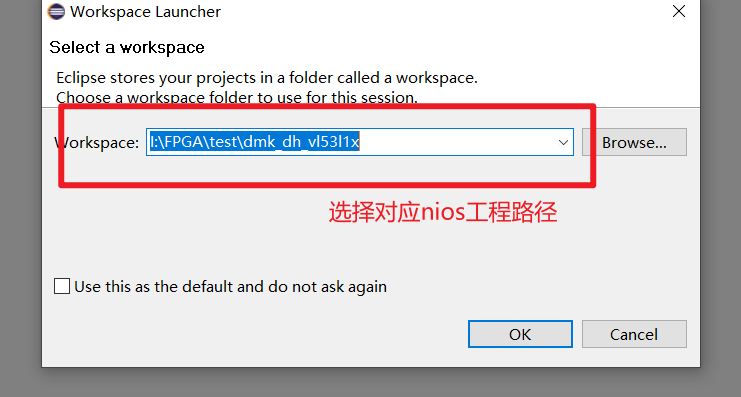

路径选择大奥.metadata文件夹路径下,点击确定,再点击ok。即可答案开nios工程

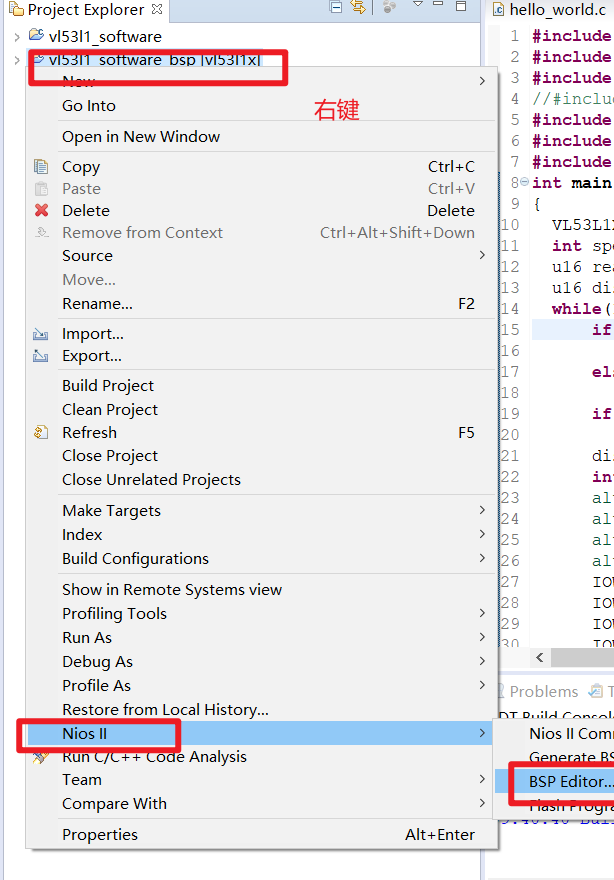

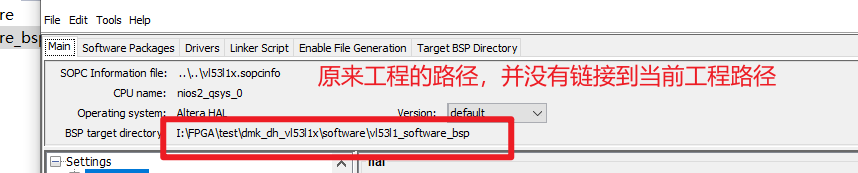

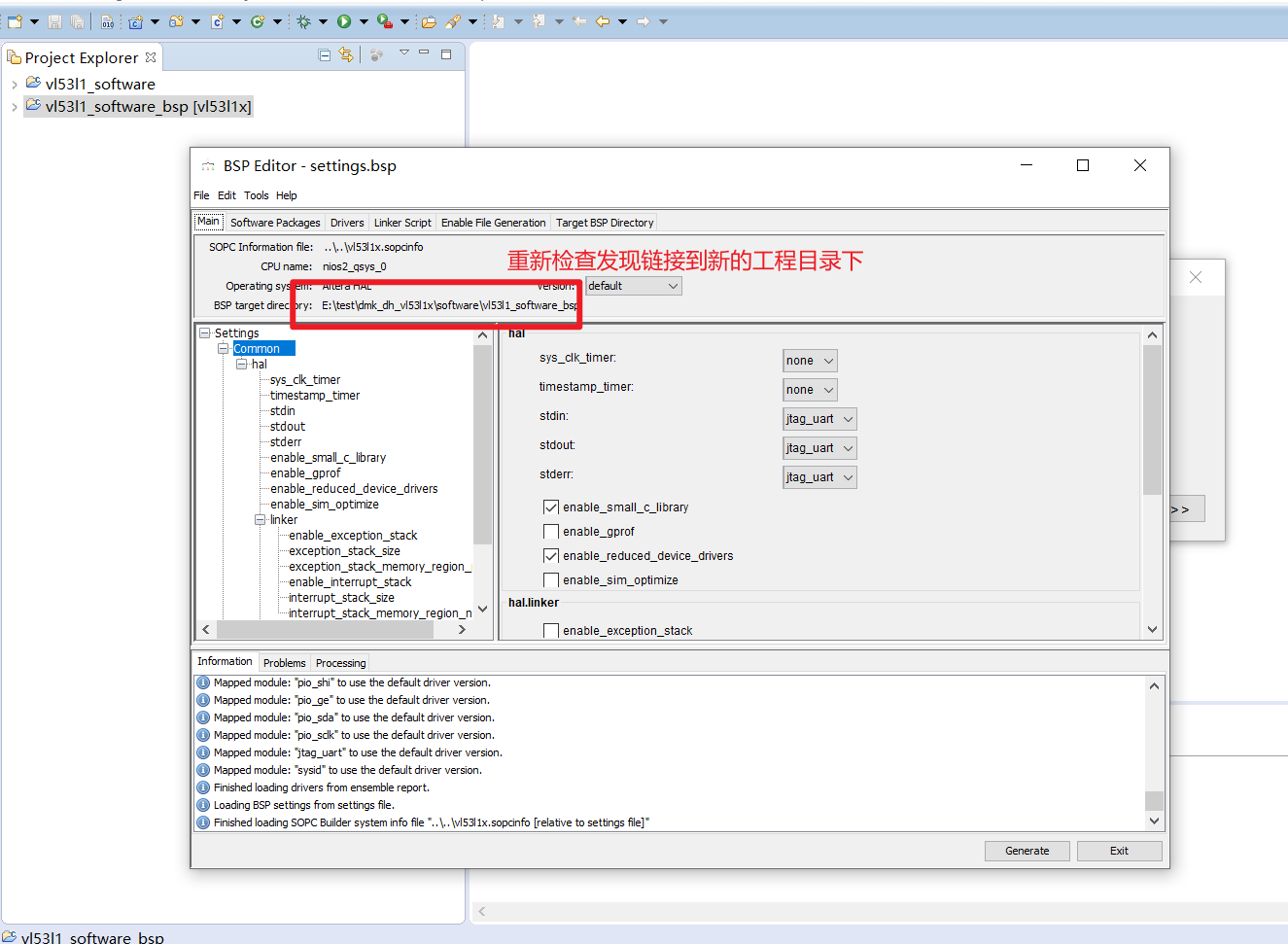

打开nios工程后检查nios链接的路径,发现还是原来旧工程的路径:

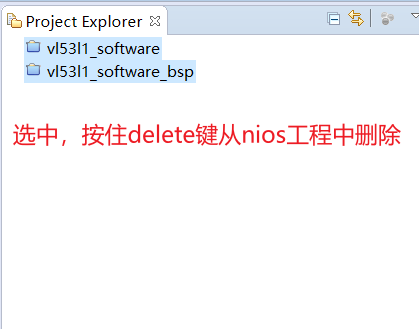

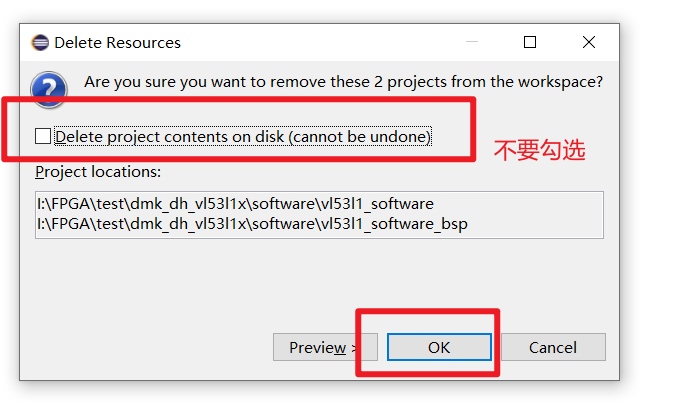

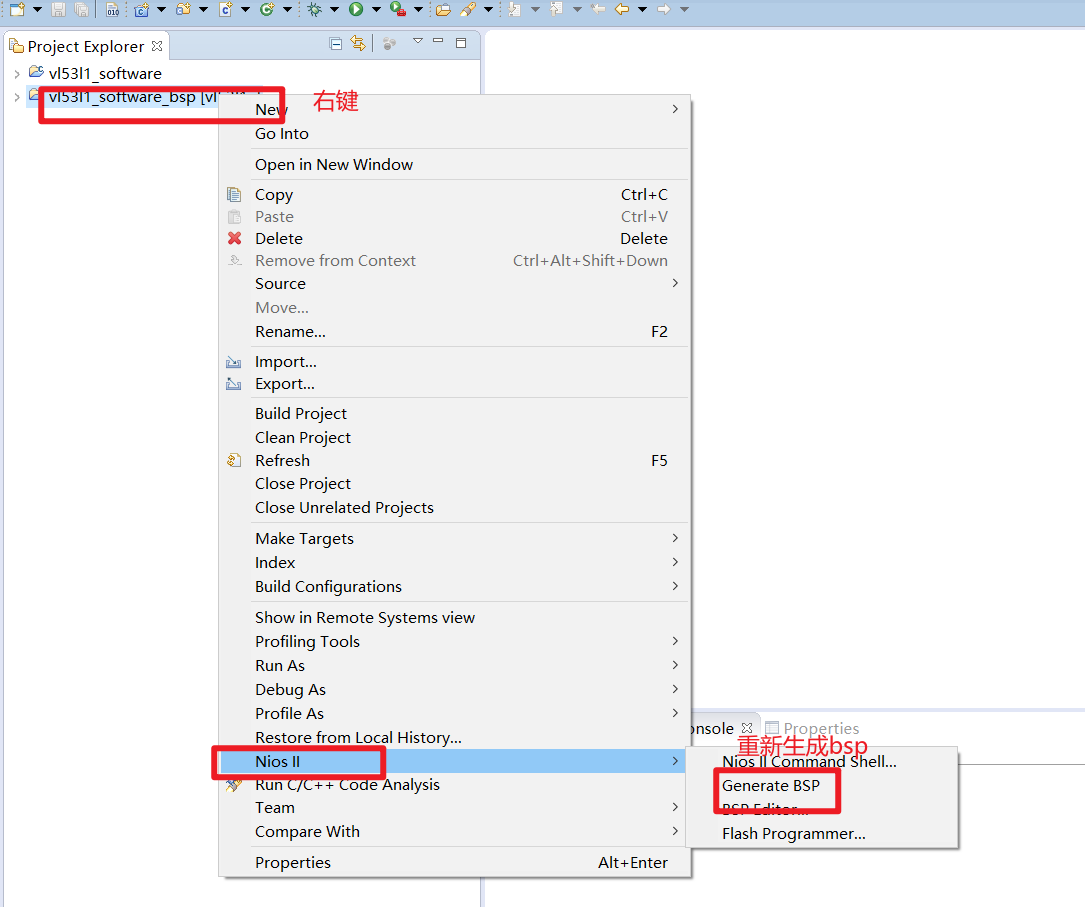

解决方法:

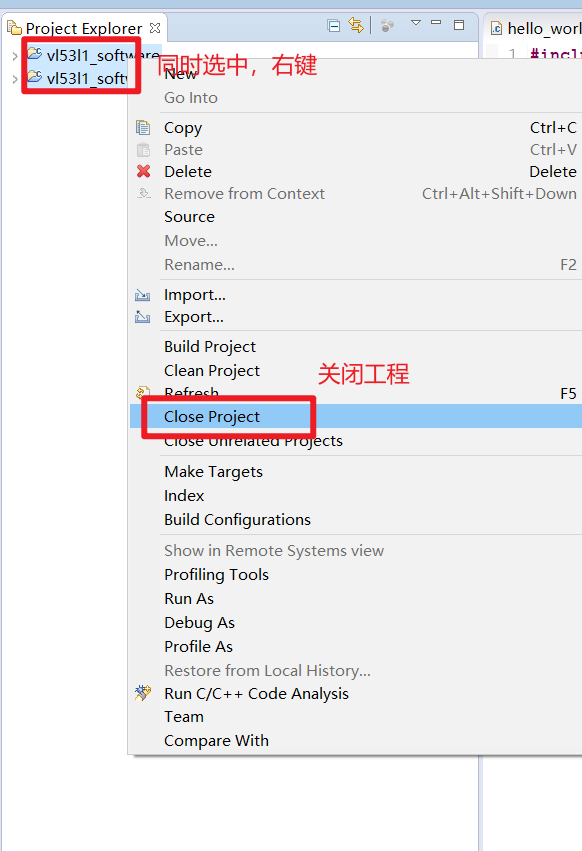

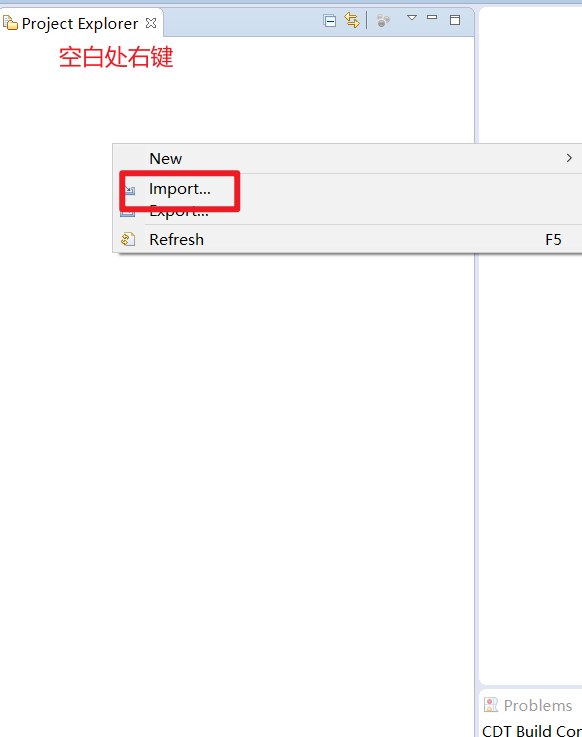

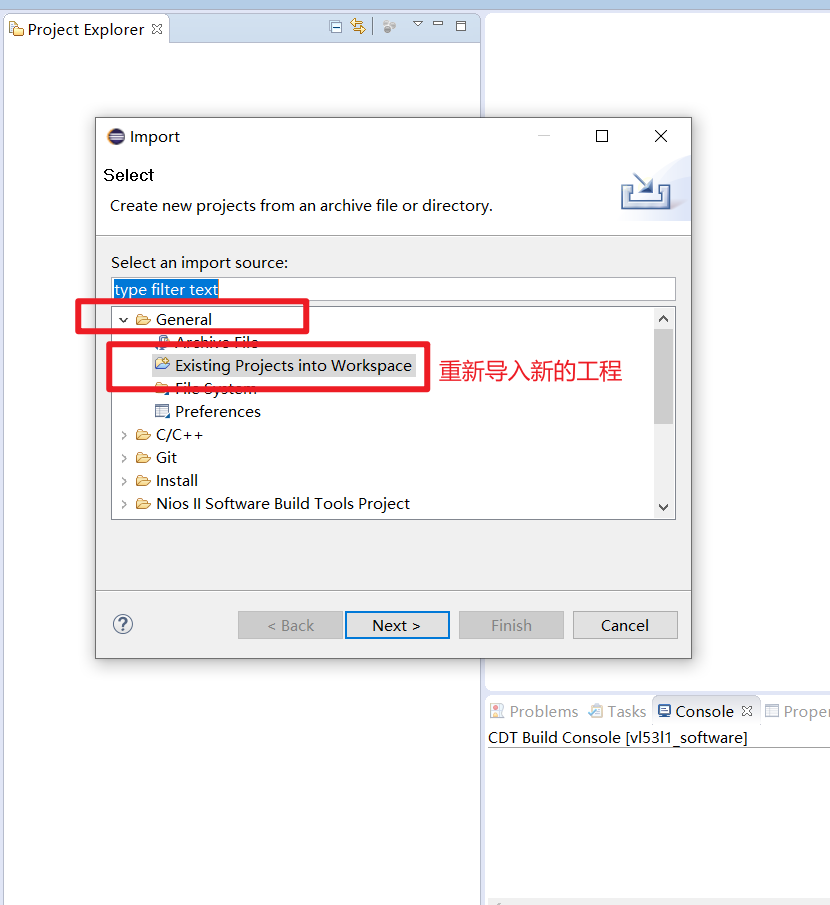

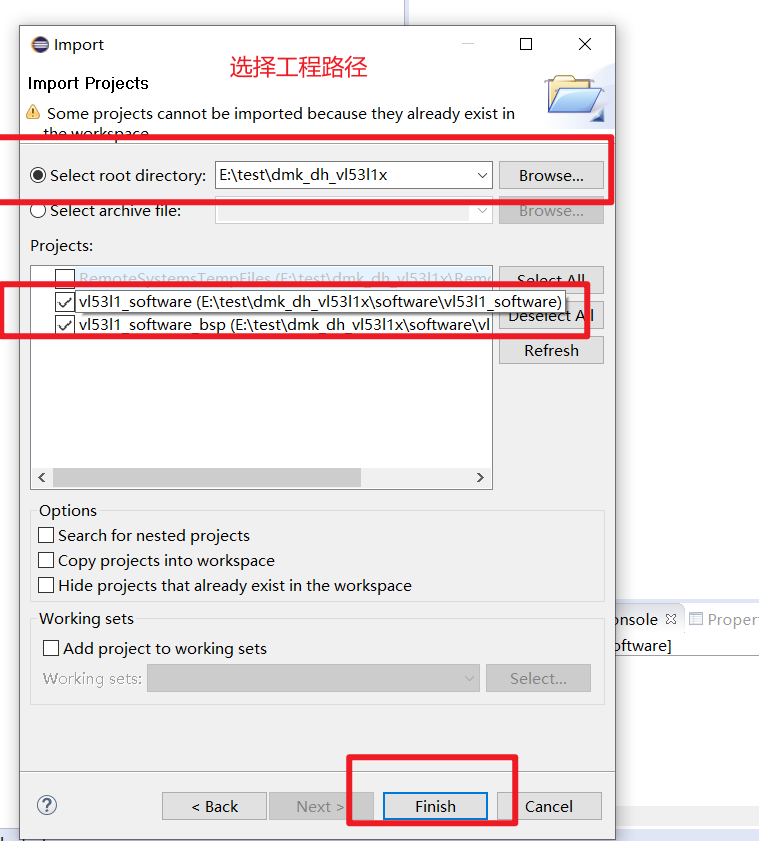

重新导入新的工程,点击next

检查路径是否正确:

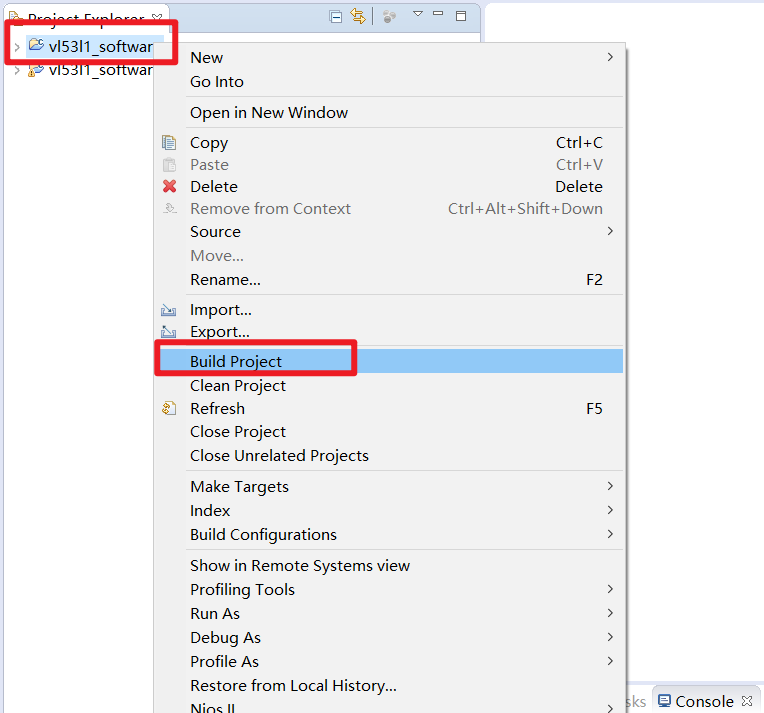

最后重新编一下工程即可,到此工程移植结束。

c

---晓凡 2025年9月于南宁书