一、OCP 原则(开闭原则)

对代码扩展是开放的,允许通过新增代码来扩展功能;对代码的修改是关闭的,尽量避免直接修改已有稳定运行的代码,以此保障代码的稳定性与可维护性。

二、中断处理

(一)中断函数注册机制

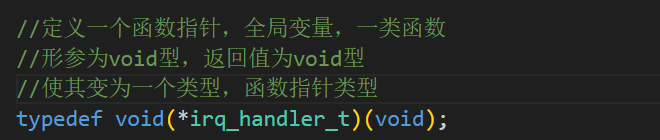

通过 typedef 定义函数指针类型 irq_handler,用于统一中断处理函数的格式(无参数、无返回值)。

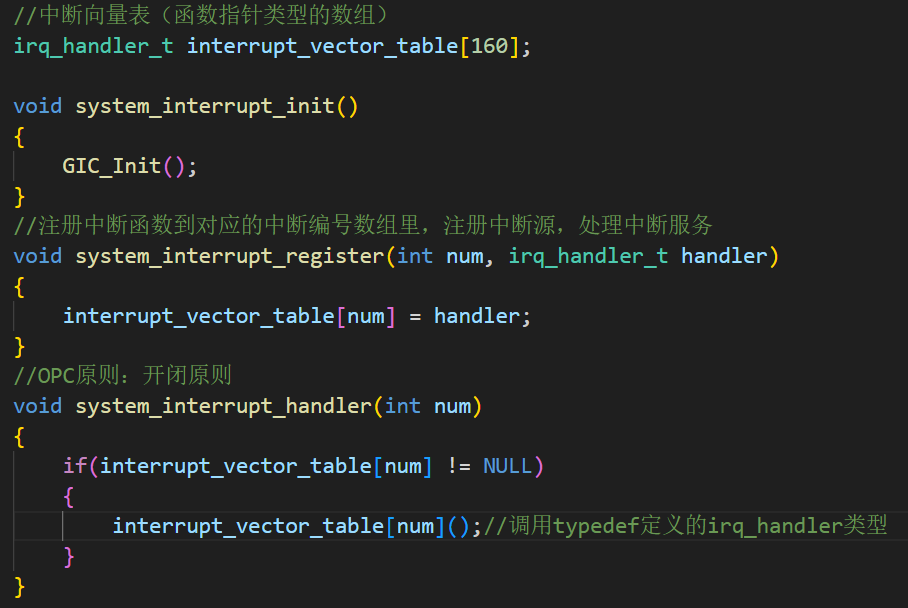

定义中断向量表 interrupt_vector_table,存储不同中断源对应的处理函数。

提供 system_register_irq 函数,实现中断源与处理函数的注册关联,遵循 OCP 原则,方便新增中断处理时,仅需注册而无需修改已有代码。

system_interrupt_handler 函数通过中断号从向量表中调用对应的处理函数,完成中断响应。

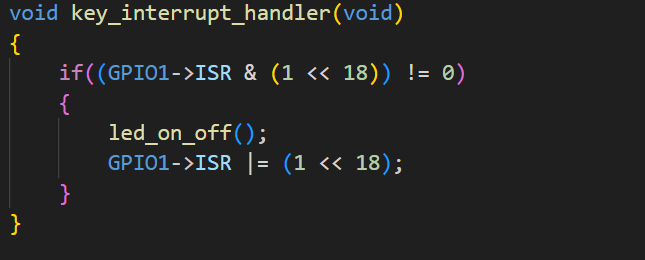

(二)示例:按键中断

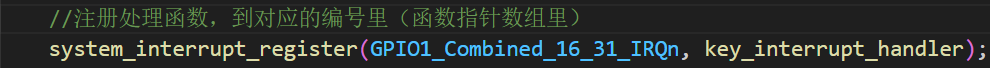

注册按键对应的中断源 GPIO1_Combined_16_31_IRQn 与处理函数 key_interrupt_handler。

在 key_interrupt_handler 中,检测 GPIO1 的中断状态寄存器(ISR),若对应按键中断标志置位,执行 led_nor 操作并清除中断标志。

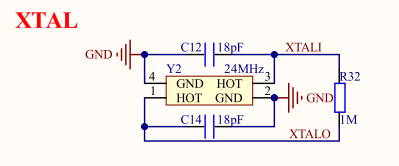

三、时钟系统

(一)时钟生成核心组件

- PLL(锁相环电路):实现倍频功能,公式为 Fout=Fin×n(Fin 为输入频率,n 为倍频系数)。

- Prescale(预分频器):实现分频功能,公式为 Fout=Fin/m(m 为分频系数)。

- PFD(相位分数分频器):结合倍频与分频,公式为 Fout=(Fin×n)/m,可分配n,m的大小(即分数小于零或者大于零),实现倍频或分频。

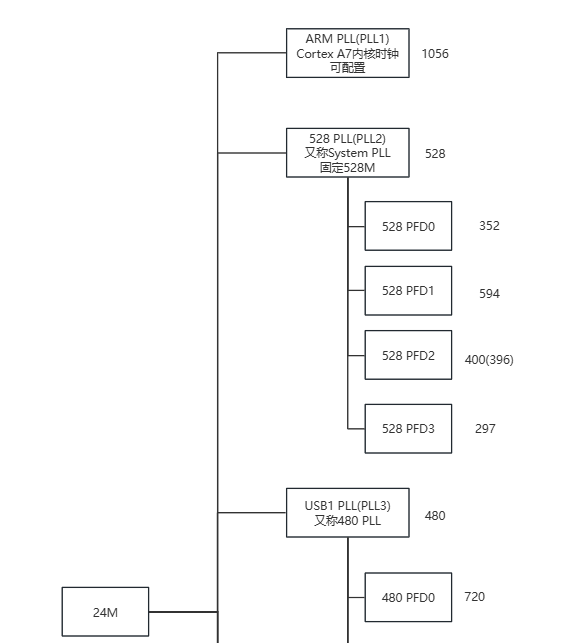

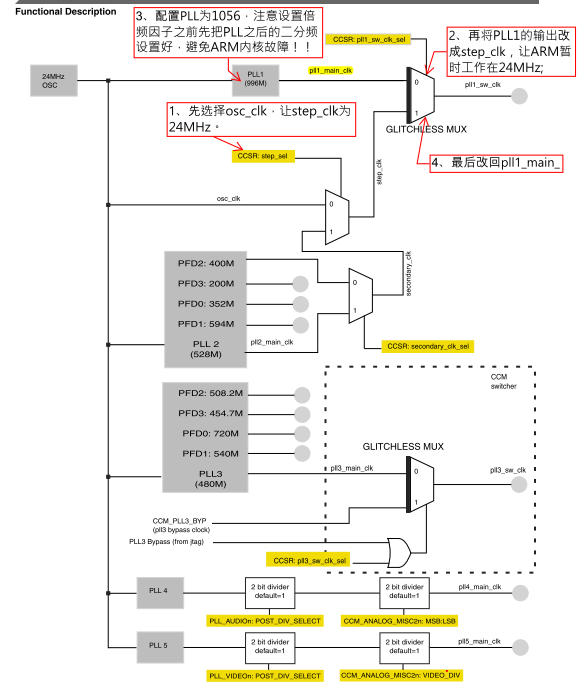

(二)IMX6ULL 中的 PLL

IMX6ULL 有多个 PLL 用于不同模块时钟供给,如 ARM PLL(PLL1)为 Cortex - A7 内核提供时钟,528 PLL(PLL2)作为系统 PLL,USB1 PLL(PLL3)用于 USB 模块等。

(三)时钟配置步骤

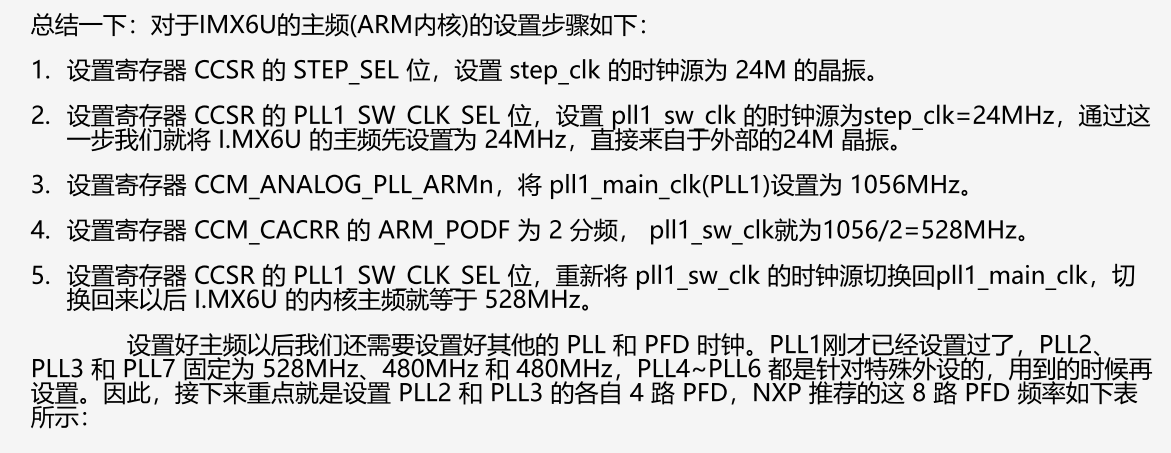

1. PLL 配置(以 PLL1 为例)

修改 PLL1 前先将内核时钟置为 24MHz,是为避免切换时钟时因时钟不稳定导致 ARM 内核停止工作。具体步骤:

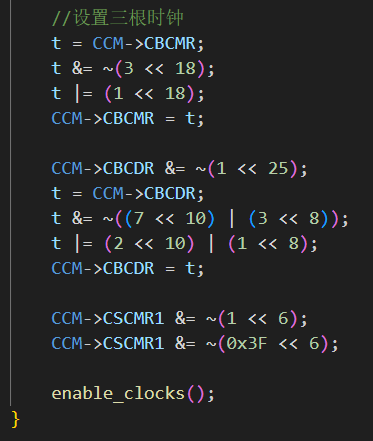

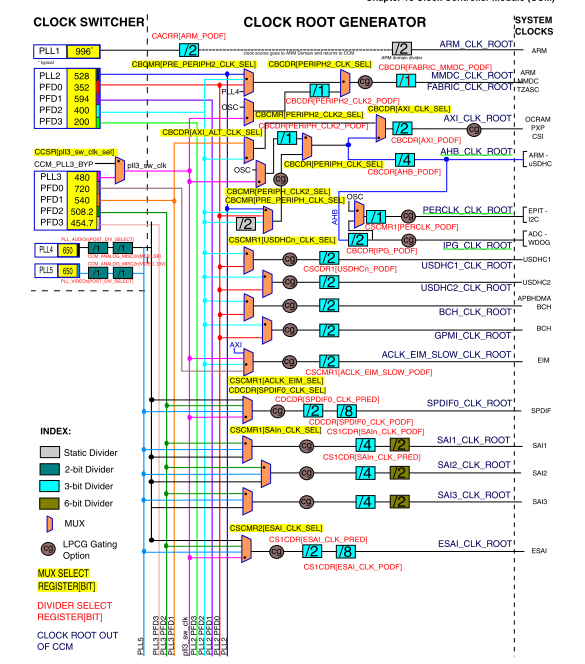

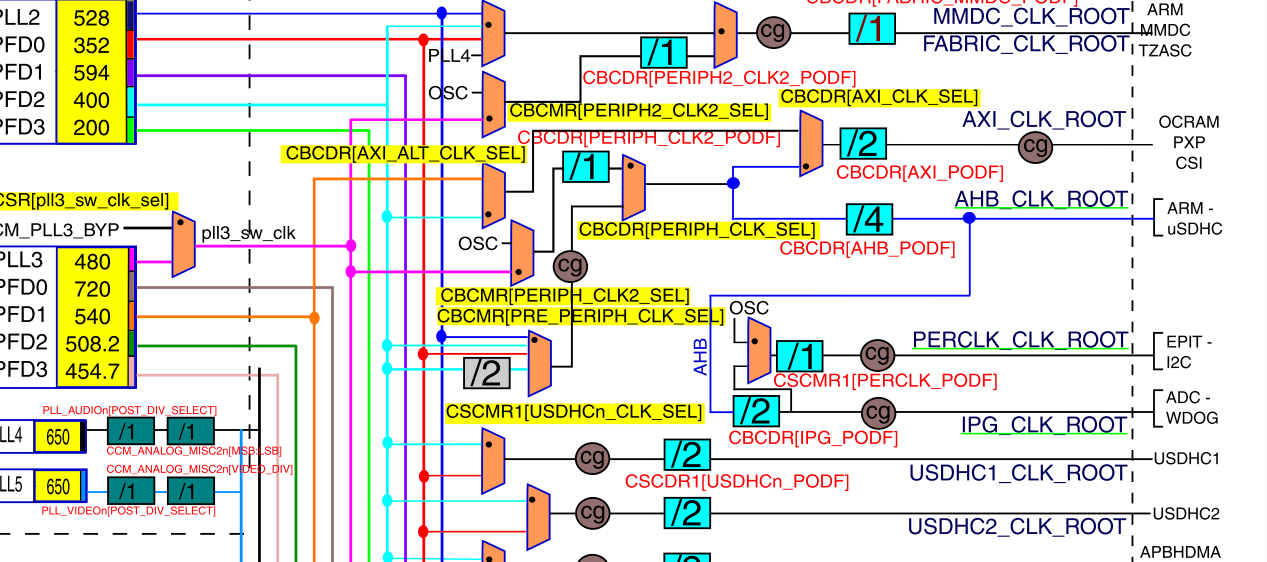

2. 时钟生成树(CLOCK ROOT GENERATOR)配置

分别配置关键时钟根:

- AHB_CLK_ROOT :例如选择 PLL2 PFD02 作为时钟源,通过寄存器

CCM_CBCMR配置时钟源选择位;利用CCM_CBCDR的AHB_PODF进行三分频,将 396MHz 时钟分频为 132MHz。 - IPG_CLK_ROOT:对 AHB 时钟进行二分频,配置为 66MHz。

- PERCLK_CLK_ROOT:保持一分频,时钟频率为 66MHz,为相关外设提供时钟。