接下来几讲,将仔细介绍Xilinx官方提供的应用说明文档xapp524,该文档提供一个7系器件简单构建处理ADC输出的LVDS接口的参考设计,后续如果使用7系器件进行LVDS接口的处理,可以在该参考设计的基础上进行修改;

介绍:

现在的高速ADC具有8位、10位、12位、14位、16位等分辨率,且单个封装封装中可能包含1个或多个数据通道,

ADC的LVDS接口,一般有:

一对差分比特时钟,用于采样数据通道,

一对差分帧时钟,用于标志哪些数据组成一个完整数据,

一对或多对差分数据信号,关于其中哪些数据信号携带哪个通道的数据,数据通道和数据信号线的关系,则是需要根据对应ADC的数据手册详细对照,

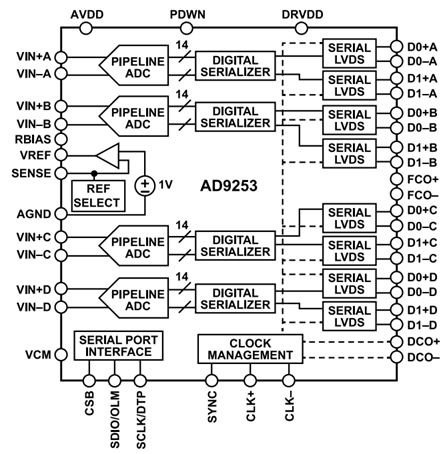

下图是ad9253的框图,接下来7系参考设计介绍完毕后,我们就在7系参考设计的基础上,对ad9253这个adc的lvds接口进行处理,进行仿真验证,

从框图中可以看到,这个ADC的管脚主要分为几种,

一是电源供电接口,二是时钟接口和一些必要的外围控制接口或是信号输入接口,三是低速的串行接口如IIC或是SPI接口,四是框图右侧的高速LVDS接口,

我们在使用一个ADC时,硬件工程师会把电源时钟外围控制等都处理好,FPGA工程师主要聚焦在低速串行接口和高速的LVDS接口,低速串行接口主要用于配置ADC内部的寄存器,用于初始化和控制ADC,需要配合数据手册提供的寄存器表使用,还可以更改LVDS接口的输出模式,

本系列课程,主要聚焦于对于LVDS接口的数据解析处理,至于驱动ADC的低速串口读写寄存器的实现,可能有时会省略;

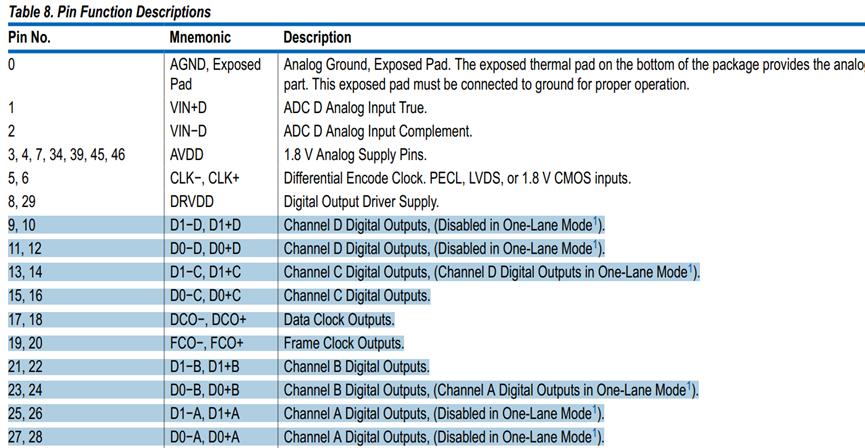

可以看到上图中选中部分为LVDS接口,

其中DCO+/DCO-,是高速的差分比特时钟,

FCO+/FCO-,是差分帧时钟,

D0-A/ D0+A / D1-A / D1+A,是通道A的差分输出,

D0-B/ D0+B / D1-B / D1+B,是通道B的差分输出,

D0-C/ D0+C / D1-C/ D1+C,是通道C的差分输出,

D0-D/ D0+D / D1-D / D1+D,是通道D的差分输出,

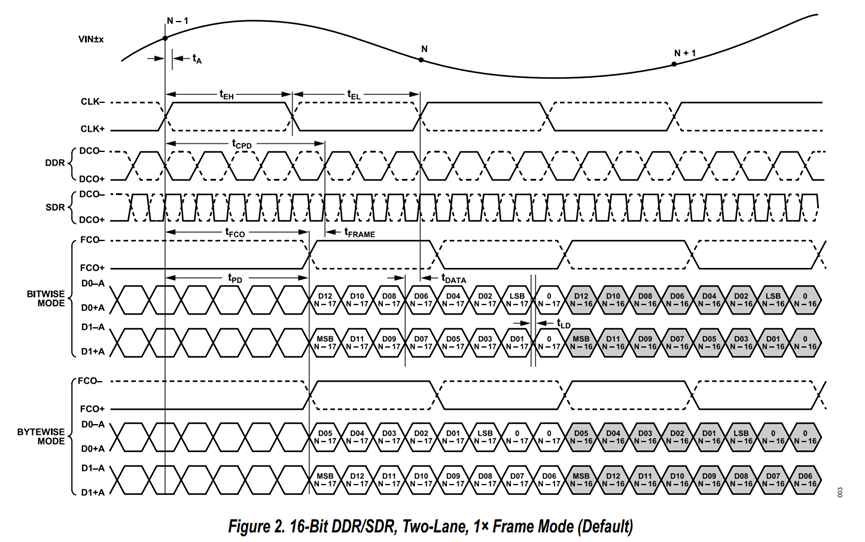

下图为ad9253一个模式的LVDS的时序图,后续使用时再详细讲解;

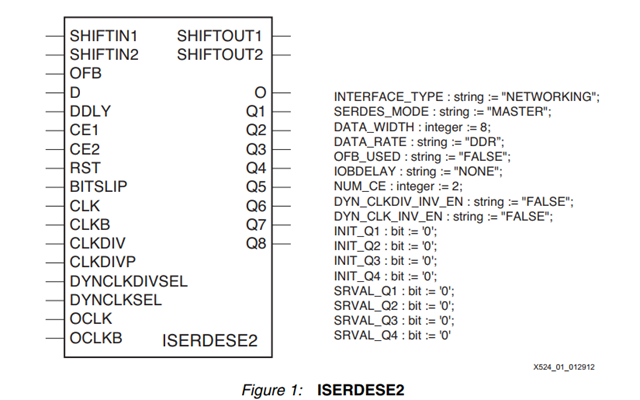

7系FPGA资源:

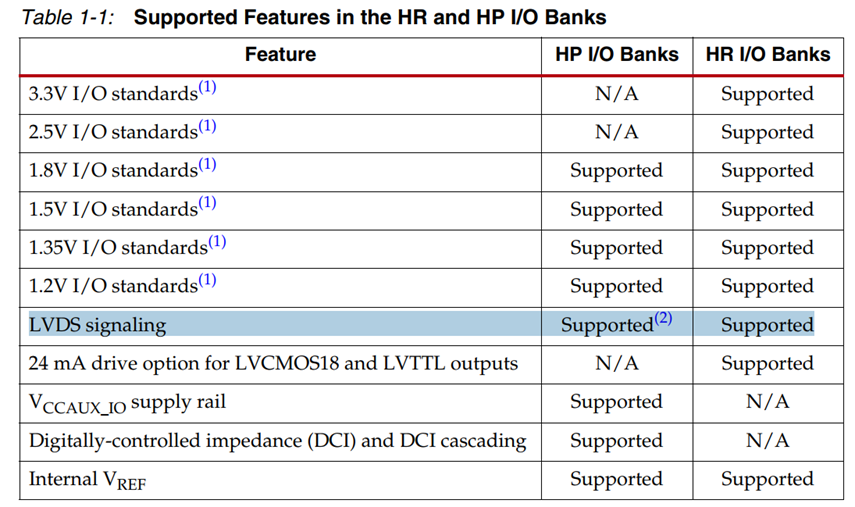

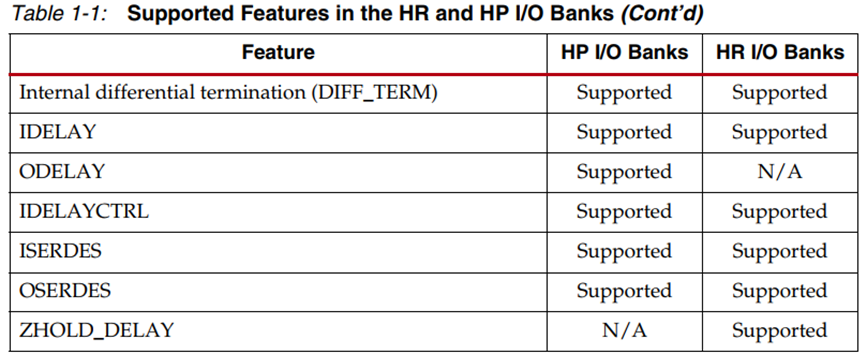

7系FPGA有HR IO bank ,HP IO bank,对于ADC接口,ISERDESE2和IDELAYE2在HR

HP bank中都可以使用,

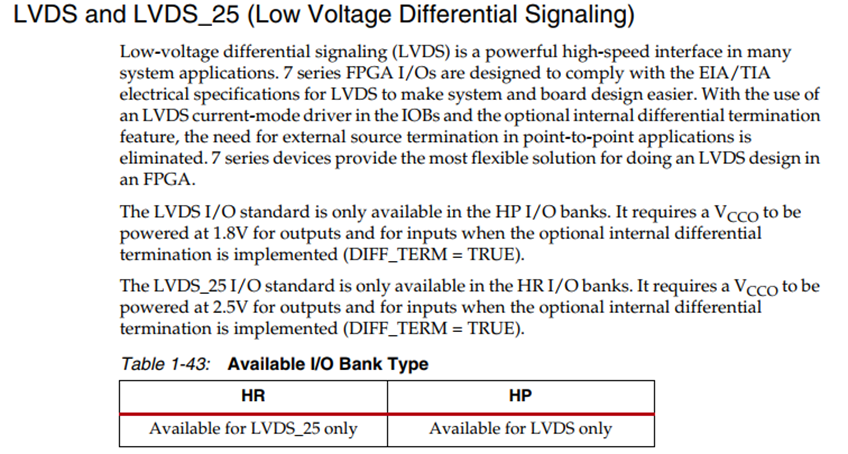

其中两种bank支持的电压标准不同,HR IO bank支持LVDS 2.5V IO,HP支持1.8V,这里的2.5和1.8指bank的VCCO电压,

7系bank支持情况:

两种bank,都支持LVDS接口,且都支持IDELAY和ISERDES,

关于LVDS电平标准,从上图ug471段落中可以看出,HR bank只支持VCCO为2.5V的LVDS_25的电平标准,HP bank只支持VCCO为1.8V的LVDS电平标准;

其他类型的差分接口,也需要根据支持的电平值判断;

本文章由威三学社出品

对课程感兴趣可以私信联系