ARM CoreSight™ SoC-400

调试访问端口(Debug Access Port, DAP)说明

具体寄存器字段、位定义及长段原文请参考官方英文手册。

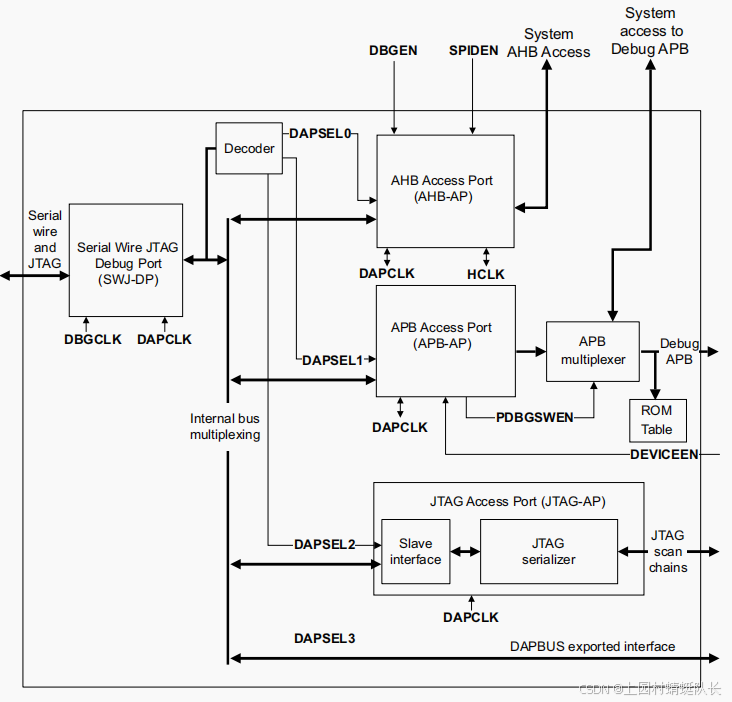

1 DAP 概述

Debug Access Port (DAP) 是 SoC 调试系统的核心组成部分,用于将外部调试器连接到片上资源。

关键特性:

- 统一的调试入口,可通过 JTAG 或 Serial Wire Debug (SWD) 接口。

- 由 调试端口(DP) 和一个或多个 访问端口(AP) 组成。

- 支持 AXI、AHB、APB 等多种 AMBA 总线访问。

- 可跨多电源域、异步时钟域,实现低功耗设计。

典型应用:

- 在芯片上下载/调试程序

- 访问片上存储器和外设寄存器

- 系统级跟踪和断点

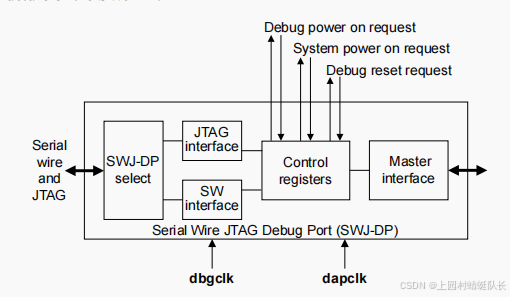

2 SWJ-DP(Serial Wire / JTAG Debug Port)

SWJ-DP 既可以作为 JTAG-DP,也可以作为 SW-DP 工作,并能自动检测和切换模式。

主要功能:

- 模式切换:上电后可通过特定序列在 JTAG 与 SWD 之间切换。

- 可配置 IR 长度:4 位或 8 位 JTAG 指令寄存器。

- 电源管理握手 :提供 cdbgpwrupreq、csyspwrupreq 等信号,与系统电源域协同。

关键接口:

| 信号 | 描述 |

|---|---|

| SWCLK / TCK | 时钟输入(SWD 或 JTAG) |

| SWDIO / TMS | 数据输入/输出或模式选择 |

| TDI | JTAG 输入 |

| TDO | JTAG 输出 |

| nRESET | 目标芯片复位控制 |

| nTRST | 可选的 JTAG 复位信号 |

2. 1架构与组成

SWJ-DP 实际上是一个调试访问端口(DAP,Debug Access Port)的变体,通常包括以下子模块:

-

DP 控制逻辑

- 管理调试器访问状态。

- 支持 SWD 和 JTAG 切换。

- 控制访问优先级和锁定状态。

-

寄存器接口

- CTRL/STAT 寄存器:DP 的全局控制和状态监控。

- SELECT 寄存器:选择要访问的 AP(Access Port)和 bank。

- RDBUFF 寄存器:读缓冲,保证连续访问一致性。

-

AP 访问桥

- 支持 AHB/APB 互连访问。

- 提供对 SoC 内存和外设的访问能力。

2.3. 关键寄存器

以下是 SWJ-DP 常用寄存器及功能描述:

| 寄存器 | 偏移 | 功能说明 |

|---|---|---|

| DPIDR | 0x00 | 设备 ID 寄存器,包含 SWJ-DP 的版本信息 |

| CTRL/STAT | 0x04 | 控制和状态寄存器,管理 DP 锁定、错误标志、调试器占用 |

| SELECT | 0x08 | 选择当前要访问的 AP 和 bank |

| RDBUFF | 0x0C | 读缓冲寄存器,确保多次访问数据一致性 |

| RESEND / ABORT | 0x0C/0x10 | 中止操作或重新发送请求 |

CTRL/STAT 寄存器字段示例:

| 位 | 名称 | 功能 |

|---|---|---|

| 0 | CDBGPWRUPREQ | 请求调试电源启动 |

| 1 | CDBGPWRUPACK | 调试电源启动确认 |

| 2 | CSYSPWRUPREQ | 系统电源请求 |

| 3 | CSYSPWRUPACK | 系统电源启动确认 |

| 4 | MASKLANE | 屏蔽访问线错误 |

| 5 | STICKYERR | 错误标志,保持直至清除 |

| 6 | ORUNERR | 总线访问超时错误 |

| 7 | WDATAERR | 写数据错误 |

2.4. 协议接口

SWJ-DP 支持两种访问协议:

2.4.1 SWD(Serial Wire Debug)

- 仅需两条信号线:SWCLK 和 SWDIO。

- 支持单调调试访问,适合低引脚设计。

- 数据传输使用序列化读写请求,DP 控制访问 AP。

.2 4.2 JTAG

- 使用标准 4-5 pin 接口:TCK、TMS、TDI、TDO、可选 nTRST。

- 提供 TAP 状态机控制访问。

- 适合传统调试工具和 FPGA/JTAG 仿真场景。

2.5. 调试访问流程

-

初始化 DP

- 配置 CTRL/STAT,确认调试电源开启。

- 检查 DP 锁定状态,确保调试器可以访问。

-

选择 AP 和 bank

- 写 SELECT 寄存器,确定要访问的外设或内存空间。

-

发起读写操作

- 写入数据或读缓冲寄存器。

- 监控 STICKYERR、ORUNERR 等错误标志。

-

完成访问

- 使用 ABORT 或 RESEND 清理状态。

- 可释放 DP 以允许其他调试器访问。

2.6. 注意事项

- SWJ-DP 可在 SWD 和 JTAG 模式间切换,但切换前必须确保总线处于空闲状态。

- 错误标志必须在后续访问前清除,否则会阻塞访问。

- 调试电源和系统电源状态必须正确设置,否则 AP 访问可能失败。

- SWJ-DP 的引脚与目标芯片设计相关,需要注意拉高/拉低电平配置。

3 DAPBUS Interconnect

DAPBUS 是 DP 与各 AP 之间的内部互连总线。

- 特点:组合逻辑互连、单电源域。

- 配置:支持 1--32 个主接口,易于扩展。

- 用途:实现来自不同 AP 的并发访问和仲裁。

4 DAPBUS Asynchronous Bridge

- 作用:在两个异步时钟域之间传输调试数据。

- 低功耗接口 (LPI):支持跨电源域的电源管理。

- 配置模式:可作为纯主接口、纯从接口或完整桥接模块。

5 DAPBUS Synchronous Bridge

- 功能:在不同但同步的时钟域之间传输数据。

- 特点 :

- 支持 1:1、1:n、n:1 等同步模式。

- 可选寄存器切片(前向、反向或完整)以简化时序收敛。

- 可选低功耗接口 (LPI)。

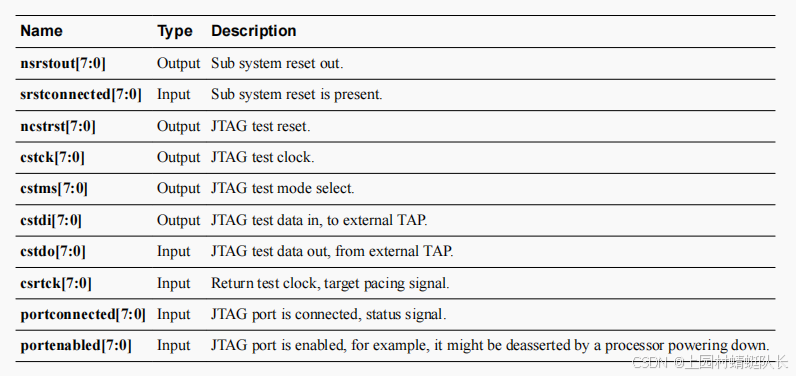

6 JTAG-AP

JTAG Access Port 提供 JTAG 主接口,用于驱动芯片内部 JTAG 链。

- 允许调试器直接访问多个 TAP 控制器。

- 支持多路并行 JTAG 端口。

- 常见信号包括 cstck、cstms、cstdo、cstdi 等。

7 AXI-AP

AXI Access Port 是一个 AXI4 主接口,可让调试器发起 AXI 事务以访问系统存储器。

主要特性:

- 32/64 位地址与数据宽度可配置。

- 支持 ACE-Lite 事务(ReadOnce、WriteUnique 等)。

- 仅支持对齐访问,不支持乱序和写数据交织。

AXI-AP (AXI Access Port) 是 CoreSight Debug Access Port (DAP) 的一种访问端口,用于让外部调试器通过 AXI4 总线访问片上系统存储器和外设。

它遵循 ARM ADIv5 规范,并实现 AMBA AXI4 主接口。

7.1. 主要功能

- 调试访问

允许外部调试工具在处理器停止或运行时直接读写系统内存、外设寄存器。 - 宽总线支持

32 位或 64 位地址宽度可配置;数据总线支持 32、64、128 位等实现。 - 非侵入式操作

通过 DAP 访问系统总线,不干扰正常的处理器执行流程。 - 多电源域/时钟域

可与 DAPBUS 异步桥或低功耗接口配合,实现跨电源域调试。

7.2. 接口信号示例

| 信号 | 方向 | 说明 |

|---|---|---|

| ACLK | Input | AXI 总线时钟 |

| ARESETn | Input | AXI 总线复位,低有效 |

| AWADDR | Output | 写地址总线 |

| AWPROT | Output | 写保护属性(安全/非安全、特权/用户等) |

| AWVALID | Output | 写地址有效指示 |

| WDATA | Output | 写数据总线 |

| WSTRB | Output | 写字节选通 |

| WVALID | Output | 写数据有效指示 |

| BREADY | Output | 写响应准备 |

| ARADDR | Output | 读地址总线 |

| ARPROT | Output | 读保护属性 |

| ARVALID | Output | 读地址有效指示 |

| RREADY | Output | 读数据准备 |

| RDATA | Input | 读数据 |

| RRESP | Input | 读响应 |

注:具体位宽和信号集合可能因实现而异,上表为典型 AXI4-Lite/AXI4 接口示例。

7.3. 事务类型与限制

- 支持的访问 :

- 单次读写(Single Transfer)

- 增量型突发传输(Incrementing Burst)

- 不支持的访问 :

- 乱序(Out-of-Order)

- 未对齐访问

- 数据交织写(Write Interleave)

7.4. 调试寄存器概览

AXI-AP 通过一组内存映射寄存器与 DAP 通信。典型寄存器包括:

| 寄存器 | 地址偏移 | 描述 |

|---|---|---|

| CSW | 0x00 | 控制与状态字,用于设置访问大小、自动增量等 |

| TAR | 0x04 | 传输地址寄存器,指定访问目标地址 |

| DRW | 0x0C | 数据读写寄存器 |

| CFG | 0xF4 | 配置寄存器,用于选择 AXI 属性、域等 |

具体寄存器字段请参考对应的 SoC 或 IP 提供商文档。

--

7.5. 调试场景示例

-

内存读取

- 调试器写 TAR 为目标地址。

- 设置 CSW 访问大小(如 32 位)并触发读操作。

- 从 DRW 读取数据。

-

内存写入

- 写 TAR 为目标地址。

- 向 DRW 写入数据,DAP 自动经 AXI 总线完成写事务。

7.6. 设计注意事项

- 时钟域跨越:若 DAP 和系统 AXI 总线位于不同的时钟域,需要使用异步桥。

- 安全属性:利用 AXI PROT 信号区分安全与非安全访问,以配合 TrustZone。

- 性能影响:在大规模调试访问中可能影响系统带宽,应合理规划。

8 AHB-AP

AHB Access Port 作为 AHB-Lite 主接口工作。

- 兼容 AMBA 2 AHB 和 TrustZone 扩展。

- 限制:不支持突发、排他或非对齐访问。

- 典型用途:访问共享内存、外设寄存器。

AHB-AP (AHB Access Port) 是 CoreSight DAP(Debug Access Port)的一种访问端口,用于让外部调试器通过 AMBA AHB-Lite 总线访问 SoC 的系统资源。

8.1. 功能概述

- 外部调试访问

允许调试器在处理器暂停或运行时直接读写片上存储器、外设寄存器。 - 符合 ADIv5 规范

与 ARM Debug Interface v5 配套使用。 - 主机角色

作为 AHB-Lite 主设备发起读写事务,而不是被动从设备。 - 跨电源/时钟域

可与 DAPBUS 异步桥和低功耗接口 (LPI) 配合,适用于多电源域 SoC。

8.2. 接口信号示例

| 信号 | 方向 | 描述 |

|---|---|---|

| HCLK | Input | AHB 总线时钟 |

| HRESETn | Input | AHB 复位,低有效 |

| HADDR | Output | 地址总线(通常 32 位,可扩展) |

| HWDATA | Output | 写数据总线 |

| HRDATA | Input | 读数据总线 |

| HWRITE | Output | 传输方向:1 = 写,0 = 读 |

| HSIZE | Output | 访问大小(8/16/32 位) |

| HTRANS | Output | 传输类型(IDLE / NONSEQ) |

| HBURST | Output | 突发类型(AHB-AP 常用 SINGLE) |

| HPROT | Output | 保护属性(特权/用户、安全/非安全等) |

| HREADY | Input | 从设备准备就绪信号 |

| HRESP | Input | 从设备响应(OKAY/ERROR/RETRY/SPLIT) |

实际实现的位宽和信号集合可能因芯片而异,上表为典型 AHB-Lite 接口示例。

8.3. 访问能力与限制

- 支持的访问

- 单次读写(Single Transfer)

- 增量型突发(Incrementing Burst,通常限制为 4/8 beat)

- 限制

- 不支持非对齐访问

- 不支持排他访问(Exclusive Access)

- 不支持交织或乱序事务

8.4. 主要寄存器(通过 DAP 访问)

| 寄存器 | 偏移 | 描述 |

|---|---|---|

| CSW | 0x00 | Control/Status Word:设置访问大小、自动增量等 |

| TAR | 0x04 | Transfer Address Register:目标地址 |

| DRW | 0x0C | Data Read/Write:读写数据通道 |

| CFG | 0xF4 | Configuration:选择安全属性、调试域等 |

具体字段定义请参考对应 SoC 或 IP 提供商的文档。

8.5. 调试操作示例

内存读取

- 调试器写

TAR为目标地址。 - 配置

CSW(访问大小、是否自动递增)。 - 读取

DRW获取数据。

内存写入

- 调试器写

TAR为目标地址。 - 将数据写入

DRW,AHB-AP 自动发起写事务。

8.6. 设计注意事项

- 时钟域跨越

如 DAP 与系统 AHB 时钟不同,需搭配异步桥以确保数据可靠。 - 安全/特权属性

利用HPROT与 TrustZone 配合实现安全访问。 - 性能影响

大规模调试访问可能暂时占用总线带宽,需要在系统设计中考虑仲裁策略。

9 APB-AP

APB Access Port 负责访问 CoreSight 调试 APB 总线。

- 固定 32 位数据宽度。

- 支持 PADDR31 信号,用于区分外部调试器访问和片上调试软件访问。

APB-AP (APB Access Port) 是 ARM CoreSight DAP(Debug Access Port)的一种访问端口。

它提供 AMBA APB3 主接口 ,让外部调试器能够访问片上的 Debug APB 总线,用于控制和配置各种 CoreSight 组件(如 ETM、CTI、Funnel 等)。

9.1 功能概述

-

调试总线桥接

- 通过 DAP 将外部调试器与 SoC 内部的 APB 总线连接。

- 实现 CoreSight 模块的寄存器读写,而无需干扰处理器运行。

-

32 位固定数据宽度

- 读写事务均为单次 32 位传输。

- 访问简单、低延迟,适合寄存器级调试。

-

符合 ADIv5 规范

- 与其他 Access Port 一样通过标准 DAP 总线访问和配置。

9.2. 接口信号示例

| 信号 | 方向 | 描述 |

|---|---|---|

| PCLK | Input | APB 总线时钟 |

| PRESETn | Input | APB 总线复位,低有效 |

| PADDR | Output | 32 位地址总线 |

| PWDATA | Output | 32 位写数据总线 |

| PRDATA | Input | 32 位读数据总线 |

| PWRITE | Output | 1 = 写操作,0 = 读操作 |

| PSEL | Output | 片选信号 |

| PENABLE | Output | 访问阶段使能信号 |

| PREADY | Input | 从设备准备就绪 |

| PSLVERR | Input | 从设备错误指示 |

上表为标准 AMBA APB3 接口信号,具体位宽可随实现微调。

9.3. 访问流程

-

写访问

- 调试器向

TAR(Transfer Address Register)写入目标地址。 - 将数据写入

DRW(Data Read/Write),APB-AP 通过 APB 发起写事务。

- 调试器向

-

读访问

- 写入

TAR为目标寄存器地址。 - 读取

DRW获得从设备返回的数据。

- 写入

9.4. 主要寄存器(通过 DAP 访问)

| 寄存器 | 偏移 | 描述 |

|---|---|---|

| CSW | 0x00 | Control/Status Word:配置访问大小(固定 32 位)、自动增量等 |

| TAR | 0x04 | Transfer Address Register:目标寄存器地址 |

| DRW | 0x0C | Data Read/Write:实际数据读写通道 |

| CFG | 0xF4 | Configuration:配置安全属性、调试域等 |

具体字段与位定义请参考芯片或 IP 提供商的详细文档。

9.5. 特性与限制

- 固定 32 位数据宽度:不支持 8/16 位访问。

- 单周期访问:所有事务为单拍 (single transfer)。

- 调试器专用:常用于配置 ETM、CTI、TPIU、Funnel 等 CoreSight 模块。

9. 6. 设计与使用注意事项

- 低功耗设计

- APB-AP 可与 DAPBUS 异步桥搭配,在 SoC 分电源域时仍可访问。

- 安全属性

- 通过配置寄存器选择 Secure/Non-secure 访问,以配合 TrustZone 架构。

- 带宽与性能

- 由于 APB 本身为低带宽协议,适合配置寄存器而非大规模数据传输。