ADC接口:

许多ADC使用LVDS接口进行通信,使用一个或多个LVDS接口将数字数据传输给FPGA。

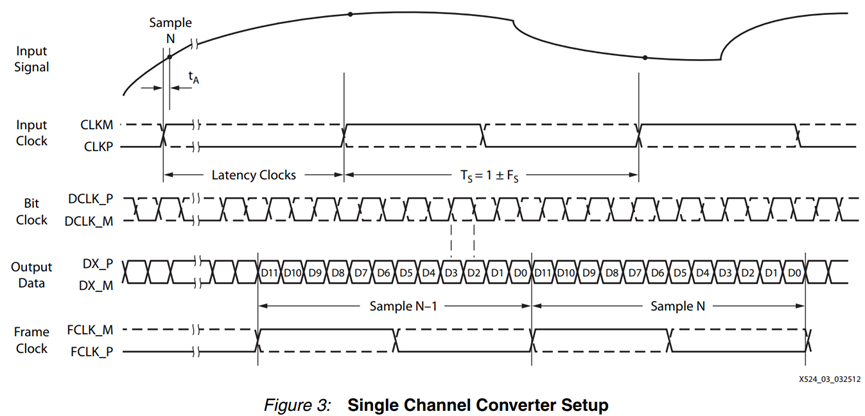

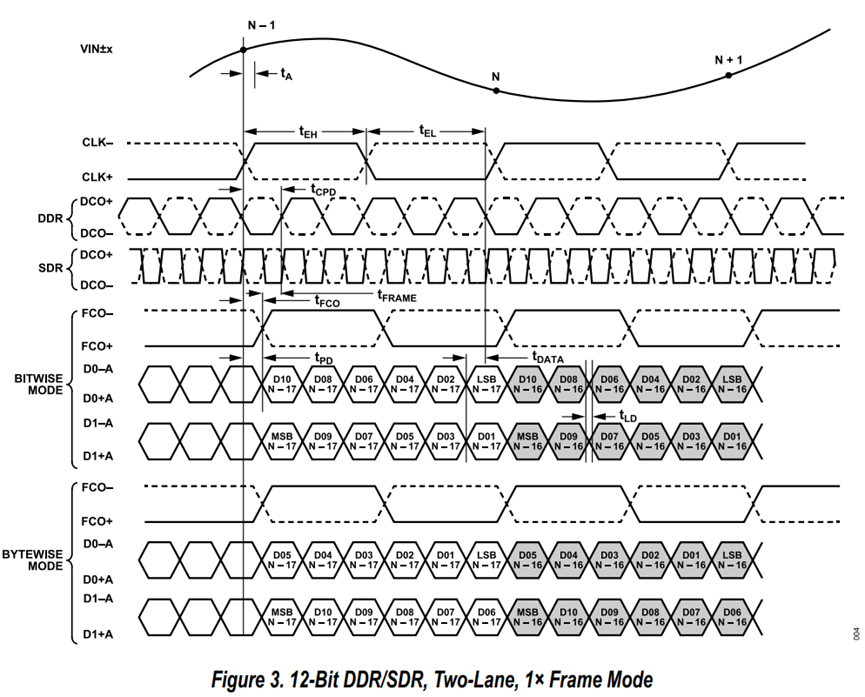

下图显示了模拟输入信号Input Signal、输入时钟Input Clock、位时钟Bit Clock、帧时钟Frame Clock、输出数据Output Data。

模拟信号在输入ADC后,经过一定延时转换为数字格式,并给到ADC输出端。其中下图模拟信号被转换为具有12位ADC分辨率的串行数据流从ADC输出端输出,与高速位时钟和用于同步的帧时钟一起提供给FPGA。

帧时钟FCLK,是ADC采样时钟的数字化和相移版本,也就是上图的用于采集Input signal输入信号的采样时钟Input Clock;

FCLK与串行数据相位对齐,一个采样时钟采样到的ADC串行化的12bit数据,都会放在一个FCLK周期中,FPGA就需要根据FCLK来判断哪12个bit的串行数据,属于同一个12bit ADC数据;

高速位时钟DCLK则是相位提前90度,时钟边沿对齐到高速串行数据的每个bit的中心位置;

ADC提供一个或多个数据通道,一般一个差分数据通道,对应到一个ADC转换器,但也会有一个转换器对应多个差分数据通道,和一个差分数据通道对应多个转换器的情况出现,有一些ADC能够配置不同的输出数据结构;

下面指的1线模式,指1个转换器对应1个数据通道,2线模式,指1个转换器对应2个数据通道,其中转换器的数量一般对应ADC模拟信号输入的通道数量,差分数据通道数量则是对应连接到FPGA或其他处理设备的LVDS的数据通道数量;

DCLK的频率由ADC的分辨率、采样率、差分数据通道和转换器的对应关系决定的,一个ADC一般只有一个DCLK和一个FCLK,所有差分数据通道在ADC输出时,都会与这一个DCLK和FCLK同步;

LVDS I/O的最大速度由DCLK在FPGA逻辑或者ISERDESE2能支持的最大工作频率来设定;

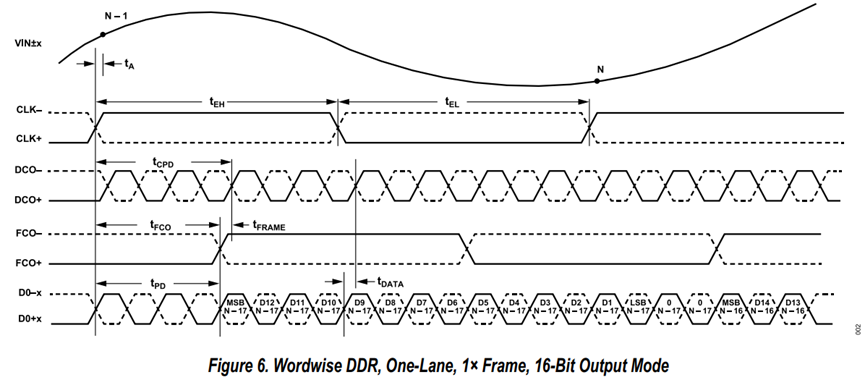

如16位ADC,1线DDR模式,150Ms/s:

比特率为:16150=2.4Gb/s;

由于使用DDR模式,则:

比特时钟速率为:16 150/2 = 1.2GHz;

可以看到这个16位150M采样率的ADC,如果只使用1个数据通道传输数据,需要1.2GHz的高速bit时钟,这个速度对于FPGA来说太高了,无法实现,那么解决方案则是,使用2线模式或是更多线模式,一个转换器对应2个或更多个数据通道;

16位ADC,2线DDR模式,150Ms/s:

比特时钟速率为:16*150/2/2 = 600MHz,

600MHz的时钟,在FPGA中的实现相比如1200MHz的时钟的实现就具有了可行性;

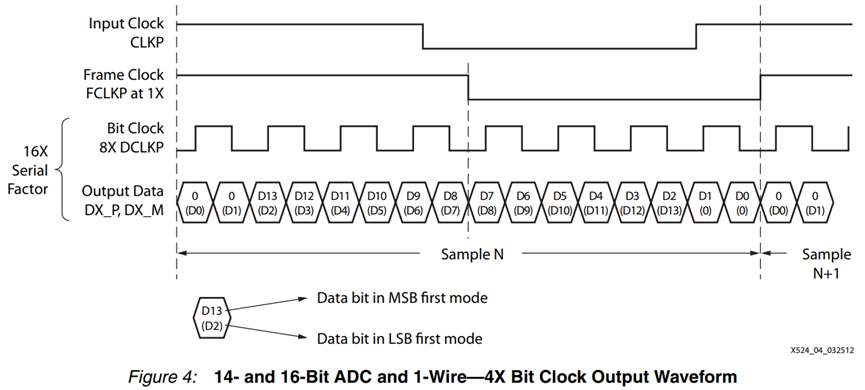

下图是14位和16位ADC在1线模式下的输出时序图:

上图时序中,16位和14位两种数据结构,使用的实现相同的时序,一个输入时钟Input Clock对应一个帧时钟FCLK,一个FCLK时钟周期下有8个Bit Clock,使用DDR模式,则1个FCLK能最大传输16个bit数据位,

其中16位则是将这个16bit数据位全部使用,14位则是闲置其中2个bit位;

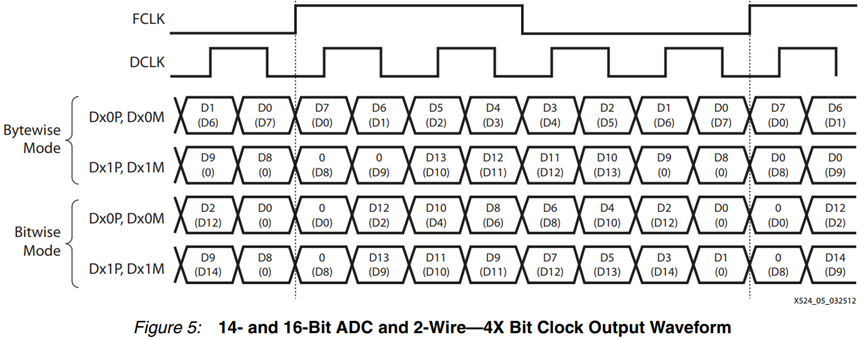

下图是14位和16位ADC在2线模式下的输出时序图:

上图时序,使用2线模式,相比于1线模式,2线模式使用2个差分数据通道传输1个转换器的数据,那么数据速率不变,比特时钟速度相应应该为1线模式的一半,

可以看出,FCLK帧时钟对应ADC的模拟输入采样时钟,所以对比1线模式应该不会变化,那么可以看到此时1个FCLK帧时钟周期下,只有4个DCLK比特时钟周期,可以确定DCLK在2线模式下为1线模式速度的一半;

其中Bytewise Mode和Bitwise Mode则是输出串行数据结构不同;

例如ad9253:

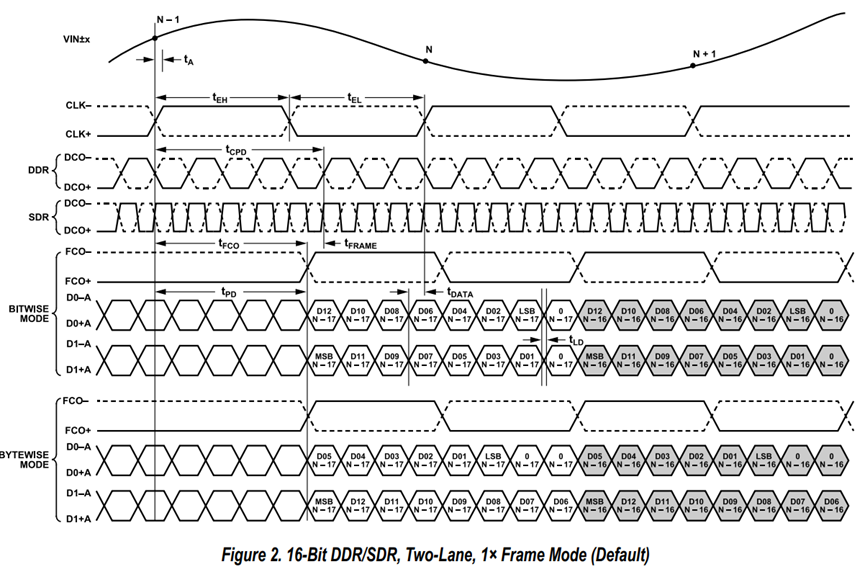

其上电默认时序模式为16位、2线DDR、1帧模式:

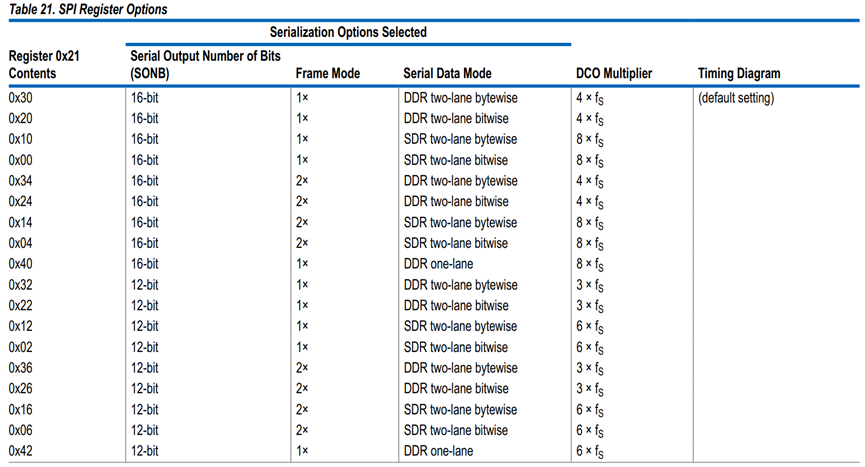

如果想使用ADC的其他模式,也可以使用ADC的SPI接口,配置其对应的时序模式寄存器:

如修改为12位、2线DDR、1帧模式:

或者修改为16位、1线DDR、1帧模式:

本文章由威三学社出品

对课程感兴趣可以私信联系