目录

前言

一、工程模块

[1.1 工程相关](#1.1 工程相关)

[1.2 源文件与约束](#1.2 源文件与约束)

[1.3 IP 核管理](#1.3 IP 核管理)

二、综合仿真

[2.1 分析阶段](#2.1 分析阶段)

[2.2 综合阶段](#2.2 综合阶段)

[2.3 分析报告](#2.3 分析报告)

[2.4 仿真阶段](#2.4 仿真阶段)

[2.5 上板调试](#2.5 上板调试)

[2.6 阶段核对](#2.6 阶段核对)

三、调试技巧

[3.1 消息 & 日志窗口](#3.1 消息 & 日志窗口)

[3.2 层级 & 逻辑资源](#3.2 层级 & 逻辑资源)

[3.3 时钟 & 约束辅助](#3.3 时钟 & 约束辅助)

四、术语总结

[4.1 工程搭建与模块管理](#4.1 工程搭建与模块管理)

[4.2 综合实现与仿真调试](#4.2 综合实现与仿真调试)

[4.3 辅助窗口与调试工具](#4.3 辅助窗口与调试工具)

[4.4 流程阶段概览](#4.4 流程阶段概览)

[4.5 其它术语](#4.5 其它术语)

[4.6 整体的流程图](#4.6 整体的流程图)

五、本文总结

六、更多操作

前言

Vivado 是 Xilinx(现 AMD)官方推出的一款面向 FPGA/SoC 设计的开发平台,被广泛应用于通信、人工智能、数据中心、汽车电子等领域的硬件设计开发。

对于初学者甚至有经验的硬件工程师而言,掌握 Vivado 的界面术语 不仅关乎学习效率,更直接关系到日后工作的规范性与交流准确性。

本文结合实际工作中的使用场景,从 Vivado 工程创建到综合实现、仿真验证的全过程出发,详细解析常见英文术语及其对应的中文理解,同时指出实际应用中应特别注意的要点与误区。按照逻辑将内容划分为三大部分,循序渐进,帮你快速掌握 FPGA 开发的第一步。

**一、**工程模块

工程搭建与模块管理:Vivado 核心术语详解

1.1工程相关

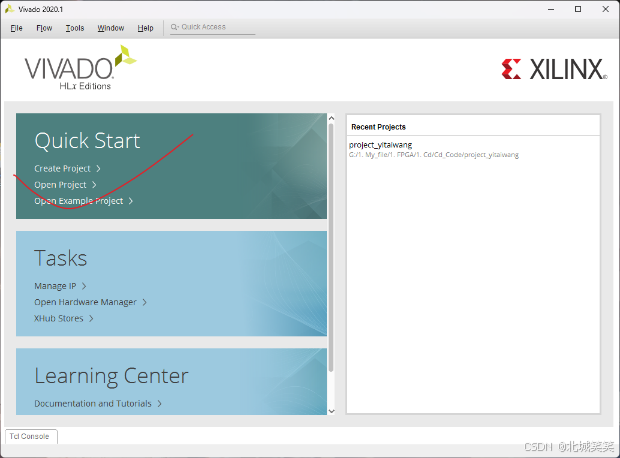

工程创建与管理相关术语

| 英文 | 中文 | 含义与用途 |

|---|---|---|

| Project | 工程 | Vivado 工程的基本单位,包含源代码、约束、IP、仿真、结果等所有内容。 |

| Create Project | 创建工程 | 启动新项目的入口,需指定工程路径、名称、FPGA 芯片型号。 |

| Open Project | 打开工程 | 打开已有的 .xpr 工程文件。 |

实际应用场景: 用于新建 / 打开 Vivado 工程,是所有开发流程的基础入口。项目初期,通常由架构工程师或开发负责人统一指定 Vivado 工程目录结构规范,确保后期多人协同不出混乱。

**注意事项:**工程路径、名称建议使用英文及短路径,避免空格、中文,减少不必要报错。

1.2源文件与约束

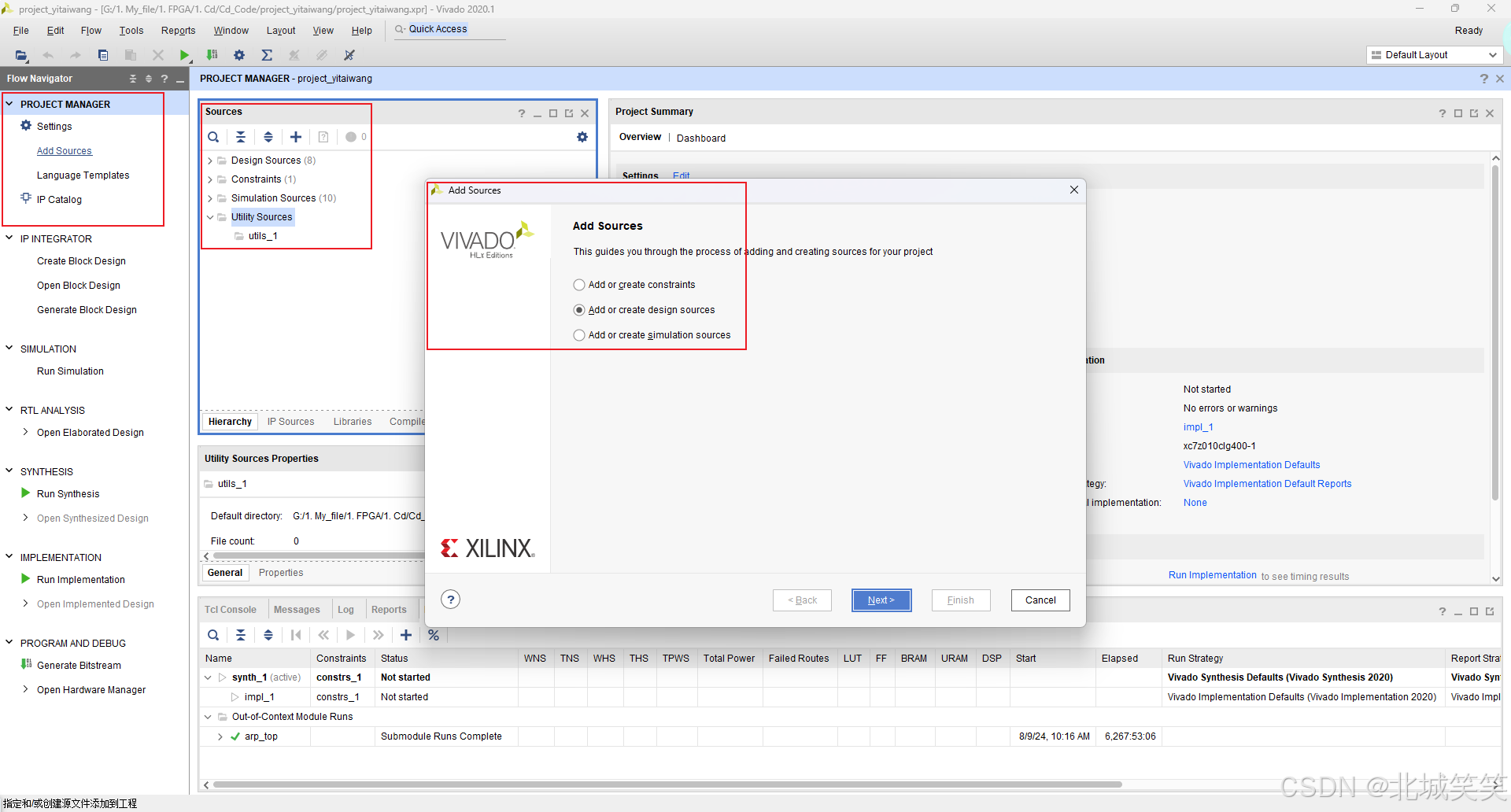

文件管理的相关术语

| 英文 | 中文 | 含义与用途 |

|---|---|---|

| Add Sources | 添加源文件 | 添加 HDL(Verilog/VHDL/SystemVerilog)等设计源代码。 |

| Add Constraints | 添加约束文件 | 添加 .xdc 约束,指定时钟、IO 引脚。 |

| Design Sources | 设计源文件 | 已纳入项目编译流程的逻辑设计文件清单。 |

| Simulation Sources | 仿真源文件 | 专门用于仿真的 Testbench 或激励文件。 |

| Constraints | 约束 | 时序 / IO |

| Utility Sources | 实用工具源文件 | 预定义可直接调用的基础逻辑模块或模板,用于快速实现常见辅助功能以提高设计效率。 |

**实际应用场景:**用于管理 RTL、约束、仿真等不同类型源文件,便于分类组织、调用。大型项目往往设计文件多、层级深,良好分组(Source Set)有助于模块管理。引脚约束往往结合硬件原理图同步更新,避免实际测试时板卡无法正常工作。

注意事项:

Source 文件命名规范(避免空格与中文),保持文件命名规范,路径扁平清晰,便于后续维护。

约束文件及时与硬件保持同步。

不要把仿真文件误加入综合流程。

1.3IP 核管理

IP 与 Block Design 相关术语

| 英文 | 中文 | 含义与用途 |

|---|---|---|

| IP Catalog | IP 核目录 | 可视化封装好的基础功能模块(AXI、FIFO、PLL 等)。 |

| IP Integrator (IPI) | IP 集成器 | 专门用于搭建 AXI 总线或复杂 IP 架构的工具。 |

| Block Design | 块设计(原理图设计) | 图形化系统架构(SoC 集成)设计,类似原理图搭建。 |

| BD (Block Diagram) | 块图 | Block Design 的缩写视图。 |

**实际应用场景:**便捷管理、搭建 SoC、AXI 互联结构,快速封装常用 IP 核,图形化更直观。Zynq、Versal 等 FPGA SoC 项目,通常大量使用 IPI + ARM + AXI 搭建硬件架构,通过 Block Design 管理 IP 子模块,极大提升开发效率并降低出错概率。

注意事项:

IP 使用后务必及时 Update IP,确保版本与接口保持一致,避免因版本差异导致功能异常,减少后续调试隐患。

建议锁定 IP 版本(Pin Version),防止在工程迁移或复用过程中出现版本冲突,提升项目稳定性与可维护性。

对于 IPI(IP Integrator) 自动生成的约束(如时钟 / 复位信号),建议统一整理归档,并纳入项目整体约束管理流程,以避免约束遗漏或重复定义的问题。

每次修改 Block Design(BD) 后,必须重新生成 Output Products(HDL Wrapper),以确保仿真与综合所使用的数据为最新版本,保障设计一致性。

**二、**综合仿真

综合实现与仿真调试:Vivado 核心流程术语与使用注意

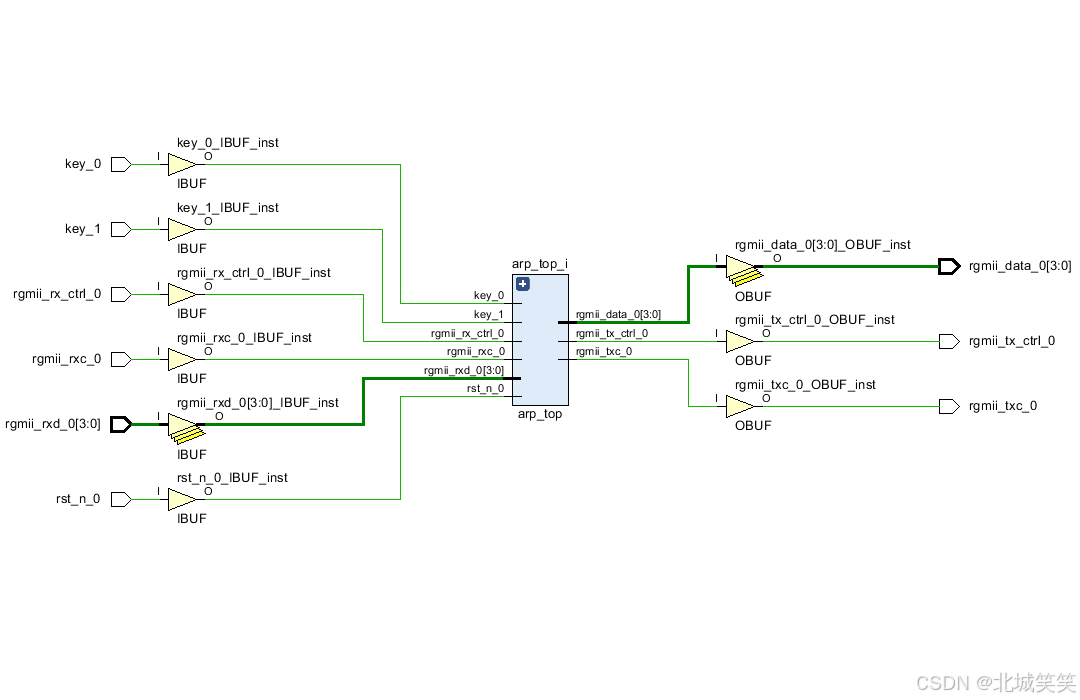

2.1 分析阶段

分析阶段相关术语

| 英文 | 中文 | 含义与用途 |

|---|---|---|

| RTL ANALYSIS | RTL分析 | 将硬HDL代码转换为逻辑电路图的过程 |

| Open Elaborated Design | 打开综合前的设计 | 查看 RTL 结构与连线情况。 |

| Schematic | 电路图 / 原理图 |

常用流程:

Xilinx Vivado,运行逻辑电路:通常叫做查看"电路图"或"原理图"(线路走向的图)

- RTL ANALYSIS RTL分析

- Open Elaborated Design 打开精心设计

这里的RTL Analysis(寄存器传输级分析)是FPGA设计过程中的一个重要步骤,它涉及将硬件描述语言(HDL)编写的代码转换为逻辑电路图的过程。

电路图示例:

2.2 综合阶段

综合实现(Synthesis)阶段相关术语

|-----------------------------|---------------|--------------------|

| Run Synthesis | **运行综合/**综合文件 | RTL → 门级逻辑转换,生成网表。 |

| Open Synthesized Design | 打开综合后的设计 | 查看逻辑实现、资源占用情况。 |

| Run Implementation | 运行实现 | 完成布局布线,时序收敛检查。 |

| Open Implemented Design | 打开实现后的设计 | 查看实际布线,时序路径。 |

**实际应用场景:**综合阶段主要用于逻辑正确性与资源预估分析,如 LUT、FF、BRAM、DSP 使用是否超限;查看图标以及综合结果是否符合预期架构设计。从 RTL → 网表 → 布局布线,生成最终硬件实现逻辑,核心步骤。

注意事项:

综合前检查约束完整性(时钟、IO),确保约束文件(XDC)正确绑定端口与时钟。

综合后分析逻辑扇出与优化情况,防止资源浪费。综合、实现完成后务必检查时序与资源报告,及时优化设计。

若综合耗时长,可启用增量综合(Incremental Synthesis)优化。

2.3分析报告

| 英文 | 中文 | 含义与用途 |

|---|---|---|

| Timing Summary | 时序摘要 | 时序收敛结果,是否满足要求。 |

| Utilization Report | 资源利用率报告 | 实际资源占用情况报告。 |

**实际应用场景:**分析设计是否满足时序与资源需求,指导后续优化调整。实现阶段重点检查关键路径是否满足时序,约束是否生效,资源分布是否均衡。通常结合 Timing Summary 查看 slack 值,调整约束或逻辑结构。

注意事项:

- 关注 WNS / TNS 时序指标 和 资源占比,评估优化空间。

- 不满足时序路径 要重点分析,勿忽略 Warning。

- 资源利用率 >90% 时应适当优化设计。

- 跨时钟域(CDC) 需特别小心,防止亚稳态风险。

WNS (Worst Negative Slack) :最坏路径的负裕量(时序余量);TNS (Total Negative Slack):所有不满足路径的时序总和。

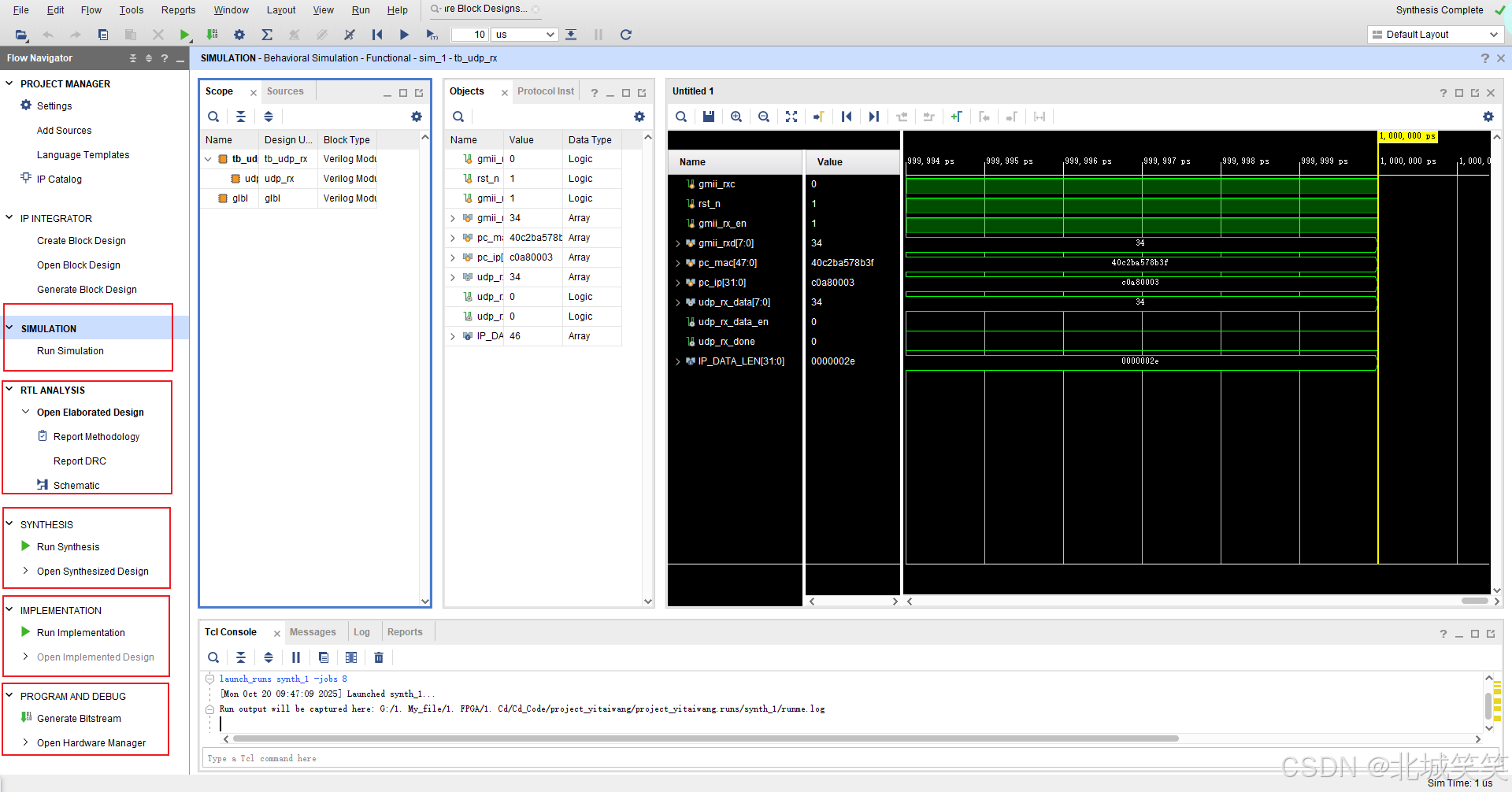

2.4仿真阶段

仿真(Simulation)阶段相关术语

| 英文 | 中文 | 含义与用途 |

|---|---|---|

| Simulation | 仿真 | 功能 / 时序验证手段。 |

| Run Simulation | 运行仿真 | |

| Run Behavioral Simulation | 运行行为仿真 | |

| Behavioral Simulation | 行为级仿真 | 功能逻辑验证。 |

| Post-Synthesis Simulation | 综合后仿真 | 带网表时序预览。 |

| Post-Implementation Simulation | 实现后仿真 | 最接近实际布线效果的仿真。 |

**实际应用场景:**验证 RTL 正确性、仿真时序收敛,提升设计可靠性。FPGA 项目通常先行为仿真验证 RTL 功能,再根据需要逐步深入后仿真,验证布线、IO 延迟等因素对设计是否有影响。

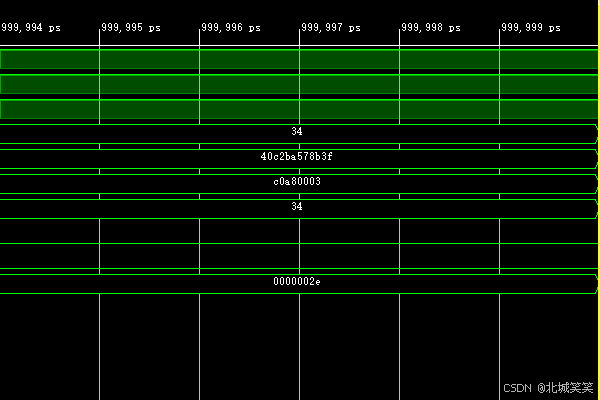

常用流程:

Xilinx Vivado,运行仿真流程:通常叫做查看"时序图"或"波形图"(绿色的波形图)

- SIMULATION 模拟/仿真

- Run Simulation 运行仿真

- Run Behavioral Simulation 运行行为仿真

时序图示例:

注意事项:

- 仿真环境搭建和激励信号需规范设计,严禁跳过功能验证环节。

- 仿真工具建议使用 Vivado 默认仿真器或与 ModelSim 联动,保证一致性。

- Testbench 代码应统一规范,提升可读性与可维护性。

- 建议生成 测试激励波形文件(如 .vcd / .wdb),便于后续问题分析与追溯。

2.5 上板调试

比特流(Bitstream)阶段相关术语

| 英文 | 中文 | 含义与用途 |

|---|---|---|

| Generate Bitstream | 生成比特流文件 | 输出 .bit 文件用于 FPGA 配置。 |

| Bitstream | 比特流 | FPGA 配置文件,二进制位流数据。 |

| Hardware Manager | 硬件管理器 | 下载比特流至 FPGA / JTAG 通信。 |

**实际应用场景:**生成硬件配置文件,下载至板卡,进行功能验证与调试。硬件工程师完成硬件电路板卡后,通过 Bitstream 下载进行上电测试,功能验证。Hardware Manager 提供 ChipScope、ILA 在线调试手段。

注意事项:

- 确保选择正确的板卡,JTAG 接口稳定可靠 ,下载后需复核实际功能。

- 下载前检查电源与 JTAG 接口状态,确保正常工作。

- 注意区分不同硬件版本对应的 bitstream文件,避免烧写错误。

- ILA 逻辑探针需合理规划资源使用,防止因资源冲突导致综合失败。

2.6 阶段核对

| 阶段 | 核心作用 | 补充说明 |

|---|---|---|

| 2.1 分析阶段 | 代码结构解析(Elaboration 阶段) | RTL Analysis 与 Open Elaborated Design 属于综合前阶段。 |

| 2.2 综合阶段 | RTL → 门级网表 → 实现准备 | "Run Synthesis / Run Implementation" 顺序准确。 |

| 2.3 分析报告 | 时序和资源分析报告阶段 | "Timing Summary / Utilization Report" 是实现后关键输出。 |

| 2.4 仿真阶段 | 功能验证与时序验证 | 三类仿真(行为 / 综合后 / 实现后)层次清晰。 |

| 2.5 上板调试阶段 | 生成 .bit 文件并下载到硬件 | Hardware Manager / ILA / JTAG 内容准确无误。 |

整体结构 :涵盖了 Vivado 全流程 5 大阶段(分析 → 综合 → 报告 → 仿真 → 上板调试)。

**三、**调试技巧

辅助窗口与调试技巧:其他常见辅助工具与术语理解

3.1 消息 & 日志窗口

| 英文 | 中文 | 含义 |

|---|---|---|

| Message | 消息窗口 | 显示综合、实现等日志。 |

| Tcl Console | Tcl 控制台 | 命令行 |

**实际应用场景:**在工程提交及综合实现阶段,必须对所有警告进行合理分析并归档保存,便于后续追踪和维护。

注意事项:

严重警告(Critical Warning)不可忽视,需确认原因及风险。

错误日志(Error)应从上至下逐条排查,确保无遗漏。

3.2 层级 & 逻辑资源

层级与逻辑资源视图

| 英文 | 中文(习惯译法) | 备注 |

|---|---|---|

| Hierarchy | 层级视图 | 模块结构 |

| Netlist | 网表 | 逻辑结构 |

**实际应用场景:**用于查看模块层次关系、逻辑结构,分析信号走向、调试问题,检查综合结果是否符合预期。

注意事项:

查看网表前,确认综合或实现流程已完成。

层级视图和网表仅显示设计结构,不包含仿真波形或动态数据。

3.3 时钟 & 约束辅助

| 英文 | 中文(习惯译法) | 备注 |

|---|---|---|

| Clocking Wizard | 时钟向导 | PLL / MMCM |

| Constraint Wizard | 约束向导 | 生成约束 |

**实际应用场景:**快速生成稳定时钟模块,辅助创建时序与 IO 约束文件,避免手写错误,提高效率。

注意事项:

使用 IP 核要及时更新并重新封装。

约束内容需核对原理图和实际硬件一致,不能直接套用他人项目。

四、术语总结

Xilinx Vivado 工程流程

4.1 工程搭建与模块管理

| 序号 | 英文术语 | 中文(习惯译法) | 备注 / 含义 |

|---|---|---|---|

| 1 | Project | 工程 | Vivado 的基本设计单元,包含所有文件与设置。 |

| 2 | Create Project | 创建工程 | 新建 FPGA 工程并指定芯片型号、工程路径。 |

| 3 | Open Project | 打开工程 | 打开已保存的 Vivado 工程。 |

| 4 | Add Sources | 添加源文件 | 添加 HDL 源文件(Verilog / VHDL)。 |

| 5 | Add Constraints | 添加约束文件 | 添加 .xdc 时序与引脚约束文件。 |

| 6 | Design Sources | 设计源文件 | 工程主逻辑文件(RTL 模块)。 |

| 7 | Simulation Sources | 仿真源文件 | 用于功能仿真的 Testbench 测试文件。 |

| 8 | Constraints | 约束文件 | 描述引脚、时钟、时序等硬件约束条件。 |

| 9 | IP Catalog | IP 核目录 | Vivado 内置可定制 IP 模块库。 |

| 10 | IP Integrator (IPI) | IP 集成器 | 图形化 SoC 搭建平台,集成多 IP。 |

| 11 | Block Design (BD) | 块设计(原理图) | IP Integrator 生成的模块化系统视图。 |

| 12 | Block Diagram | 块图视图 | 展示模块连接关系的图形化结构。 |

| 13 | Managed IP Project | IP 管理工程 | 用于单独维护和复用 IP 模块的工程形式。 |

4.2 综合实现与仿真调试

| 序号 | 英文术语 | 中文(习惯译法) | 备注 / 含义 |

|---|---|---|---|

| 14 | RTL Analysis | RTL 分析 | 将 HDL 转换为逻辑结构图,用于代码逻辑验证。 |

| 15 | Open Elaborated Design | 打开综合前的设计 | 查看 RTL 层次结构与信号连线关系。 |

| 16 | Run Synthesis | 运行综合 | 将 RTL → 门级逻辑网表(生成逻辑映射)。 |

| 17 | Open Synthesized Design | 打开综合后的设计 | 查看综合后资源利用率、逻辑优化结果。 |

| 18 | Run Implementation | 运行实现 | 完成布局布线、时序优化与逻辑映射。 |

| 19 | Open Implemented Design | 打开实现后的设计 | 查看布线、时序路径与最终布局。 |

| 20 | Timing Summary | 时序摘要 | 检查设计是否满足时序约束(WNS、TNS)。 |

| 21 | Utilization Report | 资源利用率报告 | 显示 LUT、FF、DSP、BRAM 等资源占用情况。 |

| 22 | Generate Bitstream | 生成比特流文件 | 输出 .bit 文件,用于 FPGA 配置。 |

| 23 | Bitstream | 比特流 | FPGA 的硬件配置文件(二进制位流)。 |

| 24 | Hardware Manager | 硬件管理器 | 连接 FPGA 硬件,下载比特流与在线调试。 |

| 25 | Simulation | 仿真 | 对设计进行逻辑或时序验证。 |

| 26 | Run Simulation | 运行仿真 | 启动仿真器执行仿真过程。 |

| 27 | Run Behavioral Simulation | 运行行为仿真 | 功能级仿真,不考虑时序延迟。 |

| 28 | Post-Synthesis Simulation | 综合后仿真 | 在门级网表基础上进行仿真。 |

| 29 | Post-Implementation Simulation | 实现后仿真 | 布局布线完成后的完整时序仿真。 |

4.3 辅助窗口与调试工具

| 序号 | 英文术语 | 中文(习惯译法) | 备注 / 含义 |

|---|---|---|---|

| 30 | Message | 消息窗口 | 显示编译、综合、实现等警告与错误。 |

| 31 | Tcl Console | Tcl 控制台 | 执行 Vivado 命令行操作(Tcl 指令)。 |

| 32 | Hierarchy | 层级视图 | 展示工程模块层次结构。 |

| 33 | Netlist | 网表 | 综合生成的逻辑结构文件,连接关系说明。 |

| 34 | Clocking Wizard | 时钟向导 | 用于生成 PLL / MMCM 等时钟管理模块。 |

| 35 | Constraint Wizard | 约束向导 | 辅助创建与验证时序约束。 |

| 36 | ILA (Integrated Logic Analyzer) | 集成逻辑分析仪 | 在线逻辑信号捕获与调试工具。 |

| 37 | VIO (Virtual I/O) | 虚拟输入输出 | 允许在仿真或上板过程中动态改变信号值。 |

| 38 | Report Timing / Utilization | 报告窗口 | 汇总设计时序与资源使用结果。 |

4.4 流程阶段概览

| 阶段 | 主要内容 | 典型操作 |

|---|---|---|

| 工程搭建阶段 | 建立项目、添加源文件与约束 | Create Project、Add Sources、Add Constraints |

| 综合阶段 | RTL → 门级网表转换 | Run Synthesis、Open Synthesized Design |

| 实现阶段 | 布局布线、时序优化 | Run Implementation、Open Implemented Design |

| 仿真阶段 | 功能与时序验证 | Run Simulation、Behavioral Simulation |

| 上板调试阶段 | 比特流下载与硬件调试 | Generate Bitstream、Hardware Manager、ILA |

以上列举的是 Vivado 中最常见、最基础、最实用的界面术语及其中英文对照,涵盖了从工程管理、IP 使用、综合实现、仿真调试,到约束、时序分析、硬件调试等典型 FPGA 开发流程的关键界面和功能。

⚠️ 需要特别说明的是 :

Vivado 实际使用过程中,界面术语、菜单选项、报错信息等并不局限于以上表格所列内容。随着工程规模、IP 核复杂度、工具版本更新等不同,Vivado 还包含大量更细分的功能模块,例如:

- Block Automation(模块自动化):自动创建或配置设计模块,提高搭建效率。

- Debug Hub(调试中心):用于集成和管理片上调试逻辑,支持 ILA、VIO 调试工具。

- Hardware Setup(硬件设置):配置 FPGA 与开发板相关的硬件参数及接口。

- Power Report(功耗报告):生成设计的功耗分析结果,辅助低功耗优化。

- ILA(集成逻辑分析仪):用于实时采集和分析 FPGA 内部信号,支持在线调试。

等等工具相关菜单。不同项目或团队关注点不同,常用术语也可能略有差异。这里总结的重点术语,足够支撑日常 FPGA 开发者进行基本项目搭建、调试、交付。如果后续使用过程中遇到其他术语,可结合 Vivado 官方文档、帮助系统或实际界面查找含义。

4.5 其它术语

| 英文 | 中文(习惯译法) | 含义 |

|---|---|---|

| Critical Warning | 严重警告 | 通常需关注,部分隐患可能致命。 |

| Error | 错误 | 必须解决,流程停止。 |

| LUT(查找表) | 查找表 | 基础逻辑运算资源 |

| FF(触发器) | 触发器 | 存储时序单元 |

| DSP(乘法器) | 乘法器 | 用于乘法 / 累加的硬件单元 |

| BRAM(块 RAM) | 块 RAM | 存储器资源 |

实际应用场景:

1️⃣ Critical Warning / Error

在 Vivado 开发过程中,无论是综合(Synthesis)、实现(Implementation),还是约束检查、比特流生成阶段,Critical Warning 和 Error 都是最重要的日志类型。

Critical Warning 通常提示 时序未约束、跨时钟域风险、IP 配置冲突等潜在隐患 ,虽然部分流程仍可继续,但生成结果可能存在功能性或稳定性风险,需引起高度重视。

Error 则会直接导致流程中断 ,常见原因包括 HDL 代码错误、约束文件异常、路径不存在等 ,此类问题必须第一时间定位并修复,方可继续后续流程。

2️⃣ LUT / FF / DSP / BRAM

这是 FPGA 芯片内部的四类核心物理资源:

- LUT(查找表) :实现基本组合逻辑功能,如加法、比较、状态机等,反映逻辑电路的整体规模。

- FF(触发器) :用于数据寄存和时序同步,是构建时序逻辑的关键单元。

- DSP(数字信号处理单元) :高效执行乘法、累加等运算,广泛应用于滤波器、FFT 等信号处理模块。

- BRAM(块 RAM) :提供片上大容量存储,适用于数据缓存、FIFO、双口 RAM 等需要存储结构的场景。

我们需要结合项目规模、时序性能,合理规划使用比例,防止资源不足或使用不均导致性能瓶颈。

注意事项:

✅ 关于 Critical Warning / Error:

- 所有 Error 必须修复,否则将导致流程中断,无法进入后续步骤。

- Critical Warning 不建议忽略,即使不影响综合,也可能隐藏时序违规或功能风险(如时钟约束缺失)。

- 项目交付或量产前 ,必须确保 无 Error ,并对所有 重要 Critical Warning 提供明确的技术说明或处理措施。

✅ 关于 LUT / FF / DSP / BRAM:

- 综合报告中的资源利用率建议控制在 70%~85% 之间,为后续优化与维护预留空间。

- DSP 和 BRAM 属于稀缺资源,应优先用于大规模运算或数据缓存场景,避免提前耗尽影响其他模块实现。

- 资源利用率不均衡(如某类资源耗尽而其他空闲)可能导致布局布线困难、时序难以收敛,需提前规划协调。

- ILA(在线逻辑分析仪)会占用 LUT 和 BRAM 资源,在设计规划时应预留一定余量,避免资源紧张。

4.6 整体的流程图

✅ Vivado 常见整体流程图(中文思维逻辑版)

javascript

【创建工程】

├── Create Project(创建工程)

├── Add Sources(添加源文件)

├── Add Constraints(添加约束文件)

└── IP Catalog / IP Integrator(添加或配置 IP 模块)

【分析阶段】

└── RTL Analysis(RTL 分析)

└── Open Elaborated Design(查看 RTL 结构与连线)

【综合阶段】Run Synthesis

├── 逻辑综合(RTL → 门级网表)

├── 查看资源利用率 / 时序

└── Open Synthesized Design(打开综合后设计)

【实现阶段】Run Implementation

├── 布局布线(Placement & Routing)

├── 时序收敛检查(Timing Analysis)

└── Open Implemented Design(查看实际布线与路径)

【比特流生成阶段】Generate Bitstream

├── 生成 FPGA 配置文件(.bit)

└── Hardware Manager(下载至 FPGA / 调试)

【仿真阶段】

├── Run Behavioral Simulation(行为仿真)

├── Post-Synthesis Simulation(综合后仿真)

└── Post-Implementation Simulation(实现后仿真)🧭 流程说明:

| 阶段 | 主要目的 | 输出文件 |

|---|---|---|

| 创建工程 | 建立工程、添加文件与约束 | .xpr 工程文件 |

| 分析阶段 | 验证 RTL 结构、模块连接正确性 | RTL 电路图 |

| 综合阶段 | 将 RTL 转换为逻辑网表 | .dcp(综合后设计) |

| 实现阶段 | 布局布线、时序优化 | .dcp(实现后设计) |

| 生成比特流 | 输出硬件配置文件 | .bit |

| 仿真阶段 | 验证设计逻辑与时序 | .wdb、波形文件 |

🟢 总结一句话:

Vivado 的标准设计流程是:

工程创建 → RTL 分析 → 综合 → 实现 → 生成比特流 → 仿真验证 → 上板调试

五、本文总结

Vivado 的英文术语看似简单,但背后映射的是 FPGA 开发完整流程的核心步骤与行业通用规范 。无论是新手入门还是项目实战,理解并掌握这些术语将极大提升开发效率,减少沟通成本,规避潜在风险。

本文不仅提供了详细中英文对照,更结合了工作中常见的场景、经验与注意事项,帮助你从概念认知走向实际落地。想要了解更多,请订阅 FPGA 专栏。

六、更多操作

完整 FPGA 系列,请看

FPGA 专栏![]() https://blog.csdn.net/weixin_65793170/category_12665249.html

https://blog.csdn.net/weixin_65793170/category_12665249.html

文章目录,请看

FPGA系列,文章目录![]() https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502

https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502