下一篇:

JTAG TO AXI Master 实战案例参考如下:

FPGA DDR3实战(四):DDR3地址Mapping自动化测试-CSDN博客

一 引言

在FPGA开发中,如何高效地验证AXI总线系统一直是个关键问题。今天我们将深入探讨Xilinx提供的一款强大调试工具------JTAG to AXI Master IP核 ,它为AXI总线调试提供了极大的便利,也是后续进行DDR3自动化脚本测试的重要基础。

二 JTAG to AXI Master IP核概述

JTAG to AXI Master IP核是一个可定制的核心,能够在系统中生成AXI事务并驱动FPGA内部的AXI信号。该IP核具有以下主要特性:

-

支持AXI4和AXI4-Lite接口协议

-

可配置的AXI数据宽度(32位/64位)

-

可配置的AXI地址宽度(32位/64位)

-

支持所有内存映射AXI接口事务

-

通过Vivado逻辑分析仪Tcl控制台进行硬件交互

三 IP核工作原理

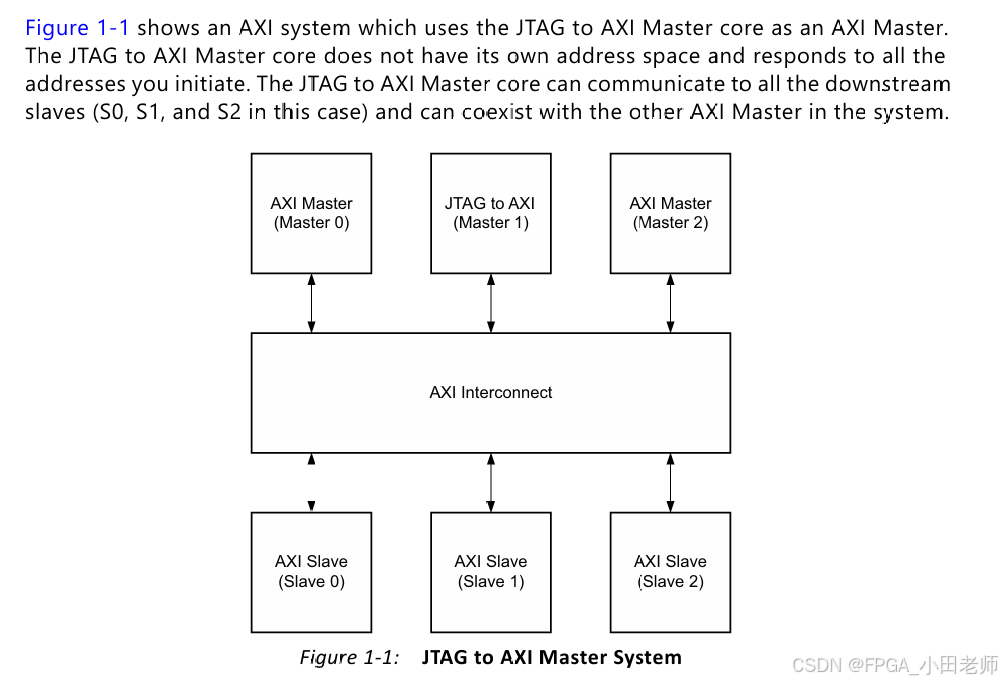

JTAG to AXI Master作为AXI系统中的一个主设备,可以通过JTAG接口接收来自Vivado Tcl控制台的命令,并将其转换为标准的AXI事务。它没有自己的地址空间,可以响应所有发起的地址,与系统中的其他AXI主设备共存。

典型系统架构:

四 Tcl控制台命令详解

JTAG to AXI Master的核心价值在于通过Tcl脚本实现灵活的AXI事务控制。

1 基本写事务:

# 创建写事务

create_hw_axi_txn write_txn [get_hw_axis hw_axi_1] \

-address 40000000 \

-data 12345678 \

-type write

# 执行写事务

run_hw_axi write_txn2 基本读事务:

# 创建读事务

create_hw_axi_txn read_txn [get_hw_axis hw_axi_1] \

-address 40000000 \

-type read

# 执行读事务

run_hw_axi read_txn3 突发传输示例:

# 8个数据的AXI4突发写

create_hw_axi_txn burst_write [get_hw_axis hw_axi_1] \

-address 40000000 \

-data {11111111 22222222 33333333 44444444 55555555 66666666 77777777 88888888} \

-len 8 -size 32 -type write

# 队列执行多个事务

run_hw_axi txn1 txn2 txn3 -queue五 实战搭建:基于BRAM的测试环境

我们以米联客MK7160FA开发板(FPGA型号:XC7K325TFFG676_2)为例,搭建一个基础的测试环境。

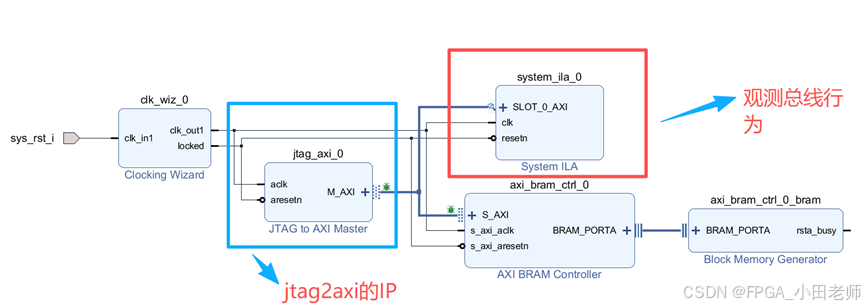

1. 设计框图

我们搭建的设计框图如下:

使用JTAG to AXI Master + BRAM控制器 + ILA的经典组合:

-

JTAG to AXI Master:生成AXI事务

-

AXI BRAM Controller:控制Block RAM

-

Block Memory Generator:提供存储空间

-

ILA:监控AXI总线行为

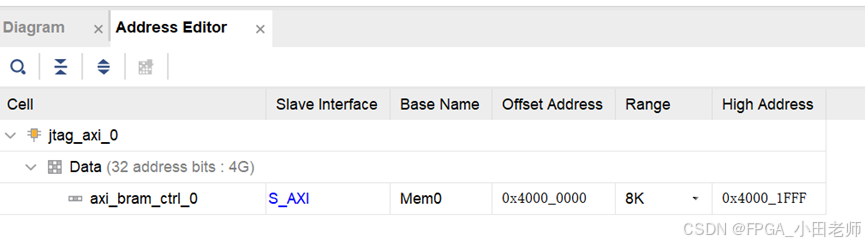

2. 关键配置

-

AXI协议:AXI4(支持突发传输)

-

数据宽度:32位

-

地址宽度:32位

-

BRAM地址空间:0x4000_0000 - 0x4000_1FFF

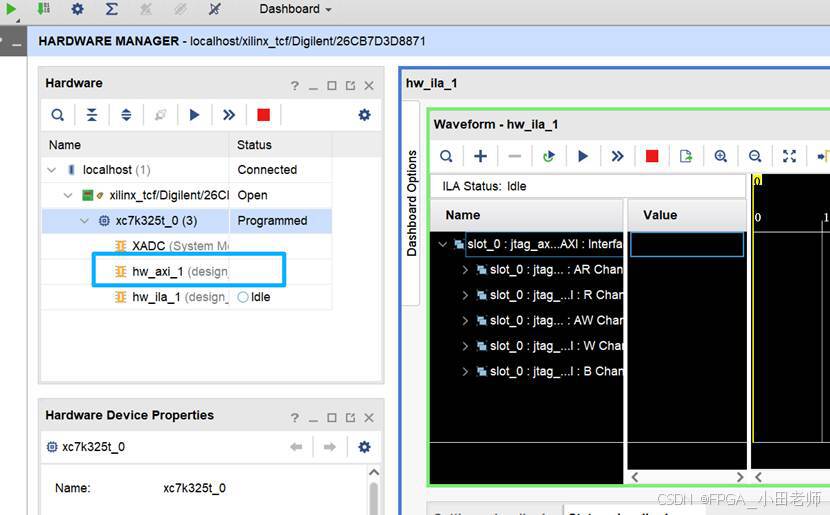

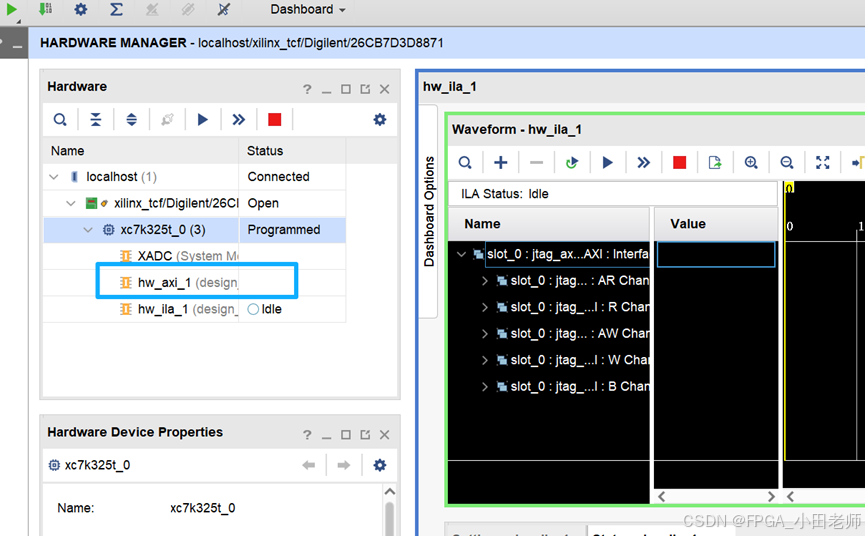

我们将程序烧写到板子里面,烧写完成之后,我们在界面上看到hw_axi_1,说明我们的jtag to axi master ip已经存在了

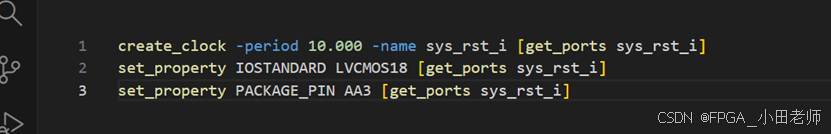

3 引脚约束和bit生成

综合实现无误生成bit之后,我们将程序烧写到板子里面,烧写完成之后,我们在界面上看到hw_axi_1,说明我们的jtag to axi master ip已经存在了

我们可以在Tcl Console中输入脚本,读写BRAM的地址空间进行测试

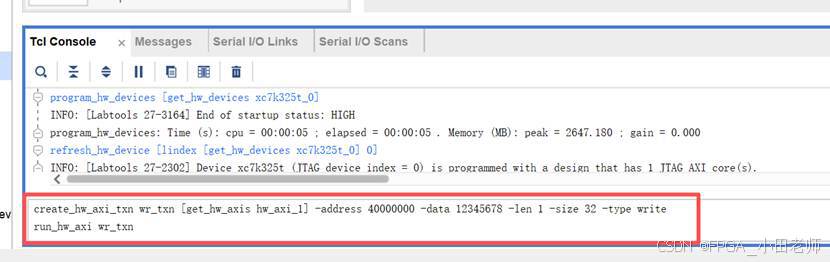

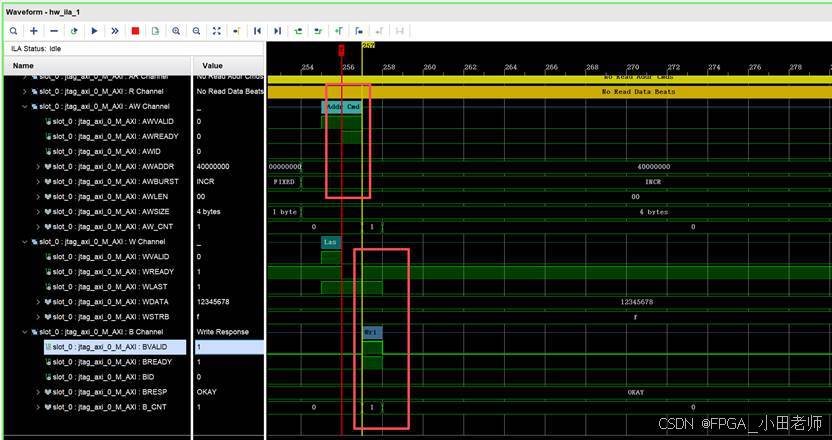

4 写事务测试

我们创建一个写事务,即给地址0x4000_0000写数据0x12345678,如下:

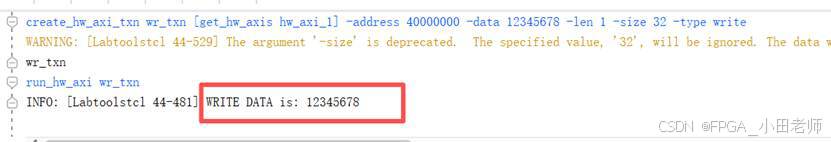

打印出WRITE DATA is:12345678,即数据写入完成

同时我们可以在ila上观测到如下波形,确实发起了一笔写请求。写地址为0x4000_0000,写数据为0x12345678,并且收到了有效的写response信号。

说明该数据已经正常写入BRAM中

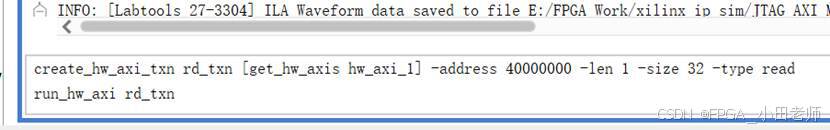

5 读事务测试

如下,我们在Tcl Console中创建一个读事务,并发起读请求,请求的读地址为0x4000_0000

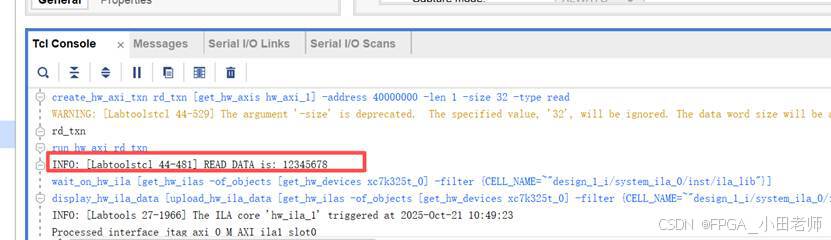

Tcl Console打印出RDATA is 12345678,即读出的数据是0x12345678,与我们刚才写入的一致

同时我们在ila上观测读波形如下,确实发起了读请求,返回数据为0x12345678.

读写一致 ,这是一个最简单的jtag2axi的读写测试,大部分情况下,我们需要直接使用脚本进行自动化测试,这个在下一篇我们使用JTAG2AXI对DDR3硬件的地址mapping功能进行自动化脚本测试,我们会详细介绍到这个脚本。

六、应用场景与价值

1. 系统前期验证

在与其他主设备(如PCIe)联调之前,使用JTAG to AXI Master验证FPGA硬件设计的正确性。

2. 自动化测试

通过编写Tcl脚本,实现自动化的读写测试,大大提高测试效率。

3. 性能分析

结合ILA核,可以详细分析AXI总线的时序特性,优化系统性能。

4. 故障诊断

当系统出现异常时,可以通过该IP核直接访问特定地址,快速定位问题。

七、调试技巧与注意事项

-

时钟与复位:确保aclk和aresetn正确连接,IP核工作在正确的时钟域

-

地址映射:确认目标从设备的地址空间与Tcl命令中的地址匹配

-

队列管理:合理设置事务队列长度以平衡性能和资源

八、为DDR3测试奠定基础

本次基于BRAM的测试为后续的DDR3自动化测试提供了重要基础:

-

命令熟悉:掌握了create_hw_axi_txn和run_hw_axi等核心命令

-

流程验证:建立了完整的"创建-执行-验证"流程

-

监控手段:学会了使用ILA监控AXI总线行为

-

脚本基础:为编写复杂的DDR3测试脚本积累了经验

在下面关于DDR3自动化测试的文章中,FPGA DDR3实战(四):DDR3地址Mapping自动化测试-CSDN博客,

我们将基于这些知识,扩展到更复杂的场景:

-

DDR3控制器的地址映射

-

大数据量的连续读写测试

-

带宽和延迟的性能测试

-

自动化测试脚本的编写与优化

总结

JTAG to AXI Master IP核是FPGA开发中不可或缺的调试工具,它架起了JTAG接口与AXI总线之间的桥梁。通过灵活的Tcl命令控制,我们可以快速验证硬件设计的正确性,执行自动化测试,并为后续复杂的存储控制器测试奠定坚实基础。

掌握这个工具的使用,将显著提升你的FPGA调试效率和系统验证能力。