目录

[1.1 控制集](#1.1 控制集)

[1.2 控制集的影响](#1.2 控制集的影响)

[1.3 大控制集设计](#1.3 大控制集设计)

[1.4 设计规避大控制集方法](#1.4 设计规避大控制集方法)

[1.5 控制集优化](#1.5 控制集优化)

一、控制集

1.1 控制集

控制集Control Set是控制信号(置位/复位信号、时钟使能信号和时钟信号)的组合,用于驱动任意给定的SRL、LUTRAM 或寄存器,对于控制信号的任意独特组合,都会组成1个独立控制集。

1.2 控制集的影响

只有完全相同控制信号(时钟,复位,使能信号)的触发器才能被放进同一个 slice,设计如果所含独立控制集过多,即同一个slice中可放置的触发器减少,可能导致资源浪费过多并且布局选项减少,从而导致功耗上升且可实现的时钟频率降低。设计所含控制集越少,则布局选项更多且灵活性更高,并且通常可以得到更好的结果。

1.3 大控制集设计

如果设计中存在一些不规范,则容易产生较大的控制集

-

每个寄存器使用不同的 复位 信号(尤其是异步复位)。

-

每个寄存器使用不同的 时钟使能。

-

每个寄存器分散在多个

always块中,工具难以合并。 -

使用条件复杂的复位/使能逻辑,而不是统一 gating。

1.4 设计规避大控制集方法

要从设计上避免出现较大的控制集,可以从以下角度考虑

1)统一复位信号

合并多个复位为一个全局复位,对不需要严格复位的寄存器,可去掉复位。

2)优先使用同步复位

异步复位会形成独立控制集,同步复位可由逻辑优化合并。

3)减少 CE(时钟使能)数量

多个独立 CE 信号会形成多个控制集,可通过数据选择逻辑替代 CE。

4)避免门控时钟(Gated Clock)

多个门控时钟 = 多个控制集,用 CE 或逻辑条件替代门控时钟;

- 对不需要复位的寄存器取消复位

很多数据通路寄存器在上电时会被逻辑覆盖,无需复位。

6)统一时钟树

多个独立时钟会导致多个控制集,若频率相同,可考虑时钟域合并(时钟复用)。

1.5 控制集优化

通常每 8 个 CLB 寄存器对应 1 个控制集,CLB 寄存器数量/8,对于设计中控制集需要优化的占比参考如下

二、工程示例

2.1工程代码

示例工程中存在同步控制与异步控制的触发器的控制集场景,

// bad_design.v

module control_set #(parameter N=20)(

input wire clk,

input wire [N-1:0] rst_vec, // 每个寄存器有不同复位

input wire [N-1:0] ce_vec, // 每个寄存器有不同CE

input wire [N-1:0] d_in,

output reg [N-1:0] q_out,

input wire rst, // 每个寄存器有相同复位

input wire ce, // 每个寄存器有相同CE

output reg [N-1:0] q_same

);

// 每个寄存器单独一个 always 块,复位和CE都不同

generate

genvar i;

for(i=0;i<N;i=i+1)

begin

always @(posedge clk)

begin

if (rst_vec[i]) q_out[i] <= d_in[i];

// else if (ce_vec[i]) q_out[i] <= d_in[0];

// if (rst_vec[i]) q_out[i] <= 0;

// else if (ce_vec[i]) q_out[i] <= d_in[0];

end

end

endgenerate

generate

genvar j;

for(j=0;j<N;j=j+1)

begin

always @(posedge clk)

begin

if (rst) q_same[j] <= 0;

else if (ce) q_same[j] <= d_in[j];

end

end

endgenerate

endmodule2.2 控制集报告

console执行命令report_control_sets,可生成控制集报告,报告有summary(概览),Histogram(控制集扇出的分布),Flip-Flop Distribution(触发器类型)

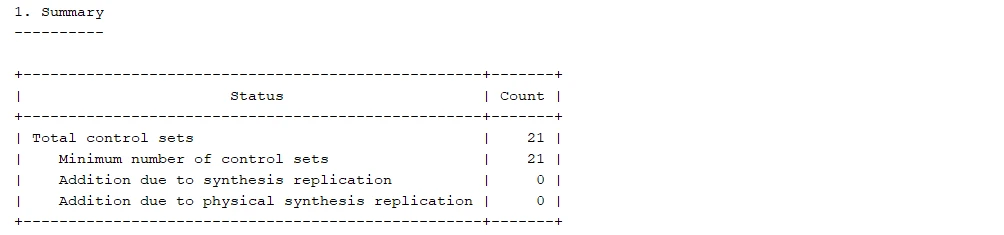

summary报告如下,统计了设计中总的控制集数量,以及综合和物理综合阶段因复制增加的控制集数量

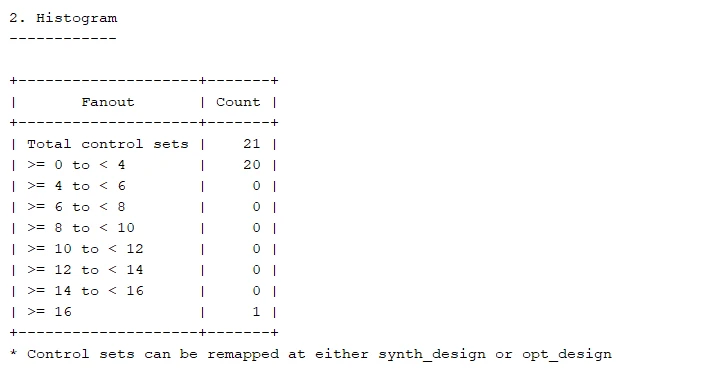

Histogram则是按照扇出的大小来统计各阶段的数量

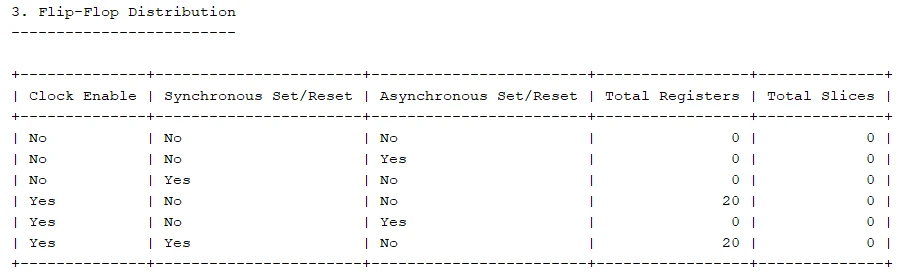

Flip-Flop Distribution如下图,报告不同控制信号触发器的分布情况

三、参考资料

《ug949-vivado-design-methodology-zh-cn》