最近使用了27DR的板子,是第一次接触RFSOC的产品,遇到了很多个奇怪的问题,写篇文章总结一下我对RF data converter这个ip核的看法

这是我遇到过配置最复杂的ip核,包括接口数量,时钟结构种种方面的问题,我将通过几个部分分别写下我对这个IP核的理解

1. 概述

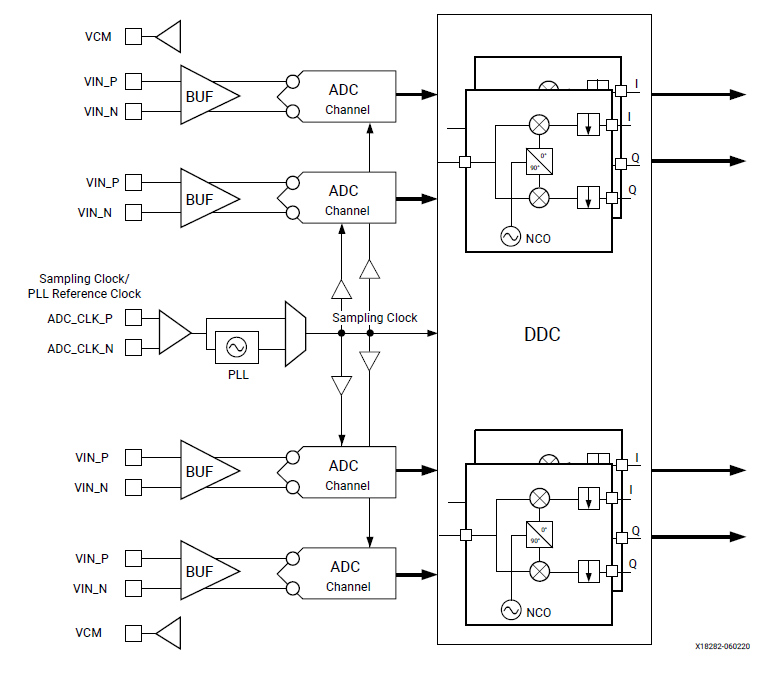

ZU27DR属于GEN1的架构,包含8×ADC + 8×DAC,ADC的最高采样率为4.096GHz,DAC的最高采样率为6.554GHz,每个通道支持独立配置采样率,混频模式等操作

模块组成有ADC子系统,包含模拟采样 + DDC(数字下变频) + 抽取滤波的功能

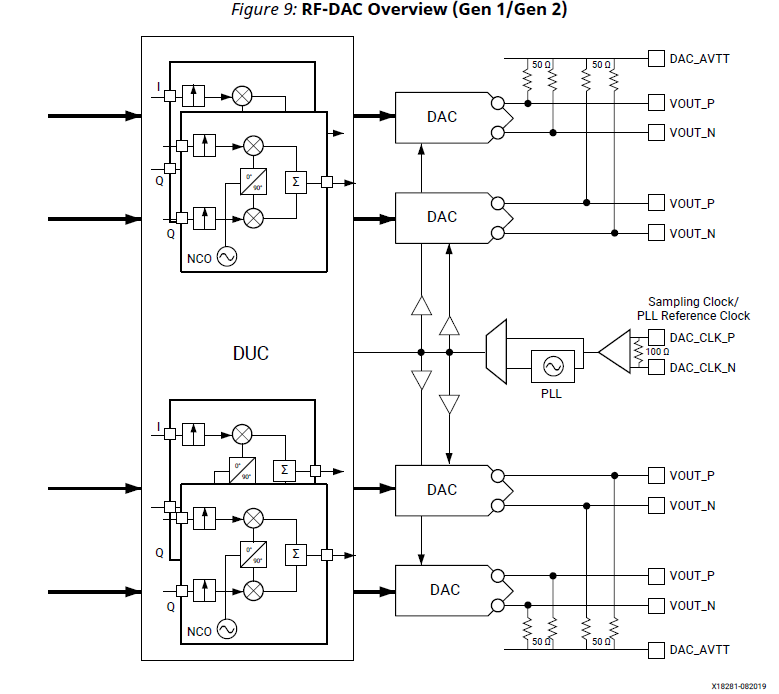

还有DAC 子系统,有插值滤波 + DUC(数字上变频) + 模拟输出的功能

ADC和DAC以tile的形式存在,像27dr这块板子 是4个adc tile,每个tile两片adc,2个dac tile,每个tile四片dac。

Gen 1的架构支持: 1x, 2x, 4x, 8x的插值模式,插值的具体作用之后会讲到

IP核整体集成高速 ADC/DAC 转换、数字下变频(DDC)、数字上变频(DUC)、NCO 混频、插值/抽取滤波等功能。

2. 时钟系统

主要时钟有

- Samlping clk: AD/DA的采样时钟,通常为GHz级,时钟大小为驱动采样的实际转换速度

- Reference clk: 为内部PLL提供参考输入

- AXI clk:驱动FPGA数据通路的时钟速率,通常在100-500mhz左右

- clk_out:从ip输出的时钟速率,与采样率有关

具体每个时钟的来源去向会在下一篇文章中详细提到

3. 数据接口

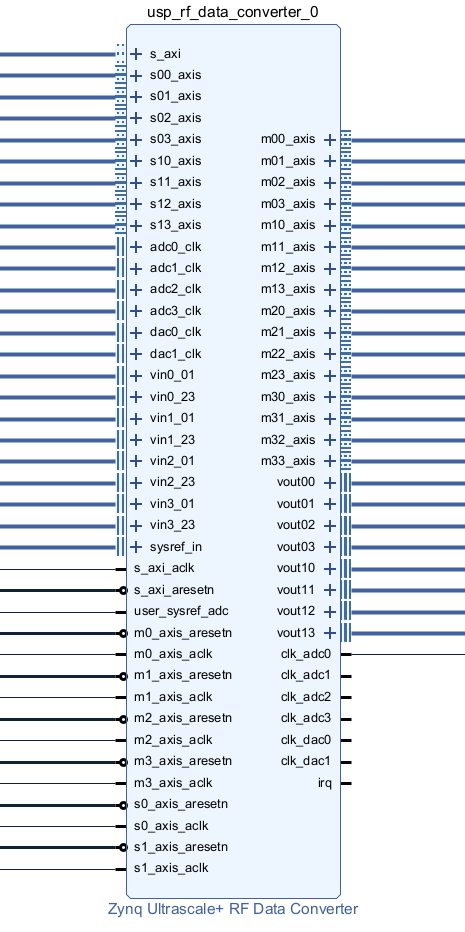

这是ip核完全配置完毕之后向外的接口图

|-----------------------|--------|--------------|-------------------------------------------------|

| 接口名字 | IN/OUT | 驱动时钟 | 功能 |

| s_axi_aclk | IN | N/A | AXI时钟输入 |

| sysref_in | IN | N/A | 外部模拟SYSREF输入 |

| user_sysref_adc | IN | m0_axis_aclk | 来自PL端自己配置的设计的RF-ADC SYSREF输入;与RF-ADC模块0 PL时钟同步 |

| user_sysref_dac | IN | s0_axis_aclk | 来自PL端自己配置的设计的RF-DAC SYSREF输入;与RF-DAC模块0 PL时钟同步 |

| adc/dacX_clk | IN | N/A | RF-ADC/DAC片内PLL参考时钟或采样时钟输入 |

| sX_axis_aclk | IN | N/A | 用于RF-DAC数据输入的时钟输入 |

| sX_axis_aresetn | IN | N/A | sX_axis_aclk域的低电平有效同步复位。在sX_axis_aclk稳定之前应保持低电平 |

| sXY_axis_tdata[M:0] | IN | sX_axis_aclk | AXI 4-流数据输入 |

| sXY_axis_tvalid | IN | sX_axis_aclk | AXI 4-Stream有效 |

| sXY_axis_tready | OUT | sX_axis_aclk | AXI 4-Stream就绪 |

| vout | OUT | N/A | DAC模拟输出 |

| mX_axis_aclk | IN | N/A | 用于RF-ADC数据输出的时钟输入 |

| mXY_axis_tdata[M:0] | OUT | mX_axis_aclk | AXI 4-流数据输出 |

| mXY_axis_tvalid | OUT | mX_axis_aclk | AXI 4-Stream有效 |

| mXY_axis_tready | IN | mX_axis_aclk | AXI 4-Stream就绪 |

| vin | IN | N/A | ADC模拟输入 |

| irq | OUT | s_axi_aclk | 中断输出 |

以上就是ip核接口的名字属性以及功能简介

4. 功能配置

-

DAC 功能

-

插值倍数:1× / 2× / 4× / 8×

-

Mixer 类型:Fine / Coarse / Bypass

-

输出模式:Real / I/Q

-

NCO 频率分辨率、相位累加器位宽

-

Output Mode:SNR Optimize / SFDR Optimize

-

ADC 功能

-

抽取倍数:1× / 2× / 4× / 8×

-

Mixer 类型:Fine / Coarse / Bypass

-

输入模式:Real / I/Q

-

DDC 功能配置

-

采样对齐与通道同步