目录

简介

最近新凯莱的高速示波器项目很火爆,于是计划坐一起高速示波器的实战项目,由于硬件已经安排了,在同步安排一篇关于FPGA的。

项目内容

本方案基于XINLINX的K7系列FPGA,ADC选用AD9226。

项目内容:

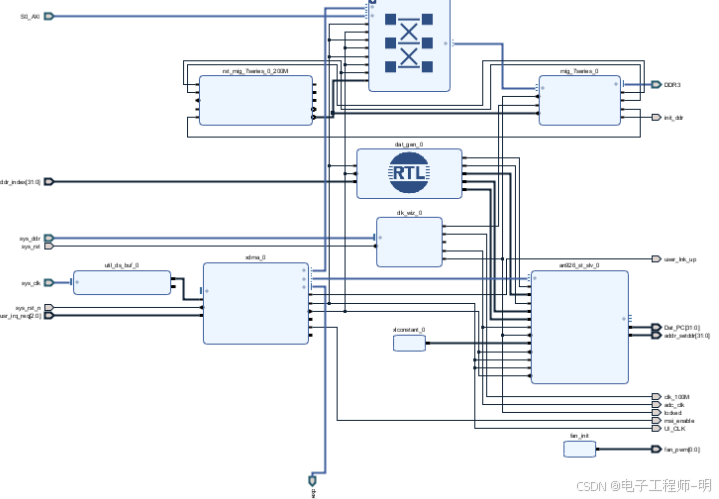

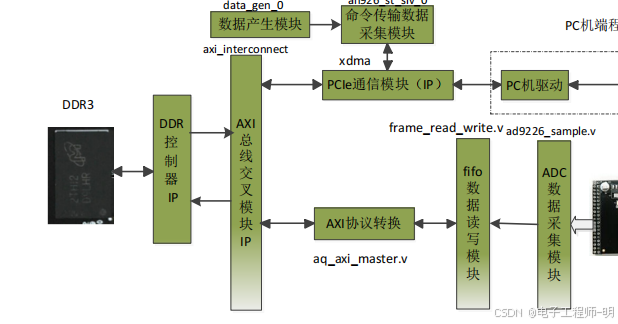

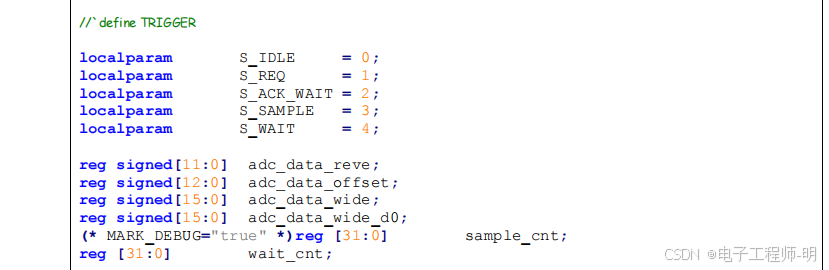

FPGA段固件程序:负责采集前端ADC的信号,FPGA基本框架,数据协议

PCIe卡驱动:负责上位机测试程序与PCie采集卡的数据交互

PC段测试程序:显示基本的波形

基本流程:ADC采集到数据后,会产生写FIFO,通知FIFO读写模块把ADC的数据写入FIFO中,由于DDR的数据接口是AXI接口,所有这里还设计了协议转换模块。在读取DDR数据时,PC机程序通过PCIe通信发出读DDR数据,DDR

3 中的数据通过AXI总线和PCIe接口上传给PC机,PC机通过软件进行波形显示。

实战内容:

介绍项目设计方案,设计代码(详细解释细节代码设计思路)

学员组我设计,设计疑问答疑

最后做总结