文章目录

前言

学习PCIE的基本知识,这是硬件工程师的必经之路

一、前置知识串行并行:

电脑中的不同设备之间交互数据也需要通路,电脑中不同设备交互的通路叫总线,总线和我们现实生活中的道路是一样的,现实中的道路有限速和限宽,一条道路能通行多少量汽车,就是这条道路的通行能力,路不可能无限宽,汽车也不可能无限快,所以总线的数据传输能力我们叫做带宽,

串行并行

并行 就是很多数据一块传输,但是

①必须数据同步传输,什么叫同步,传输前,传输过程中,传输完成,数据都要对齐好,什么都要对齐好,所以速度很难快起来,取决于最慢的那一个数据,需要照顾数据的协同传输,效率做不高

②并行总线由于相邻的链路是同时传输的,就会互相产生干扰,并且也容易受到外界干扰,抗干扰性较差。如果出现错误,还需要重新对齐,再次传输。

③占用较多IO,接口面积大

串行 就是数据一个接着一个传输,串行比如USB,就叫通用串行总线,

①行就是数据一个接着一个传输,取决于最快的那一个数据,所以每个数据都很快,效率并不低,因为只有一条链路,频率可以做成很高很高。

②串行如果一个数据出现错误,再重新传一个过去就好了。

③只用一个IO

二、PCIE的前世今生

PCIE的协议非常复杂,光是文档就有一千多页,对于我们初学者非常不友好,但是对于我们应用来说,比如工程师来说,还是非常好学的,

1.PCI的发展史

最早期的电脑,进入消费市场的,进入民用家庭的时候,CPU和不同设备之

间的连接总线接口是不一样的,

比如 CPU 连接声卡,有声卡的接口。连接硬盘,有硬盘的接口。连接网卡,

有网卡的接口。而且,不同主板的接口还不一样。

声卡

网卡

硬盘

为了解决这个问题,为了统一硬件规格和标准。IBM 公司联合 intel 公司,给

它的 PC 和外围设备制定了一个标准的接口,即 ISA 总线。

ISA 总线是一种 16 位并行总线,带宽最大 8MB/S,ISA 总线也有缺点,比如

插上一个 ISA 总线的声卡,还需要去手动去配置一些软件参数,才可以使用,无

法做到即插即用,ISA总线支持的外围设备有限,最多支持6个外围设备。

后面又慢慢发展到 32 位的 EISA 总线、VESE 总线、MCA 总线,不过这些总

线都是昙花一现。直到PCI总线横空出世,并且得到了主流厂商的认可,并且迅

速统一了各类总线,PCI总线一统天下啦

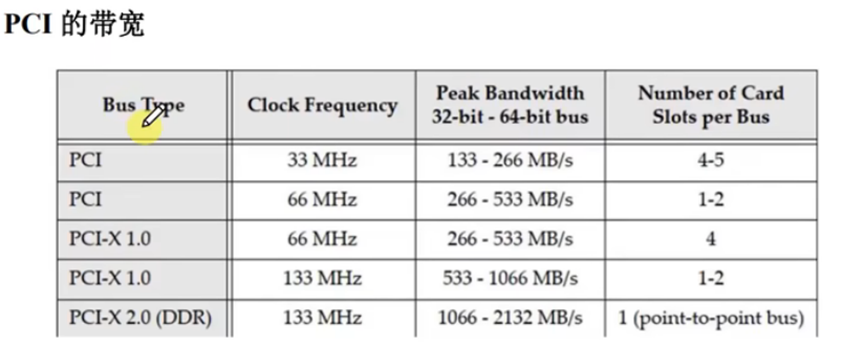

2.PCI的带宽

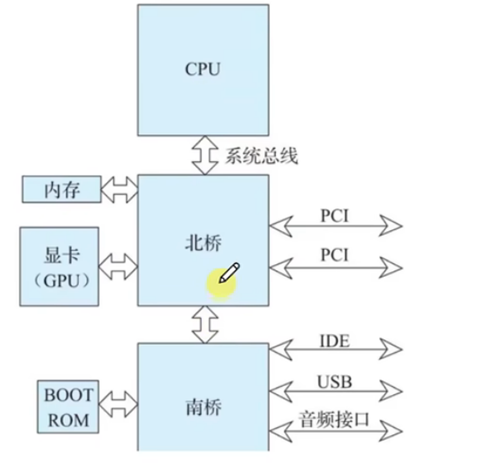

有个概念,南桥北桥。为什么需要桥,原因是为了解决CPU跟设备的读取速度不一致导致的

桥 Bridge:方便 CPU 和外设进行通信

北桥 芯片:负责速率比较快 的外设,比如支持PCI的设备

南桥 芯片:负责速率比较慢 的外设,比如麦克风、键盘等等

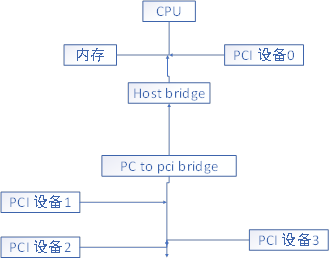

主桥相当于我们这个北桥,PC to pci bridge相当于一个扩展,北桥的挂在设备数量有限,

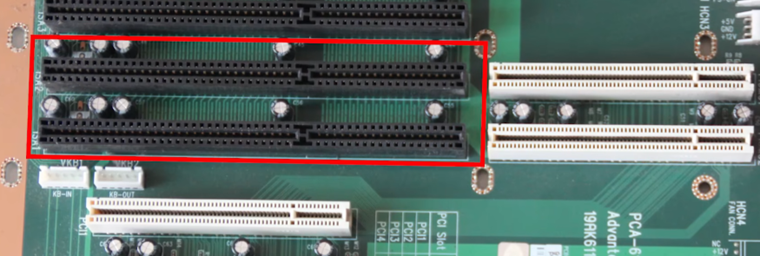

三、PCI和PCIE的异同

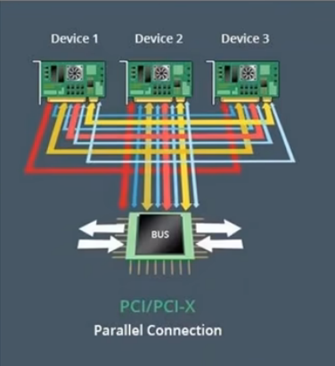

①PCI : Shared bus

总线使用并行总线结构,在同一条总线上所有的外部设备共享总线带宽。采

用共享总线的机制,会出现不同的设备抢占总线的情况,所有带宽还是有限。

②PCIE : Point to Point,点对点

点对点的传输,每一个外部设备独自拥有一条总线。并且PCIE是差分的,抗干扰能力更强

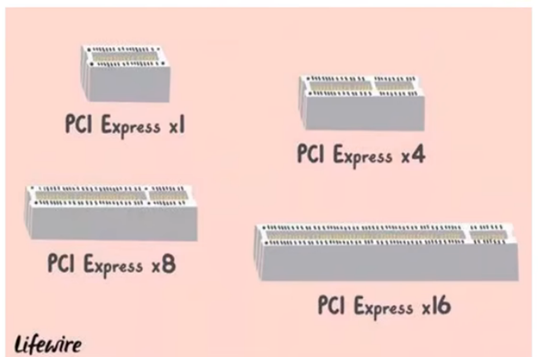

③)向后兼容性 (Software Backward(

Compatibility

新的协议会兼容旧的的协议,PCIE 可以兼容 PCI、PCIE 3.0 可以兼容 PCIE

2.0、PCIE x8 可以兼容 PCIE x2 等等

④速率

PCI最大带宽 266MB/S,PCIE 1.0x1带宽达到了 250MB/S

四、PCIE的基础知识

1、定义和特点

PCIE 为 PCI Express 的缩写。

定义:外部设备高速互联总线,一般就是CPU和外部设备连接(显卡、声

卡等等)

特点:

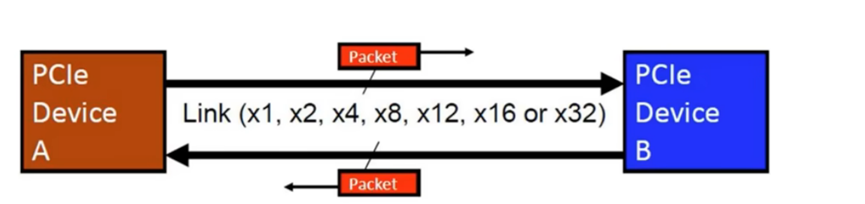

① 点对点、全双工通信 ②)路由方式简单③基于数据包协议传输

2、 express link

Link 和 lane 的区别

一条 lane 就是一对 tx 和 rx。Tx 和 rx 都是差分对的组成,差分抗干扰能力

更强

Link 描述的设备 A和设备 B之间通信的,link 可以由多条 lane 组成,现在最高就X16

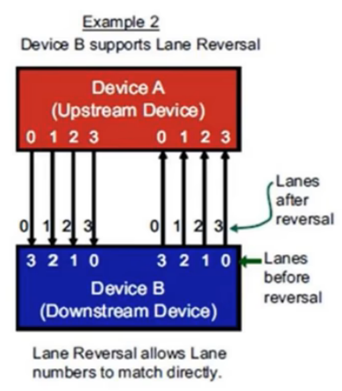

3、PCIE Lane reversal

PCIE 的 lane 可以不用 0对 0,1 对 1,2 对 2、3 对 3,比如说TX0直接怼到对面的RX3也是没有问题的、减少 pcb 工作量,兼容

性比较强。减少过孔和绕线

4、PCIE Polarity Inversion

PCIE 的极性可以翻转,正可以对着负,减少PCB 工作量,兼容性非常强,比如说TX1+接RX3-,都是可以的

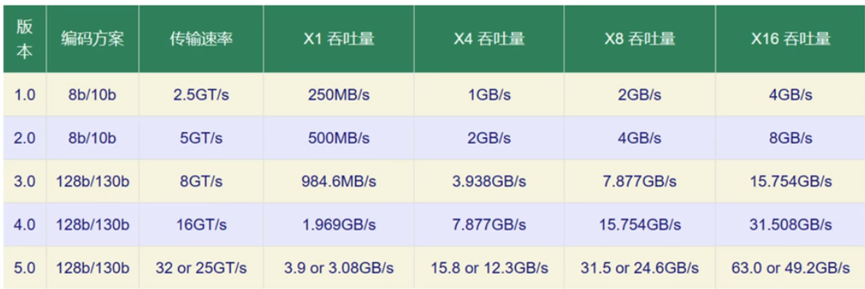

5、PCIE的速率

(注;PCIE5.0目前还只是概念阶段,还没有大规模应用)

GT/S:Giga transaition per second,即每一秒内传输的次数,这是一个新的单位

带宽(吞吐量)=(传输速率lane数量 效率)/8= GB/S

举个例子,PCIE2.0x4,带宽=(5GT/s 4 0.8)/8=2GB/s

由于 PCIE 的速率非常快,FPGA 实现 PCIE,是通过专门硬核来实现,是由

特定的 bank 实现(MGT bank),这个bank用来传高速数据的,不能用来作其他功能

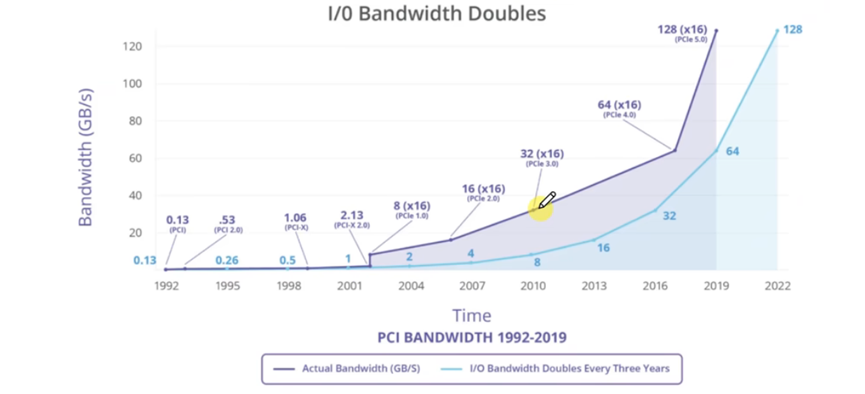

PCIE 发展很快,隔个两三年翻一翻。如果发展不快,可能会被其他的总线

给取代。

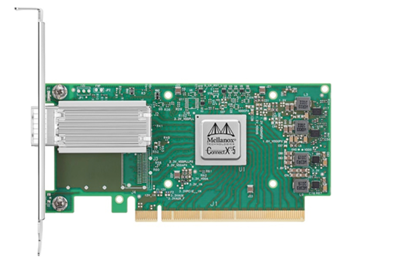

五、FPGA实现PCIE接口

PCIE总线非常复杂,开发一套成熟的FPGA和PCIE的通信系统。一般需

要硬件工程师、FPGA 工程师、上位机驱动工程师等等的配合。由于开发难度比

较大,所以有一些开源的框架。当然,也有很多公司出售非开源的框架,满足更

多应用的需求。

1、RIFFA 框架,最大支持12通道

2、XAPP1052 和xdma框架,使用起来最简单

3、以色列的 Xillybus 的多通道 DMA 框架

4、北大 EPEE 框架

开源框架里面,一般 riffa 和 xdma 框架用的比较多

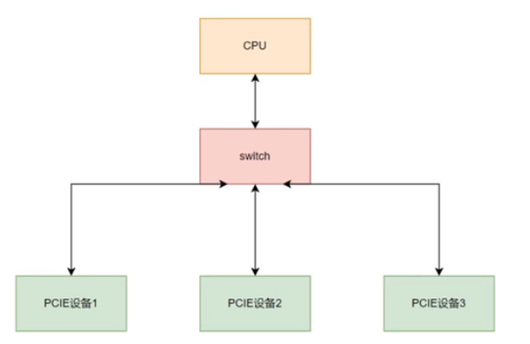

六、PCIE的拓扑结构

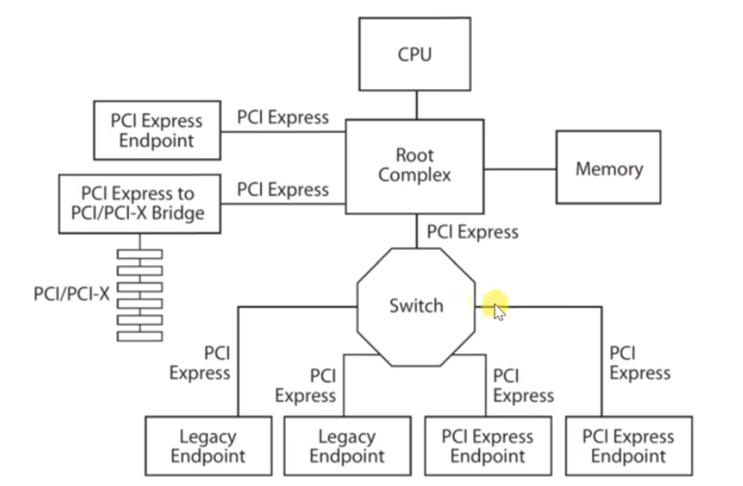

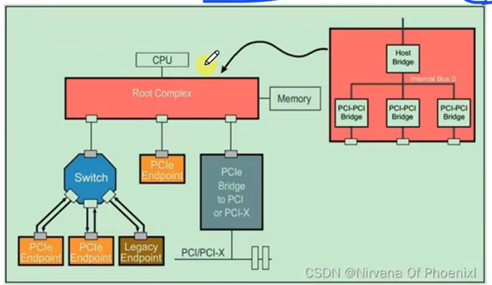

Root Complex 一般被称之为 RC、根部,怎么理解 Root Complex?

① CPU 和 PCIE 总线之间的媒介,比如说CPU有个数据包,发给ENDpoint,先把数据发给一个虚拟地址,这个虚拟地址映射到内存,然后根部把数据读出来,然后经过SWITCH给到我们的终端设备,CPU不会直接跟终端设备进行通信

② 可以将 Root Complex 理解为北桥芯片 Host Bridge +PCI-PCI Bridge

③ Endpoint :终端设备,比如显卡

④ Switch :扩展交换设备,Switch后面还能接switch扩展

七、PCIE电路设计

虽然PCIE的协议很复杂,但是对于应用来说,还是比较简单,毕竟有很多开源框架,我们硬件工程要做的是要做好原理图设计和PCB布线规范,应用就不会有什么大问题

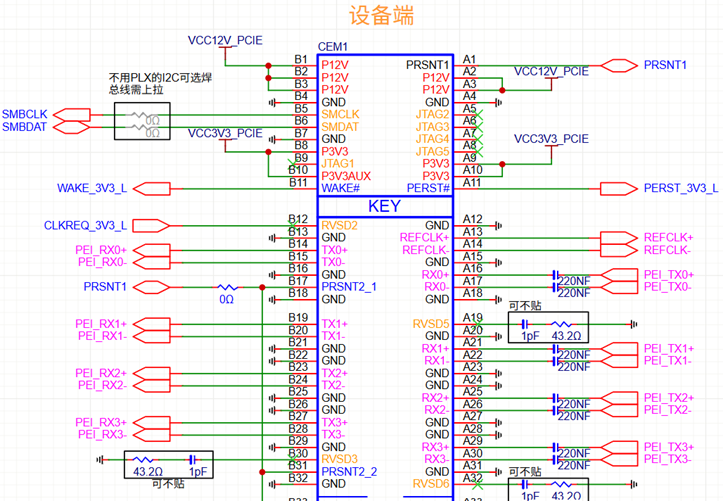

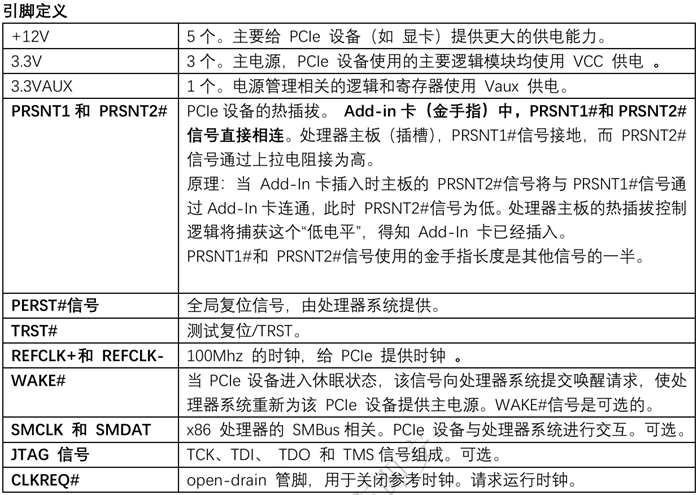

1、电路设计:

一般常见的电路设计就是这种,TX端要加耦合电容用于隔直

发射端 (Tx) :产生高速数据信号 交流耦合电容 隔离直流电压,防止双方直流偏置冲突,实现直流平衡。

接收端 (Rx) :正确采样数据信号 (无外部元件) 内部已集成终端电阻和直流偏置电路,用于阻抗匹配和信号恢复。

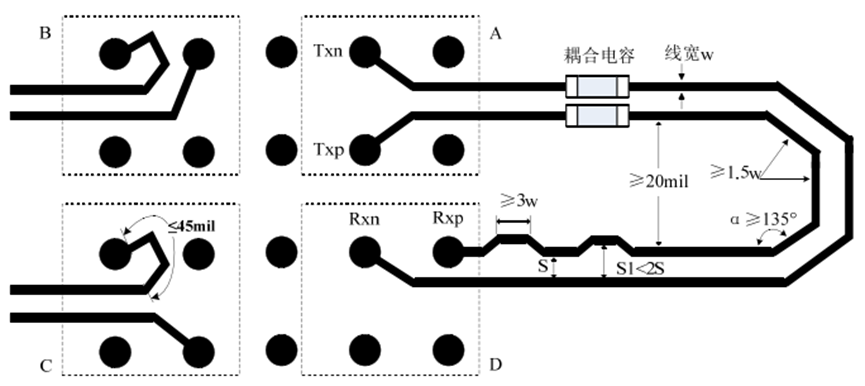

2、PCB设计

PCB布局布线常见要求

① 阻抗控制:差分阻抗常见有85Ω/90Ω/100Ω(根据不同CPU)。

② 线长控制:走线长度尽量不超过10inch,差分线对内需控制等长±2mil。

③ 走线平滑:采用10°转弯角度走线。

④ 信号隔离和屏蔽:走线有完整的参考地,并远离其他高速信号和电源;Lane和Lane之间采用地孔进行隔离,同时保持3W或5H原则。

⑤ 走线过孔:尽量避免过孔,过孔数量控制在2个以内;对于过孔处,需要做阻抗匹配以及预留回流地过孔。

⑥ 电源去耦电容:去耦电容靠近电源管脚放置 。

⑦ 交流耦合电容:差分线对内的交流耦合电容需同一物料,电容下方做挖空处理

总结

硬件-信号(有线)-PCIe信号及硬件设计深入解析-CSDN博客

PCIE-PCB设计规范!(建议收藏)-CSDN博客

PCIE架构设计、第一讲 PCIE基础知识、深入理解高速接口底层原理_哔哩哔哩_bilibili

PCIe硬件电路设计01_哔哩哔哩_bilibili

【硬核科普】一根线传输效率比多根线高?详解串并行总线的工作原理与优劣_哔哩哔哩_bilibili

后续学习