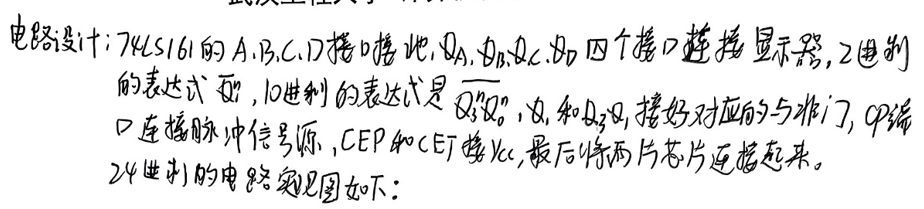

24小时数字钟实战!74HC161搭24/60进制计数器+Multisim仿真(附完整原理图+进位避坑)

刚做数字钟实验时,我对着一堆芯片和导线卡了一下午:秒针跑满60不触发分钟加1,小时到24还在往25跳,甚至数码管只亮一半数字。后来才发现,数字钟的核心不是"堆器件",而是"拆模块+控进位"------把钟拆成"秒→分→小时"三部分,每部分用74HC161做进制计数器,再用进位信号串起来,像搭积木一样简单。今天从模块拆分到接线实操,再到Multisim仿真,跟着做就能实现"时:分:秒"精准显示。

一、先搞懂:数字钟要做啥?核心怎么拆?

1. 实验核心需求(必须先明确)

- 功能:显示24小时制时间(00:00:00~23:59:59循环),1Hz秒脉冲已提供;

- 模块拆分 :按"秒→分→小时"拆成3个独立模块,每个模块解决"进制计数+进位联动":

- 秒模块:60进制(00~59),秒到59时向分模块发"进位信号";

- 分模块:60进制(00~59),分到59时向小时模块发"进位信号";

- 小时模块:24进制(00~23),小时到23时清零,不向其他模块进位;

- 显示 :用共阴极数码管(或Multisim里的DCD_HEX显示器),每部分用2个数码管(个位+十位),共6个显示"时:分:秒"。

2. 核心器件分工(新手不用记参数,记"作用")

| 器件型号 | 所属模块 | 通俗作用 | 核心任务 |

|---|---|---|---|

| 74HC161×6 | 秒/分/小时模块 | 4位同步计数器(能改造成任意进制) | 秒/分用2片做60进制,小时用2片做24进制 |

| 74HC00(与非门) | 进制清零逻辑 | 生成"到目标值就清零"的信号 | 秒到59、分到59、小时到23时,输出低电平触发清零 |

| 74HC08(与门) | 进位信号联动 | 把计数器进位端信号传给下一级 | 秒TC→分CLK使能,分TC→小时CLK使能 |

| 共阴极数码管 | 显示模块 | 把二进制输出转成数字(0~9) | 秒/分/小时的个位+十位分别显示 |

| Multisim 12 | 仿真工具 | 验证电路是否正常工作 | 测进制计数、进位、显示是否正确 |

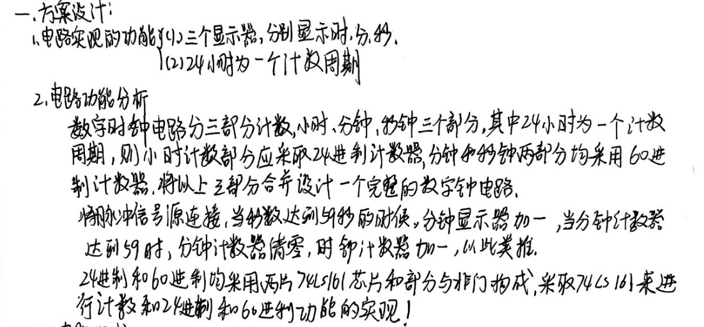

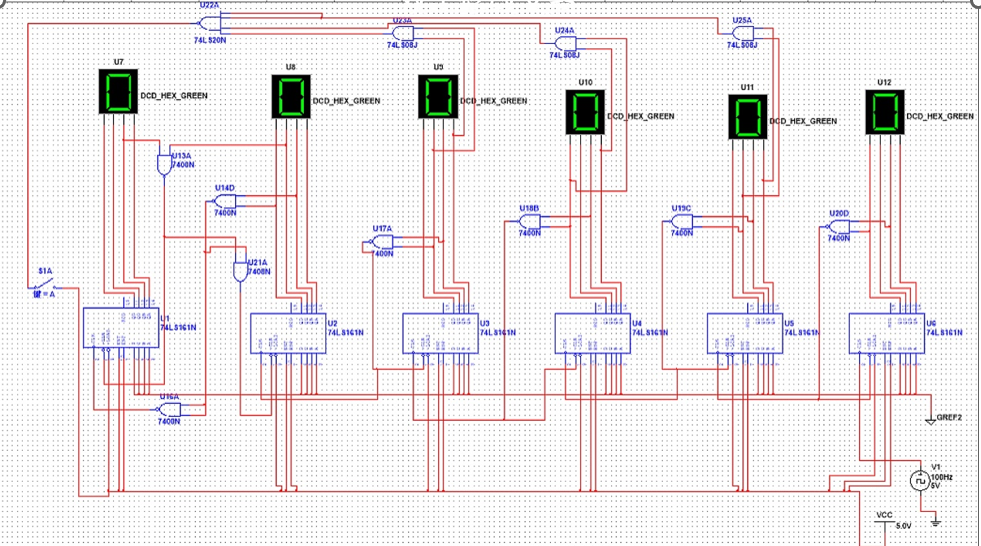

二、总体方案:像搭积木一样拼数字钟

核心逻辑是"下一级触发上一级":1Hz秒脉冲先给秒模块,秒到59触发分模块加1,分到59触发小时模块加1,小时到23清零,形成循环。整体框图一看就懂:

1Hz秒脉冲 → 秒模块(60进制,00~59)→ 分模块(60进制,00~59)→ 小时模块(24进制,00~23)

↓ ↓ ↓

秒数码管(2个) 分数码管(2个) 小时数码管(2个)每个模块的核心都是"2片74HC161":1片做"个位(09,10进制)",1片做"十位(05/0~2,6/2进制)",再用与非门设计"到目标值清零"的逻辑。

三、核心模块设计:从秒到小时,分步实操

每个模块的设计逻辑相通(都是"个位+十位"),以"秒模块"为例讲透,分模块和小时模块可直接套用逻辑。

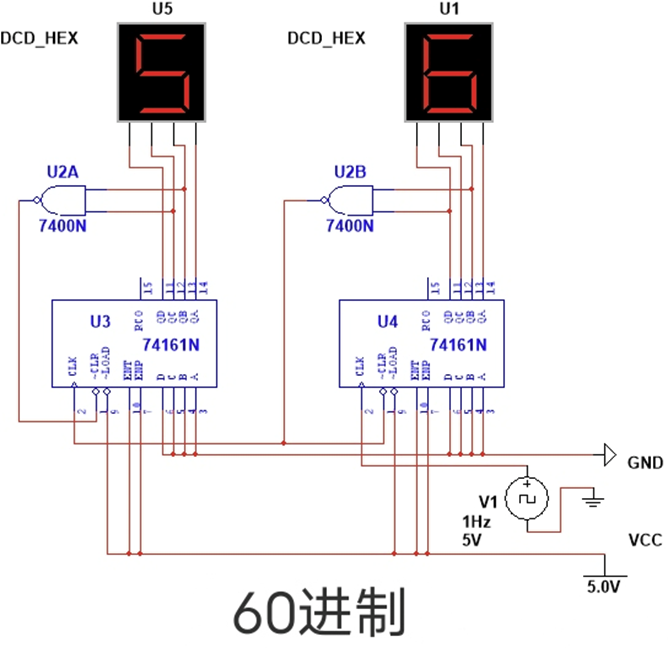

模块1:秒模块(60进制,00~59,秒到59向分进位)

1. 原理:60进制="十位6进制(05)+个位10进制(09)"

- 个位计数器(U1:74HC161):10进制(0~9),到9时向十位计数器发进位;

- 十位计数器(U2:74HC161):6进制(0~5),到5且个位到9时(合计59),触发秒模块整体清零,并向分模块发进位;

- 清零逻辑:用74HC00与非门,当U2的Q2=1(4)、Q0=1(1)(十位=5)且U1的Q3=1(8)、Q0=1(1)(个位=9)时,与非门输出低电平,同时清零U1和U2。

2. 接线步骤(Multisim里实操)

- 电源与使能 :U1和U2的VCC(16脚)接5V,GND(8脚)接GND;

CEP(7脚)、CET(10脚)接VCC(高电平=允许计数); - 时钟输入 :U1的

CLK(2脚)接1Hz秒脉冲(Multisim里搜"Clock Voltage Source",设1Hz); - 个位→十位进位 :U1的

TC(11脚,进位端,计满10时输出1)接U2的CLK(2脚); - 清零逻辑 :

- 74HC00(2输入与非门):第一个与非门接U2的

Q2(14脚)、Q0(12脚)(十位=5); - 第二个与非门接U1的

Q3(15脚)、Q0(12脚)(个位=9); - 第三个与非门接前两个与非门的输出,最终输出接U1和U2的

CR(1脚,低电平清零);

- 74HC00(2输入与非门):第一个与非门接U2的

- 秒→分进位 :U2的

TC(11脚)接分模块U3的CEP和CET(分模块的使能端,秒到59时TC=1,允许分计数); - 显示 :U1的

Q3~Q0(15~12脚)接秒个位数码管(DCD_HEX),U2的Q2~Q0接秒十位数码管。

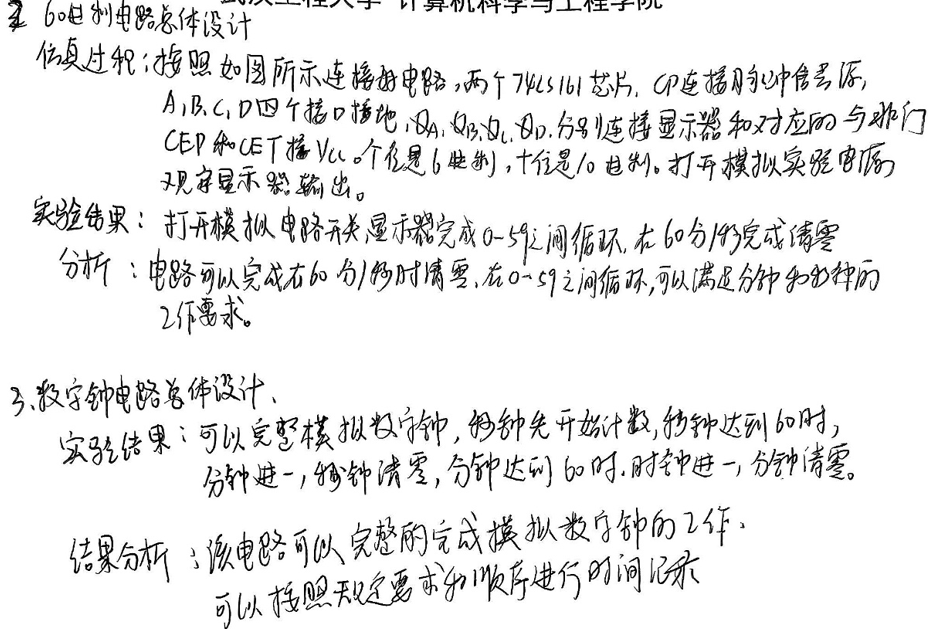

3. Multisim仿真验证

- 运行仿真:看秒数码管从00→01→...→59→00循环,每1秒变1次;

- 查进位:秒到59时,分模块的数码管是否加1(比如初始00→01),是则进位正常。

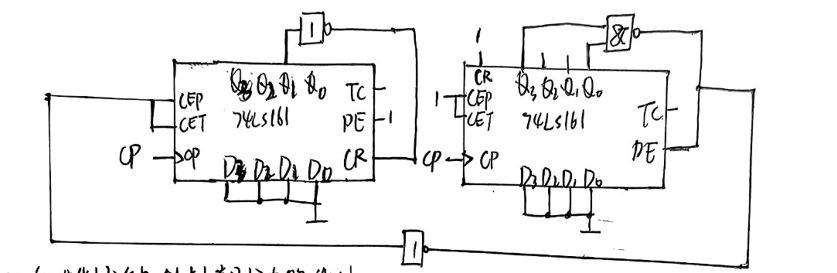

模块2:分模块(60进制,00~59)

和秒模块完全一样!唯一区别是:

- 时钟使能:分模块U3的

CEP/CET接秒模块U2的TC(秒到59时才允许分计数); - 分→小时进位:分模块U4的

TC接小时模块U5的CEP/CET(分到59时向小时进位)。

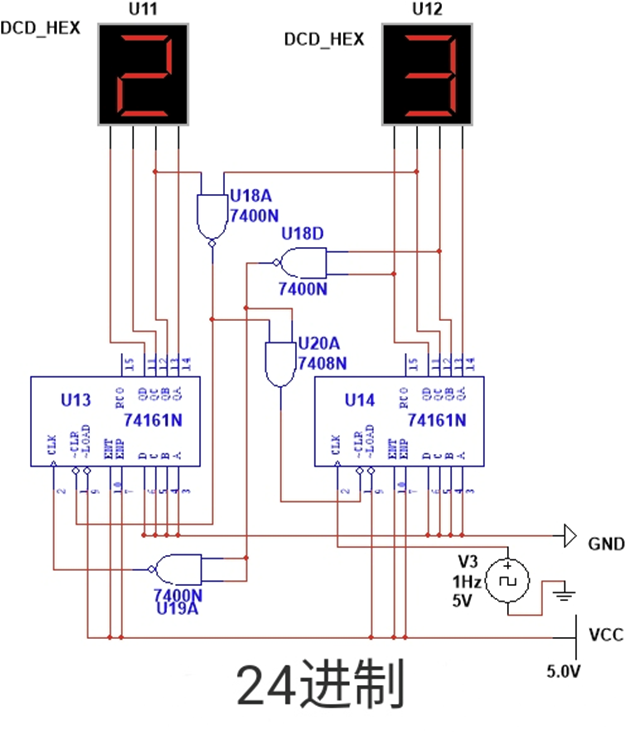

模块3:小时模块(24进制,00~23)

1. 原理:24进制="十位2进制(02)+个位10进制(09)"

- 个位计数器(U5:74HC161):10进制(0~9),到9时向十位计数器发进位;

- 十位计数器(U6:74HC161):2进制(0~2),到2且个位到3时(合计23),触发整体清零;

- 清零逻辑:74HC00与非门,接U6的

Q1(2脚,十位=2)和U5的Q1(2脚,个位=3),输出接U5和U6的CR。

2. 关键接线差异

- 时钟使能:U5的

CEP/CET接分模块U4的TC(分到59时才允许小时计数); - 无进位输出:小时到23清零后,不向其他模块发进位(24小时循环)。

3. 仿真验证

- 小时数码管从00→01→...→23→00循环,分到59时小时加1(比如23:59→00:00),则正常。

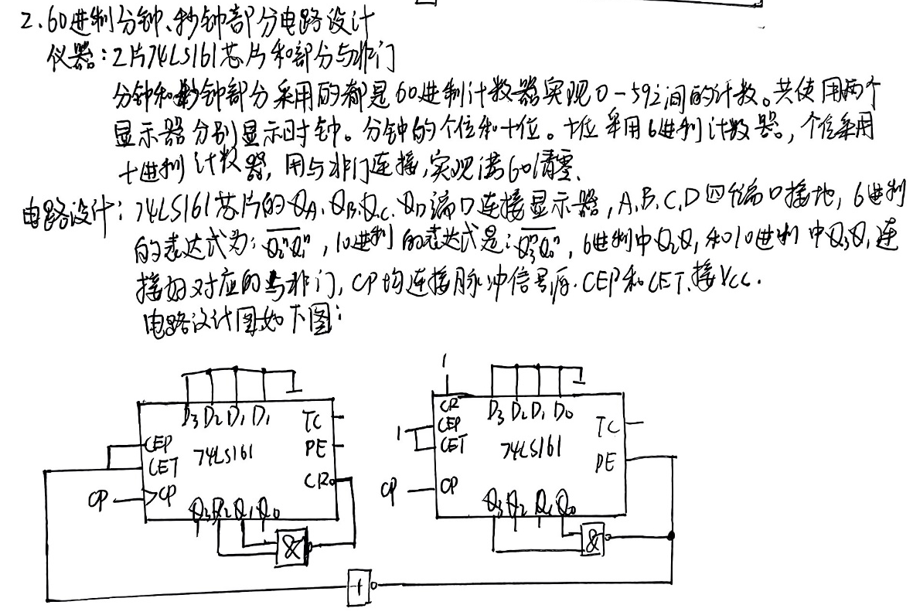

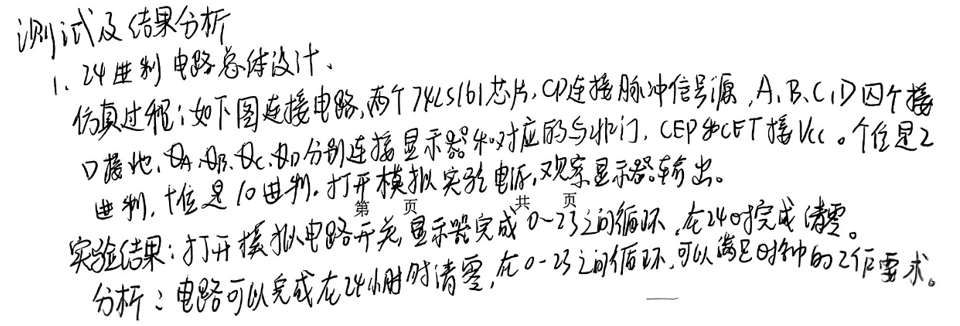

四、系统联调:3步搞定"时:分:秒"联动

- 查模块独立工作:先单独仿真秒、分、小时模块,确保每个模块进制正确(秒60、分60、小时24);

- 查进位链路:秒→分、分→小时的进位端是否接对,仿真看"秒59→分+1""分59→小时+1"是否触发;

- 查显示:数码管是否对应"时:分:秒",比如秒05、分12、小时18,显示"18:12:05",无错位或乱码。

五、新手必避坑

- 74HC161使能端忘接高电平 :

CEP/CET必须接VCC,否则计数器不计数,数码管一直显示00; - 进位端接反 :把秒的

TC接分的CLK( instead ofCEP),导致分模块每秒都计数,不是60秒加1; - 清零逻辑引脚接错:小时24进制的清零条件是"十位2+个位3"(23),别接成"十位2+个位9"(29),否则小时到29才清零;

- 数码管没接译码器:直接把74HC161的输出接数码管,导致显示乱码,需用74HC4511(BCD-七段译码器)转换;

- Multisim时钟设错 :把1Hz时钟设成1kHz,秒数跳得太快看不清,需在时钟属性里把"Frequency"设为1。

六、总结:数字钟设计的核心逻辑

数字钟的本质是"模块化+信号联动":先把复杂的"计时"拆成秒、分、小时三个小问题,每个小问题用"2片74HC161+与非门"解决进制和清零,再用进位信号把模块串起来,最后用数码管显示。不管是24进制还是60进制,核心都是"找到目标值的二进制,设计清零逻辑",跟着这个思路,其他进制的计数器也能轻松实现。