深入浅出解析时序基础,让复杂概念变得生动易懂

《FPGA基础知识》系列导航

本专栏专为FPGA新手打造的Xilinx平台入门指南。旨在手把手带你走通从代码、仿真、约束到生成比特流并烧录的全过程。

本篇是该系列的第十篇内容

上一篇:****FPGA基础知识(九):时序约束常见问题与解决方案深度解析-CSDN博客

下一篇:****FPGA基础知识(十一):时序约束参数确定--从迷茫到精通-CSDN博客

1 引言

在数字电路设计中,有两个概念如同交通规则般重要,却又常常让人困惑------它们就是建立时间和保持时间。今天,让我们用一场精彩的舞蹈来诠释这些技术概念。

舞池中的完美配合

想象一个专业的交谊舞池:

-

💃 男伴 代表数据信号,负责引导动作和传递信息

-

🕺 女伴 代表触发器,接收并响应男伴的引导

-

🎵 音乐的鼓点 代表时钟边沿,规定动作发生的精确时刻

现在,考虑一个完美的托举动作:

建立时间 就像男伴需要在鼓点响起之前就提前摆好姿势、站稳脚步。他不能在最后一刻才匆忙准备。

保持时间 则像鼓点响起后,男伴还需要继续保持托举姿势片刻,确保女伴安全落地。他不能立刻松手去准备下一个动作。

2 技术本质:当舞蹈遇见物理现实

2.1 建立时间:提前准备的哲学

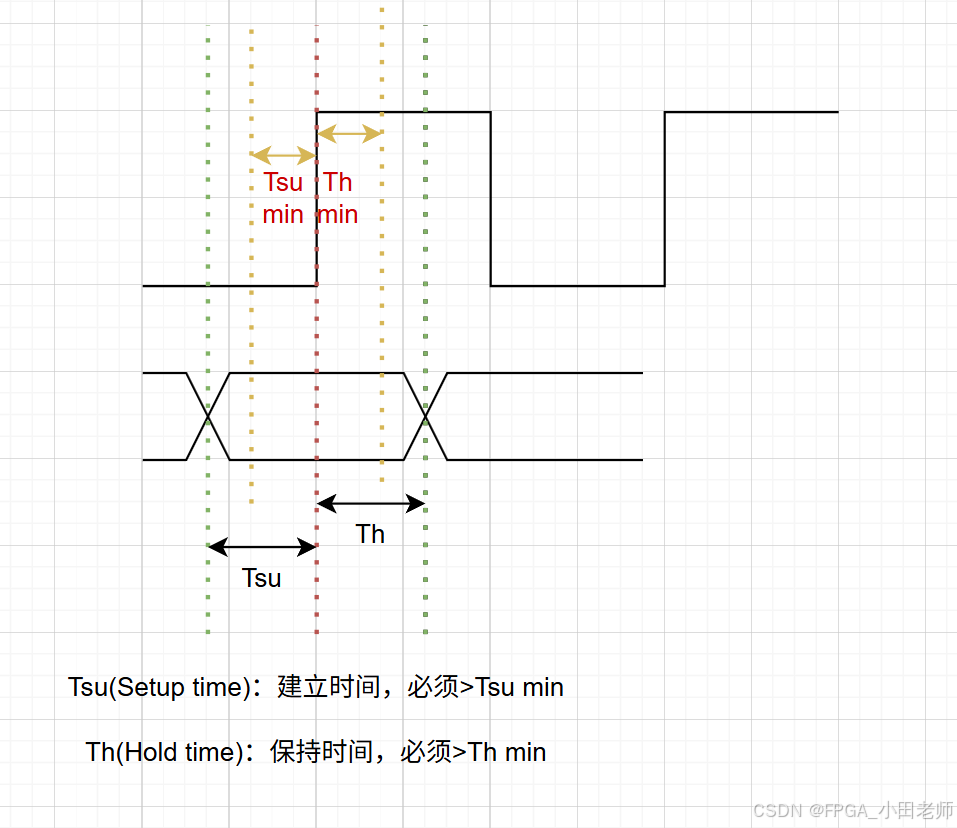

定义 :在时钟有效边沿到来之前 ,输入数据必须保持稳定的最短时间。

物理意义:触发器内部需要时间来"感知"输入数据。当时钟边沿到来时,内部的晶体管、电容需要完成状态切换和充电过程。

2.2 保持时间:持续稳定的艺术

定义 :在时钟有效边沿到来之后 ,输入数据必须继续维持稳定的最短时间。

物理意义:确保当时钟边沿触发后,新捕获的数据有足够时间在触发器内部"安顿下来"。

3 常见问题场景与诊断

3.1 建立时间违例:迟到的代价

典型场景1:组合逻辑过长

// 问题代码:多级复杂运算在一个周期内完成

module timing_violation_example (

input clk,

input [15:0] a, b, c, d, e, f,

output reg [31:0] result

);

// 过长的组合逻辑链 - 建立时间违例!

always @(posedge clk) begin

result <= (a * b + c * d) / (e - f);

// 乘法→加法→减法→除法,延迟累积超标

end

endmodule症状:时序报告显示WNS为负值,关键路径延迟超过时钟周期

解决方案:流水线拆分

// 解决方案:流水线拆分

module pipeline_fix_example (

input clk,

input [15:0] a, b, c, d, e, f,

output reg [31:0] result

);

reg [31:0] stage1, stage2, stage3;

always @(posedge clk) begin

// 第一级:并行乘法

stage1 <= a * b;

stage2 <= c * d;

stage3 <= e - f;

// 第二级:加法+除法

result <= (stage1 + stage2) / stage3;

end

endmodule典型场景2:高扇出网络

-

一个信号驱动太多负载

-

布线延迟显著增加

-

常见于复位信号、使能信号

// 问题代码:单个信号驱动过多负载

module high_fanout_problem (

input clk,

input enable, // 这个信号驱动32个寄存器!

input [31:0] data_in,

output reg [31:0] data_out

);

reg [31:0] reg1, reg2, reg3, reg4, reg5, reg6;

// ... 还有26个类似的寄存器always @(posedge clk) begin if (enable) begin // enable扇出极大! reg1 <= data_in; reg2 <= data_in + 1; reg3 <= data_in + 2; // ... 所有32个寄存器都用enable end endendmodule

解决方案:寄存器复制

// 解决方案:寄存器复制

module fanout_fix_example (

input clk,

input enable,

input [31:0] data_in,

output reg [31:0] data_out

);

// 复制enable信号,每个驱动部分负载

reg enable_copy1, enable_copy2, enable_copy3;

always @(posedge clk) begin

enable_copy1 <= enable;

enable_copy2 <= enable;

enable_copy3 <= enable;

end

// 现在每个复制信号只驱动10-11个寄存器

always @(posedge clk) begin

if (enable_copy1) begin

reg1 <= data_in;

// ... 驱动10个寄存器

end

if (enable_copy2) begin

reg11 <= data_in;

// ... 驱动10个寄存器

end

// ... 以此类推

end

endmodule典型场景3:跨时钟域路径

-

不同时钟域间的数据传输

-

缺乏适当的同步电路

-

时序约束不完整

// 问题代码:直接跨时钟域传输

module cdc_problem (

input clk_a, // 100MHz

input clk_b, // 50MHz

input data_a,

output reg data_b

);

// 建立时间违例风险!

always @(posedge clk_b) begin

data_b <= data_a; // 直接从clk_a域采样

end

endmodule

解决方案:双寄存器同步链

/ 解决方案:双寄存器同步器

module cdc_fix_example (

input clk_a,

input clk_b,

input data_a,

output reg data_b

);

reg sync_reg1, sync_reg2;

// 双寄存器同步链

always @(posedge clk_b) begin

sync_reg1 <= data_a; // 可能进入亚稳态

sync_reg2 <= sync_reg1; // 大概率稳定

data_b <= sync_reg2; // 安全使用

end

endmodule3.2 保持时间违例:过早的麻烦

典型场景1:直通路径

症状:数据变化太快,在时钟沿后立即改变

// 问题代码:几乎没有组合逻辑

module short_path_problem (

input clk,

input data_in,

output reg data_out

);

// 保持时间违例风险!

always @(posedge clk) begin

data_out <= data_in; // 数据几乎直接通过

end

endmodule解决方案:插入LUT延迟

// 解决方案:插入LUT延迟

module short_path_fix (

input clk,

input data_in,

output reg data_out

);

// 插入3级LUT延迟链

wire delay1 = ~data_in; // LUT作为反相器

wire delay2 = ~delay1; // 再反相回来

wire delayed_data = ~delay2; // 最终反相

always @(posedge clk) begin

data_out <= delayed_data; // 现在有足够延迟

end

endmodule典型场景2:时钟偏移过大

-

发送端和接收端时钟到达时间差异大

-

时钟树平衡不佳

-

接收端时钟早于发送端时钟

// 问题场景:时钟树不平衡

module clock_skew_problem (

input clk,

input [7:0] data_in,

output reg [7:0] data_out

);

reg [7:0] intermediate;// 假设由于布局问题: // - clk到达intermediate寄存器:延迟0.3ns // - clk到达data_out寄存器:延迟0.1ns // 结果:数据过早到达data_out! always @(posedge clk) begin intermediate <= data_in + 1; data_out <= intermediate; // 保持时间违例! endendmodule

解决方案:约束时钟树

// 解决方案:约束时钟树

// 在SDC约束文件中:

# 增加时钟不确定性约束

set_clock_uncertainty -hold 0.05 [get_clocks clk]

set_clock_latency -source 0.2 [get_clocks clk]

set_clock_latency 0.3 [get_clocks clk]典型场景3:布局不合理

-

前后级寄存器物理位置太近

-

布线延迟过短

-

数据过早到达目标寄存器

// 问题代码:物理位置过于接近

module placement_problem (

input clk,

input [3:0] a, b,

output reg [3:0] result

);

reg [3:0] temp;// 布局后: // - 寄存器temp在SLICE_X1Y1 // - 寄存器result在SLICE_X1Y2 // 布线延迟只有0.05ns → 太短! always @(posedge clk) begin temp <= a & b; // 简单逻辑 result <= temp; // 保持时间违例! endendmodule

解决方案:布局约束或逻辑调整

// 解决方案:布局约束或逻辑调整

module placement_fix (

input clk,

input [3:0] a, b,

output reg [3:0] result

);

reg [3:0] temp;

wire [3:0] delayed_temp;

// 方法1:插入逻辑延迟

assign delayed_temp = ~(~temp); // 2级LUT延迟

// 方法2:合并逻辑

always @(posedge clk) begin

// 直接计算,避免短路径

result <= a & b;

end

endmodule4 系统化解决方案

4.1 建立时间违例修复策略

4.1.1 架构级优化:流水线设计

// 修复方案:四级流水线分解长路径

reg [31:0] stage1, stage2, stage3, stage4;

always @(posedge clk) begin

// 第一级:乘法运算

stage1 <= a * b;

stage2 <= c * d;

// 第二级:加法和减法

stage3 <= stage1 + stage2;

stage4 <= e - f;

// 第三级:乘法

stage5 <= g * h;

// 第四级:最终计算

result <= stage3 / stage4 + stage5;

end4.1.2 逻辑级优化:操作符平衡

// 优化前:不平衡加法树

result = a + b + c + d + e + f + g + h; // 7级逻辑深度

// 优化后:平衡加法树

wire [7:0] sum1 = a + b;

wire [7:0] sum2 = c + d;

wire [7:0] sum3 = e + f;

wire [7:0] sum4 = g + h;

wire [7:0] sum12 = sum1 + sum2;

wire [7:0] sum34 = sum3 + sum4;

result = sum12 + sum34; // 仅3级逻辑深度4.1.3 物理级优化:布局约束

# 关键路径分组约束

group_path -name critical_path -from [get_pins start_reg/C] -to [get_pins end_reg/D]

# 区域约束:将相关逻辑布局在相邻区域

create_pblock critical_region

add_cells_to_pblock critical_region [get_cells {start_reg comb_logic* end_reg}]

resize_pblock critical_region -add {SLICE_X10Y10:SLICE_X30Y30}4.2 保持时间违例修复方案

4.2.1 延迟插入技术

// 修复方案:插入LUT延迟链

module hold_fix (

input clk,

input data_in,

output reg data_out

);

// 插入2级LUT延迟

wire delay1 = ~data_in; // 第一级延迟

wire delay2 = ~delay1; // 第二级延迟

wire delayed_data = ~delay2; // 第三级延迟

always @(posedge clk) begin

data_out <= delayed_data;

end

endmodule4.2.2 时钟树优化

# 增加时钟不确定性约束

set_clock_uncertainty -hold 0.05 [get_clocks clk]

# 设置生成时钟约束

create_generated_clock -name clk_div2 \

-source [get_pins mmcm/CLKIN] \

-divide_by 2 [get_pins mmcm/CLKOUT0]4.2.3 寄存器复制

// 高扇出信号的寄存器复制

(* EQUIVALENT_REGISTER_REMOVAL="NO" *)

reg control_signal_1, control_signal_2, control_signal_3;

always @(posedge clk) begin

control_signal_1 <= original_control;

control_signal_2 <= original_control;

control_signal_3 <= original_control;

end

// 每个副本驱动一个区域,减少单个负载5 实用调试技巧

5.1 时序分析命令

# 建立时间分析

report_timing -max_paths 10 -setup -slack_less_than 0.5 \

-nworst 3 -unique_pins -name setup_violations

# 保持时间分析

report_timing -max_paths 10 -hold -slack_less_than 0 \

-nworst 5 -name hold_violations

# 路径详情分析

report_timing -from [get_pins start_reg/C] \

-to [get_pins end_reg/D] -delay_type min_max5.2 关键指标解读

-

WNS (Worst Negative Slack):最差负裕量,必须 > 0

-

TNS (Total Negative Slack):总负裕量,反映整体质量

-

WHS (Worst Hold Slack):最差保持时间裕量

-

Failing Endpoints:违例端点数量

6 预防性设计指南

设计阶段的最佳实践

1. 合理时钟规划

-

根据设计复杂度选择适当的时钟频率

-

为时钟网络预留足够的资源

-

考虑时钟域交叉的同步方案

2. 代码编写规范

// 好的实践:寄存器输出

always @(posedge clk) begin

reg1 <= comb_logic1;

reg2 <= comb_logic2; // 明确的流水线阶段

end

// 避免:过长的组合逻辑链

assign long_chain = a + b + c + d + e + f + g + h;3. 约束完整性

# 完整的时序约束示例

create_clock -period 10 -name clk [get_ports clk]

set_input_delay 2.0 -clock clk [all_inputs]

set_output_delay 1.5 -clock clk [all_outputs]

set_clock_uncertainty -setup 0.1 -hold 0.05 [get_clocks clk]总结:掌握数字节奏的艺术

建立时间和保持时间违例的解决需要系统化的方法:

建立时间违例就像舞者动作太慢,解决方案是:

-

简化动作(优化逻辑)

-

放慢音乐(降低频率)

-

优化位置(改善布局)

保持时间违例就像舞者动作太快,解决方案是:

-

增加衔接(插入延迟)

-

调整节奏(平衡时钟)

-

重新编排(修改架构)

记住这个设计哲学:优秀的时序不是偶然获得的,而是通过精心的设计和持续的优化实现的。 当你深入理解这些概念后,时序收敛将从一个令人头疼的问题,转变为可以系统化解决的设计挑战。

在数字电路的世界里,掌握建立时间和保持时间的艺术,就是掌握了让电路稳定运行的节奏感。愿你在设计的舞台上,跳出最完美的数字之舞!