概述

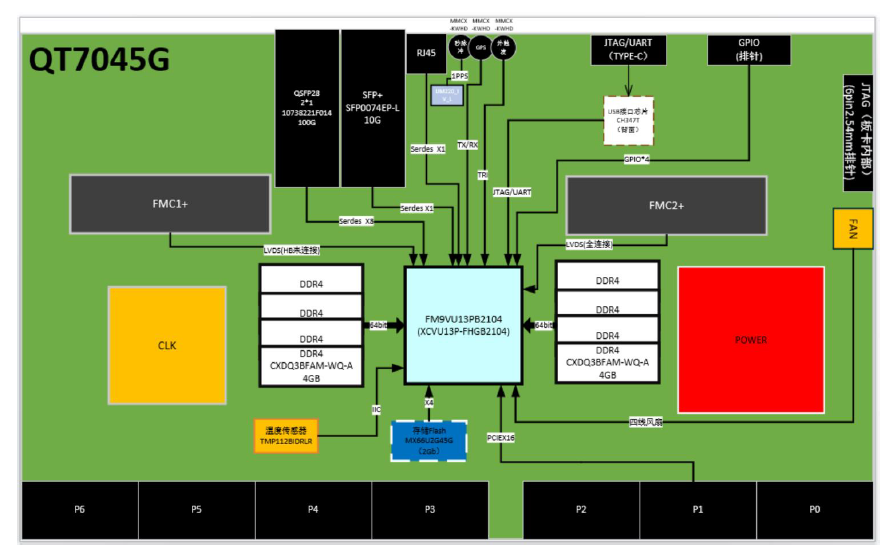

基于VU13P的6U VPX 载板是一款高性能的6U VPX 载板。板载2 个 HSPC形式的FMC

+连接器。板卡选用了 1 片XCVU13P-FHGB2104作为主控芯片,搭配两组每组4 颗1GB/16bit 的DDR4 缓存颗粒,共8GB 容量,和 1 颗2Gb 的加载QSPI Flash。

板卡对外提供一个RJ45千兆网口,一个排针式的JTAG口,一个排针式的GPIO 口(可支持4 路标准3.3V 的GPIO 信号),一个TYPE C 形式的USB 接口(可支持UART或者JTAG),一个10Gbps 的SFP+光纤接口,一个外触发,一个GPS 信号接口和一个PPS 信号输出接口,和2 个能支持100Gbps 的ZQSFP 光纤接口。

另外,QT7045G 通过VPX P1接口对外提供一路x16 的PCIE 通道。通过2 个HSPC 形式的FMC+(VITA57.4)接口向外部提供丰富、高速且可配置的数字I/O 资源。

其中一路为全功能,可提供84 对高速差分线(含LA,HA,HB BANK 和4 对差分时钟线)、1 组共2 对参考时钟线、1 组共2 对同步时钟线、24 组共48 对超高速 DP 差分对及6 对超高速差分时钟线;另一路可提供62 对高速差分线(含LA,HA BANK 和4 对差分时钟线)、1 组共2 对参考时钟线、1 组共2 对同步时钟线、24组共48 对超高速DP 差分对及 6 对超高速差分时钟线。

客户可以根据应用需求灵活地选择FMC 子卡或者 FMC+子卡,比如 ADC 子卡、DAC 子卡以及光纤子卡等。同时可支持 Windows,Linux 上位机驱动。便于构建灵活、高效的开发及使用环境。

应用:

• FPGA 信号处理

• 实时多算法处理的在线测试验证

• 测试测量快速环境搭建

• 无线、国防应用

产品特性:

• FPGA 默认为1 片Xilinx 公司的XCVU13P-FHGB2104,或者

XCVU11P-FHGB2104;

• 提供一路全功能型标准HSPC(VITA 57.4)子卡接口,另一路

HSPC子卡接口只是少了HB BANK 的22 对高速差分线;

• 板载2 组4GB 的高速DDR4 缓存,共8GB;

• 板载1 颗2Gb 的QSPI Flash;

• 前面板一个TYPE C 形式的USB 接口,可支持UART 或者JTAG;

• 板卡内部一个6pin 排针式JTAG 调试接口;

• 前面板一个RJ45 千兆网接口;

• 前面板一个排针式GPIO 接口;

• 前面板SSMC 形式的外触发接口一个,GPS 信号接口一个和PPS 信

号输出接口一个;

• 前面板一个10Gbps 的SFP+光纤接口和2 个能支持100Gbps的

ZQSFP光纤接口;

• 具备温度监控功电路;

• 标准VPX 背板单独12V 供电;

• 标准6U VPX 规范,P1 接口对外提供一路x16 的PCIE 通道;

• 支持导冷散热;