参考附件

F280049C Enhanced Pulse Width Modulator (ePWM)_tms320f280049c 学习笔记 epwm-CSDN博客

TMS320F280049C 学习笔记7 ePWM_280049epwm-CSDN博客

C2000 epwm使用笔记 (Driverlib) - Fun_Cheong's

TMS320F28069的EPWM模块同步设置_sysctrlregs.pclkcr0.bit.tbclksync-CSDN博客

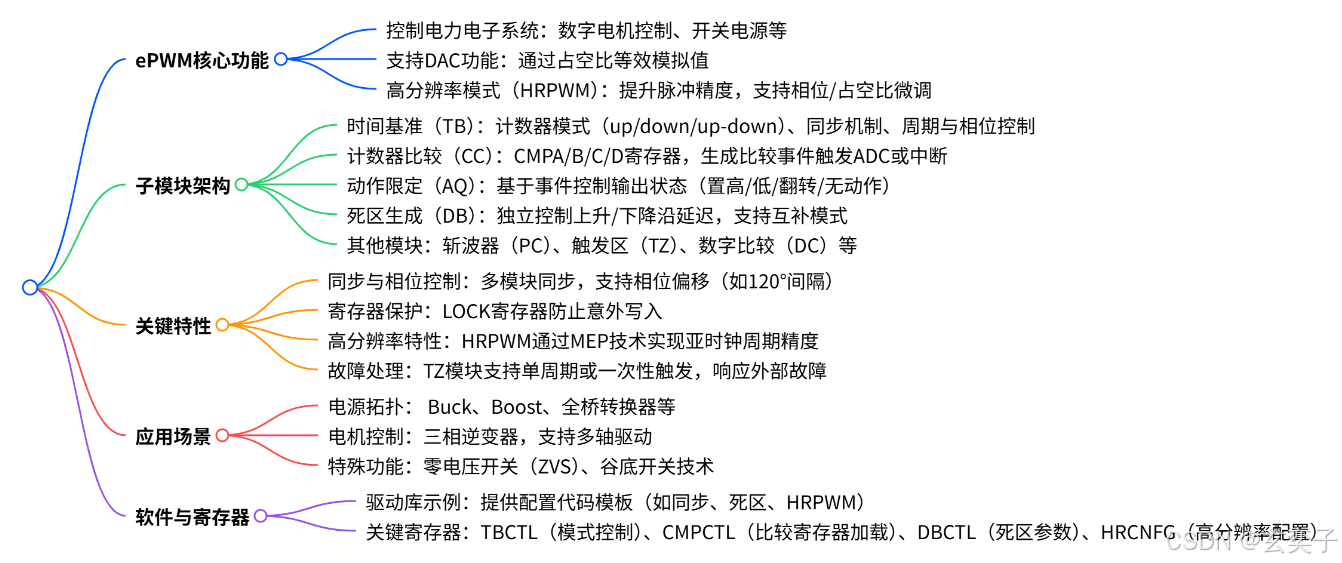

思维导图

增强型脉宽调制器(ePWM)外设是控制许多商业和工业设备中电力电子系统的关键元素,这些系统一般包括数字电机控制,开关电源控制,不间断电源控制和其他形式的功率转换系统

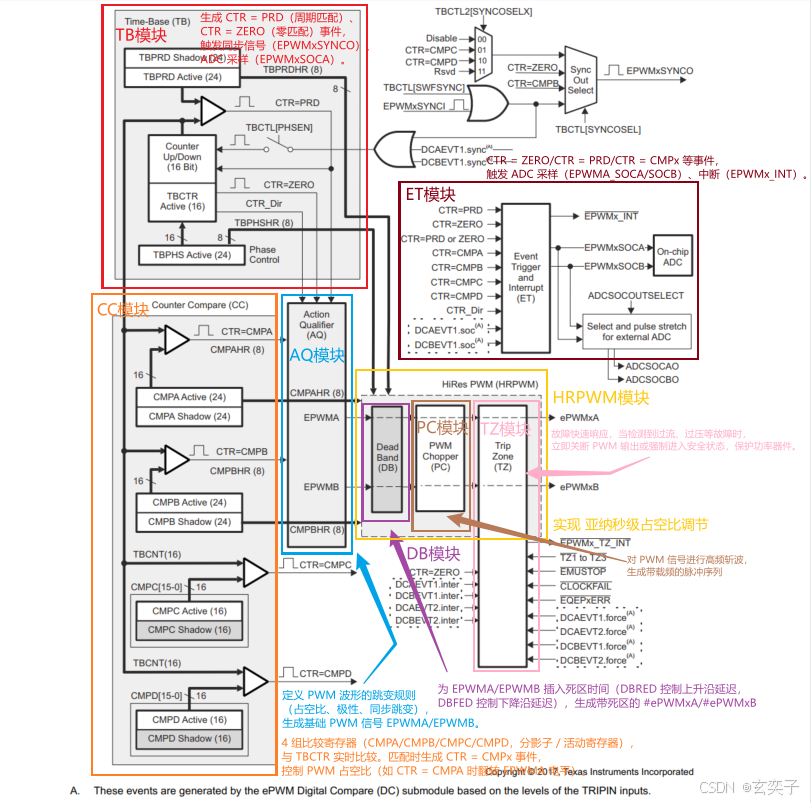

ePWM 模块主要组件

**时基模块 (TB):**控制 PWM 的频率、周期与计数模式,实现多模块同步运行。

**计数器比较模块 (CC):**与时基计数器进行比较,决定 PWM 的占空比或触发事件。

**动作限定器模块 (AQ):**根据比较结果或触发条件控制 ePWM 输出高低电平或翻转。

**死区控制模块 (DB):**在互补 PWM 输出间插入可配置的死区时间,避免上下桥直通。

**PWM 斩波模块 (PC):**将 PWM 输出调制为高频斩波形式,用于脉冲变压器驱动等场景。

**故障处理模块 (TZ):**检测外部故障信号(如过流/欠压)后立即关闭 PWM,确保安全。

**事件触发模块 (ET):**在指定时间点触发 ADC 转换或中断,支持事件计数器分频。

**数字比较模块 (DC):**通过比较器或 TRIP 信号产生精确定义的事件或保护响应。

**高分辨率模块 (HRPWM):**提供亚系统时钟级调节精度,实现超高精度的占空比/相位/周期控制。

EPWM模块及其关键信号框图

位于手册第1896页"Figure 18-3. ePWM Modules and Critical Internal Signal Interconnects"

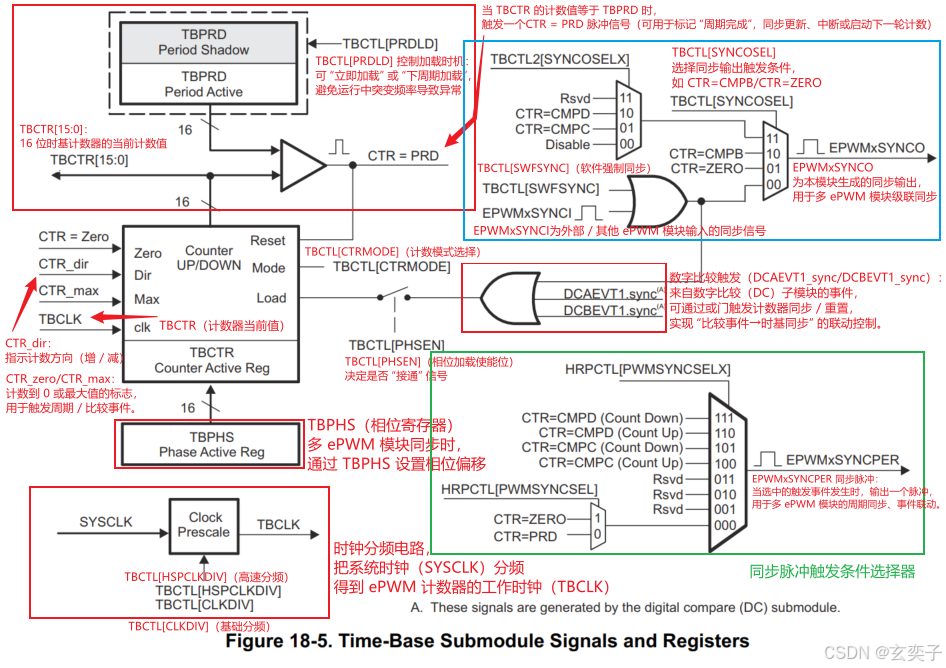

时间基准子模块(TB)

功能总结

控制PWM频率和周期,通过TBPRD寄存器设置周期值。

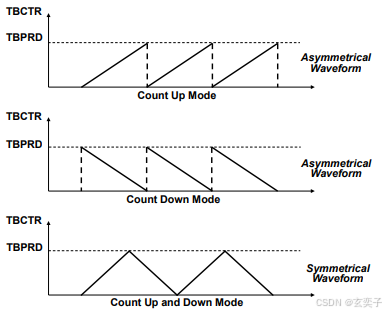

计数模式:增计数(Up)、减计数(Down)、增减计数(Up-Down)。

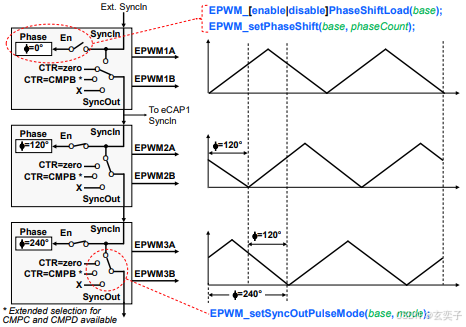

同步机制:通过EPWMSYNCI/EPWMSYNCO实现多模块同步,支持相位调节(TBPHS)。

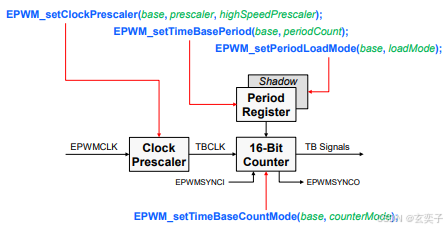

电路结构

时钟

用于 EPWM 计数器的时钟最初源自器件的系统时钟。一个可配置的时钟分频器对系统时钟进行分频,以生成 EPWM 时钟 (EPWMCLK)。然后,可以使用 EPWM 时钟预分频器值来进一步对 EPWM 时钟进行分频,从而用于 EPWM 计数器和 EPWM 时基周期寄存器。计数器和时基周期值控制所生成 EPWM 波形的频率和周期。

-

预分频器计算:

时基时钟

TBCLK= EPWMCLK / (HSPCLKDIV * CLKDIV)时钟预分频器 = HSPCLKDIV * CLKDIV

影子寄存器

许多 EPWM 寄存器,例如时基周期寄存器,也具有影子寄存器。影子寄存器就像一个缓冲器,允许寄存器更新与 EPWM 计数器或特定(可配置)事件同步,并避免寄存器因被软件异步修改而发生损坏或虚假操作。

时基计数器可以使用以下三种模式之一运行:向上计数、向下计数和向上向下双向计数。请注意,向上计数和向下计数模式用于产生非对称波形,而向上向下双向计数模式用于产生对称波形。

向上计数模式

- 计数器从零开始递增计数,直至达到时基周期寄存器值,然后计数器复位为零并重新开始计数序列。

向下计数模式

- 计数器从时基周期寄存器值开始递减计数,直至达到零,然后计数器复位为周期值并重新开始向下计数序列。

向上/向下双向计数模式

- 计数器从零开始递增计数,直至达到时基周期寄存器值,然后计数器递减计数,直至达到零并重复上述计数序列。

同步

同步允许多个 EPWM 模块作为一个系统协同工作。同步基于称为 SYNC-IN 信号的输入信号。此外,如下图所示,波形还可以进行相移或偏移。

关键寄存器

TBCTL:计数模式、时钟分频、同步使能、相位使能。

TBPRD:PWM 周期值(支持影子寄存器)。

TBPHS:设置与其他 ePWM 同步的相位差。

TBCTR:当前计数值(只读)。

TBCLKSYNC:所有 ePWM 模块同步起始。

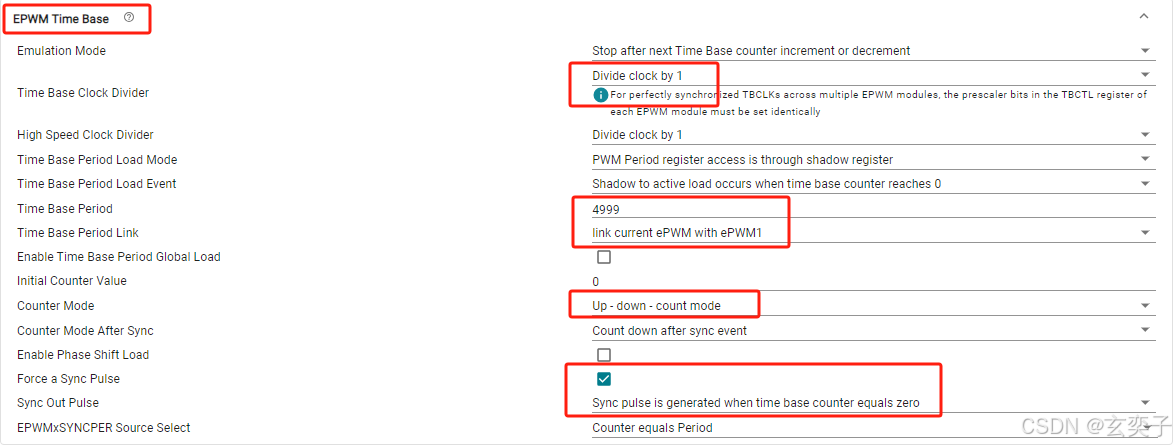

CCS配置

PWM的频率由时间基周期(TBPRD)寄存器以及时间基计数器的模式来控制。

我们这里采用计数模式(中心计数模式,采样点远离两边上升/下降沿的振铃)

STM32 PWM 计数器模式和对齐_stm32 pwm中心对齐-CSDN博客

STM32笔记之 PWM(脉宽调制)_pwm向上计数-CSDN博客

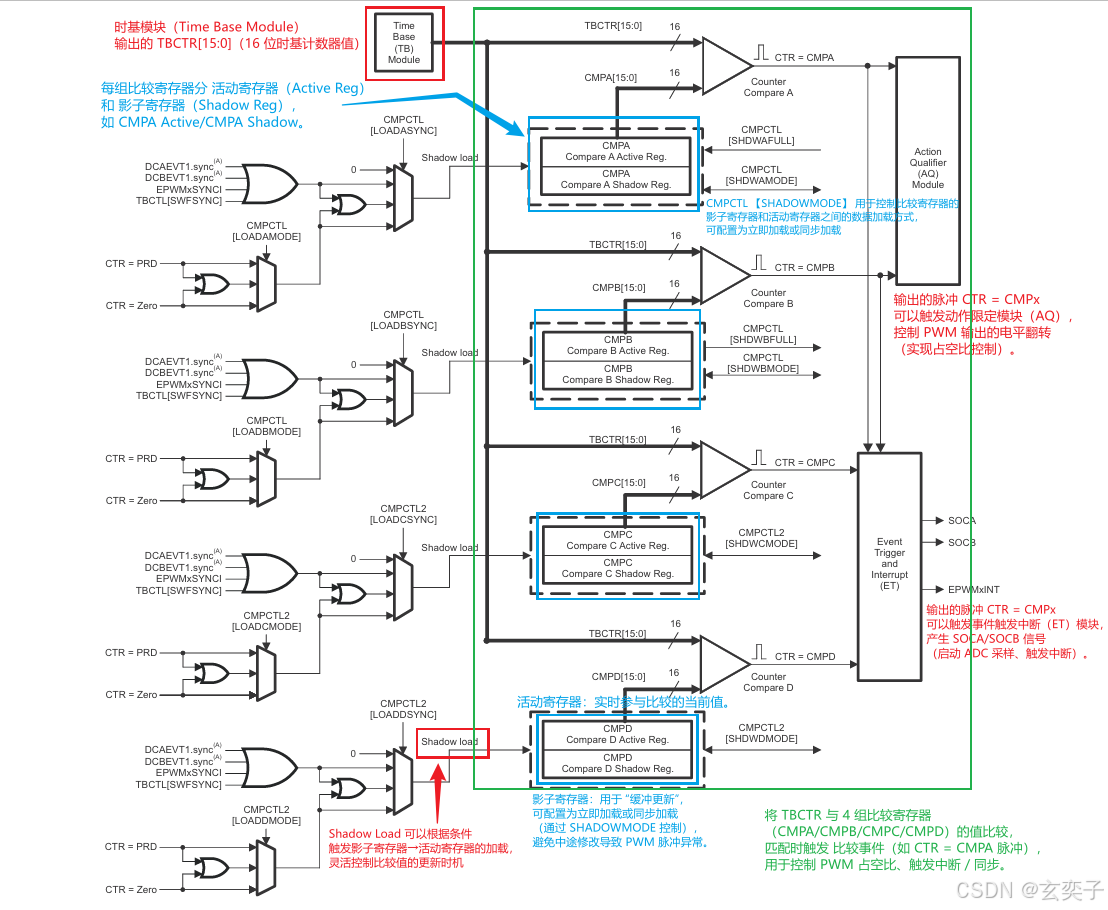

计数器比较子模块(CC)

功能总结

用于设置 PWM 的占空比,通过比较器 CMPA~CMPD 与 TBCTR 比较生成事件。

CMPA/CMPB 控制实际输出波形,占空比调节;CMPC/CMPD 常用于触发 ADC 或中断。

支持影子寄存器,防止波形更新时出现毛刺。

电路结构

关键寄存器

CMPA/CMPB/CMPC/CMPD:比较值。

CMPCTL / CMPCTL2:影子寄存器使能、加载模式配置。

CMPAHR/CMPBHR:高分辨率比较值(仅部分模块支持)。

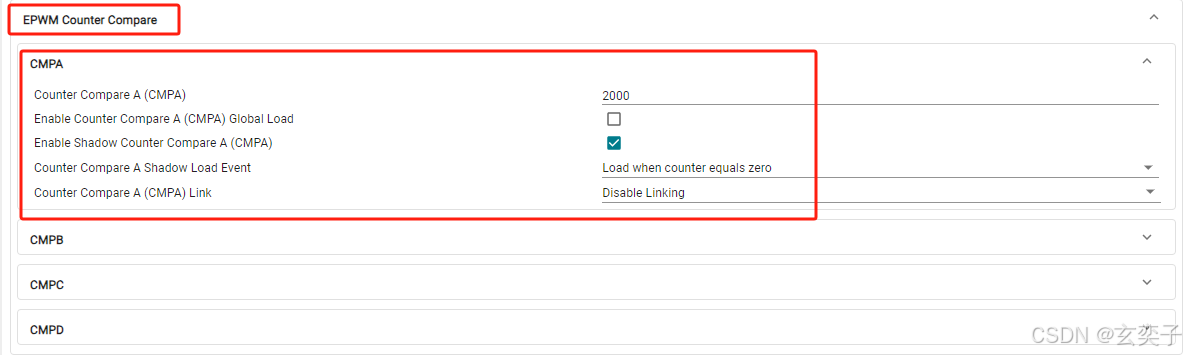

CCS配置

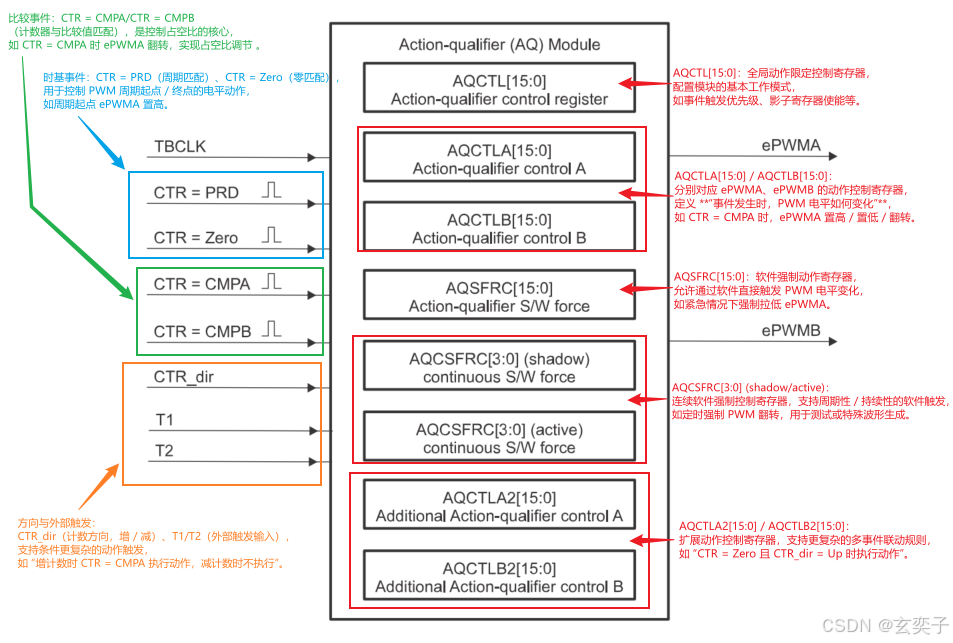

动作限定器子模块(AQ)

功能总结

定义 PWM 输出在特定事件(如 CTR=CMPA)时的行为:置位、清零、翻转或无操作。

支持单独配置 ePWMxA 和 ePWMxB。

支持通过软件强制控制输出状态,常用于调试和保护模式切换。

电路结构

关键寄存器

AQCTLA/AQCTLB:配置事件与对应的动作。

AQSFRC:软件强制输出设置。

AQCSFRC:软件控制强制输出 A/B 高/低电平。

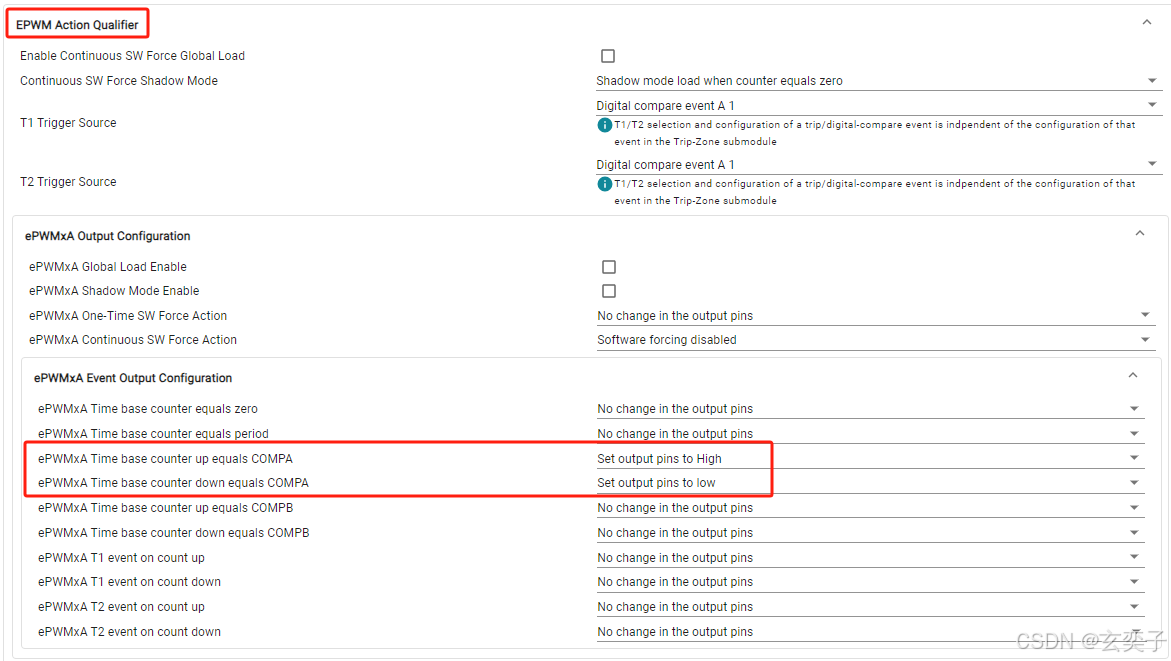

CCS配置

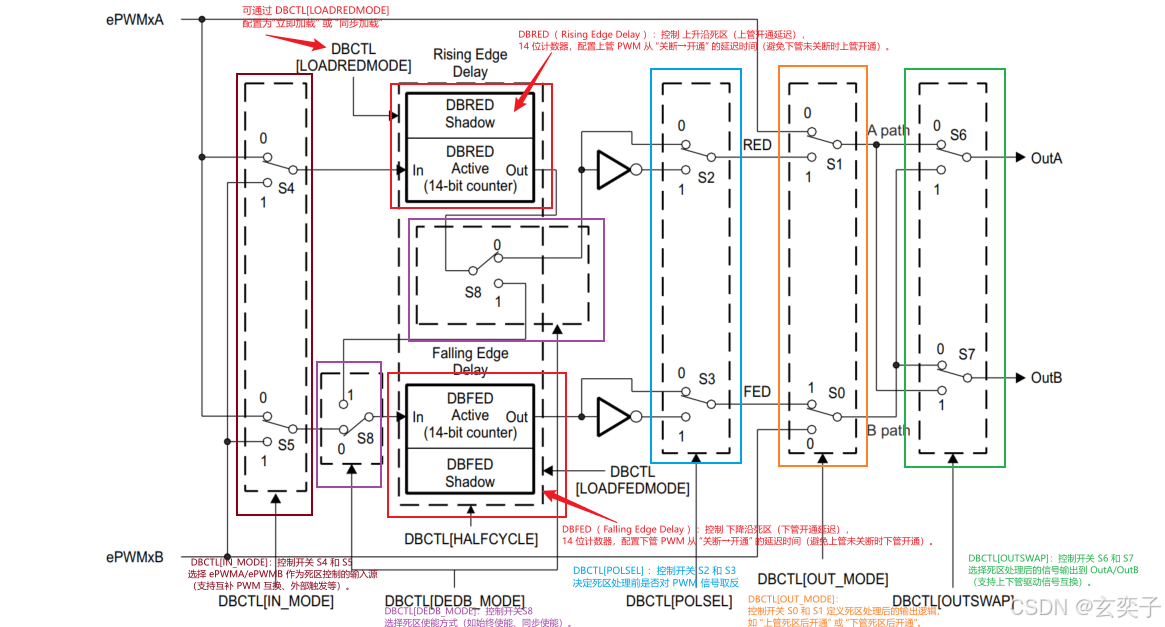

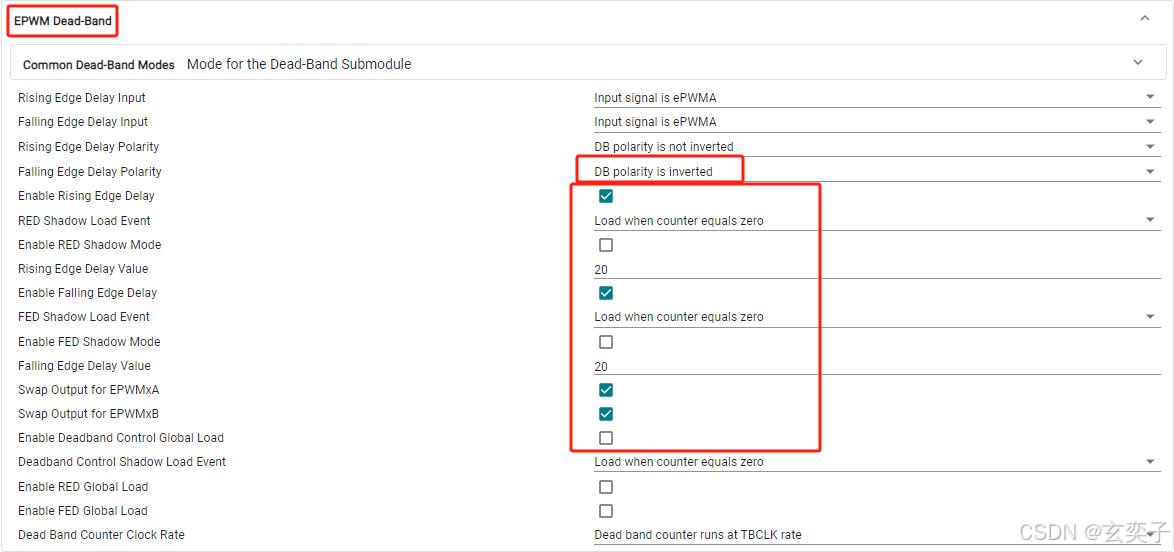

死区发生器子模块(DB)

功能总结

为 ePWMxA/B 输出添加互补死区(Dead-Time),防止上下桥臂直通。

独立设置上升沿延迟(RED)与下降沿延迟(FED)。

支持互补模式、极性翻转、高分辨率模式,适配多种驱动电路。

电路结构

关键寄存器

DBCTL:死区输出模式、极性配置、输入源选择。

DBRED:上升沿延迟时间。

DBFED:下降沿延迟时间。

HRDBCTL:高分辨率死区配置(如启用 DBREDHR/FEDHR)。

CCS配置

PWM斩波器子模块(PC)

功能总结

将 PWM 输出调制为高频脉冲包(斩波),用于隔离驱动或变压器耦合应用。

可配置第一个脉冲宽度、斩波频率与占空比。

可选择启用/旁路斩波功能。

关键寄存器

PCCTL:斩波使能、频率分频、占空比、初始宽度配置。

故障保护子模块(TZ)

功能总结

处理故障保护输入信号(如过流/过压),在触发时强制关闭 PWM 输出。

支持一次性响应(One-Shot)与周期性响应(Cycle-by-Cycle)。

可将输出拉高、拉低或置为高阻状态。

可结合 Digital Compare 实现精准硬件保护。

关键寄存器

TZSEL:选择启用的 Trip 输入源(TZ1~TZ6、DCAEVT、DCBEVT)。

TZCTL:触发后输出行为设置。

TZEINT:使能中断。

TZFLG/TZCLR:状态标志与清除。

CCS配置

数字比较子模块(DC)

功能总结

通过输入比较器(CMPSS)或 TRIPIN 生成保护事件(DCAEVT、DCBEVT)。

支持事件窗口(Blanking Window)、滤波器、同步触发 TBCTR。

可触发中断、ADC、TZ 子模块联动保护。

关键寄存器

DCTRIPSEL:选择事件输入源(如 TRIPIN、COMPxOUT)。

TZDCSEL:配置事件级别(高/低电平触发)映射到 TZ 子模块。

DCFCTL、DCFOFFSET、DCFWINDOW:滤波窗口、延迟等设置。

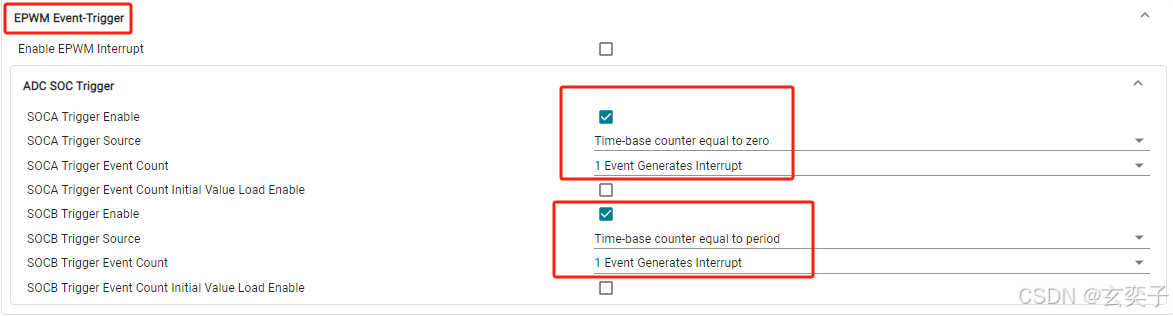

事件触发子模块(ET)

功能总结

用于配置何时触发中断(EPWMxINT)或 ADC 转换(SOCA/B)。

支持 CTR=Zero/PRD/CMPx 等事件为触发源;支持每第 N 次触发。

可结合 Global Load 或 AQ 实现多模块联动。

关键寄存器

ETSEL:选择事件源并使能中断/ADC 启动。

ETPS:事件触发频率分频设置(如每1/2/3次触发)。

ETFLG/ETCLR:事件标志位读取与清除。

CCS配置

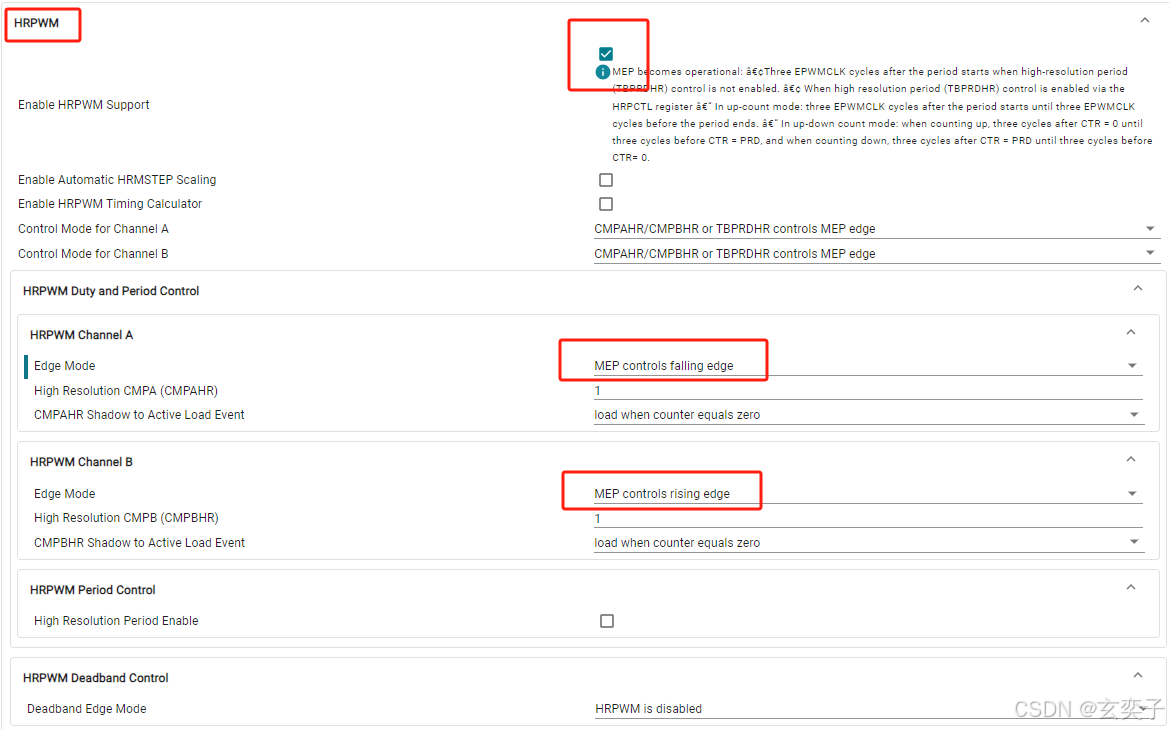

HRPWM

功能总结

通过 MEP 技术将 PWM 分辨率扩展至亚系统时钟(~150ps)。

用于高频 PWM 控制下提升占空比、相位、周期的调节精度。

支持高分辨率设置:占空比(CMPAHR/CMPBHR)、周期(TBPRDHR)、相位(TBPHSHR)、死区(DBREDHR/DBFEDHR)。

适用于多相电源、数字功放、D类变换器、相移全桥等高精度要求场景。

支持自动换算(Auto-conversion)与在线标定(SFO 软件计算 MEP 步长)。

关键寄存器

CMPAHR/CMPBHR:占空比高分辨率扩展寄存器(8 位,配合 CMPA/B 使用)。

TBPRDHR:周期高分辨率扩展寄存器(部分芯片支持)。

TBPHSHR:相位高分辨率扩展寄存器。

DBREDHR/DBFEDHR:死区延迟高分辨率寄存器(仅用于 half-cycle 模式)。

HRCNFG/HRCNFG2:配置边沿选择(上升/下降/双边)、自动换算、加载条件等。

HRPCTL:高分辨率周期使能、相位加载同步控制。

HRMSTEP:MEP 步长(由 SFO 软件写入,影响精度换算)。

CCS配置