1 概念

Shared Logic(共享逻辑) 指的是 Aurora IP 核运行所必需,但又可以被多个 IP 核实例共享的 FPGA 资源。主要包括:

-

收发器公共模块 :如

GTHE2_COMMON,GTXE2_COMMON,GTPE2_COMMON。这些模块为同一个 Quad 内的多个收发器通道提供 QPLL 时钟源和参考时钟路由。 -

时钟缓冲与生成:

-

参考时钟的差分输入缓冲器:

IBUFDS_GTE2/3/4 -

用户时钟生成模块:

MMCM/PLL和BUFG/BUFG_GT

-

-

复位逻辑 :对

reset和gt_reset输入信号进行去抖和同步的逻辑。

这两个选项决定了这些共享资源是被封装在 IP 核内部 ,还是被提取到 IP 核外部的示例设计层次。

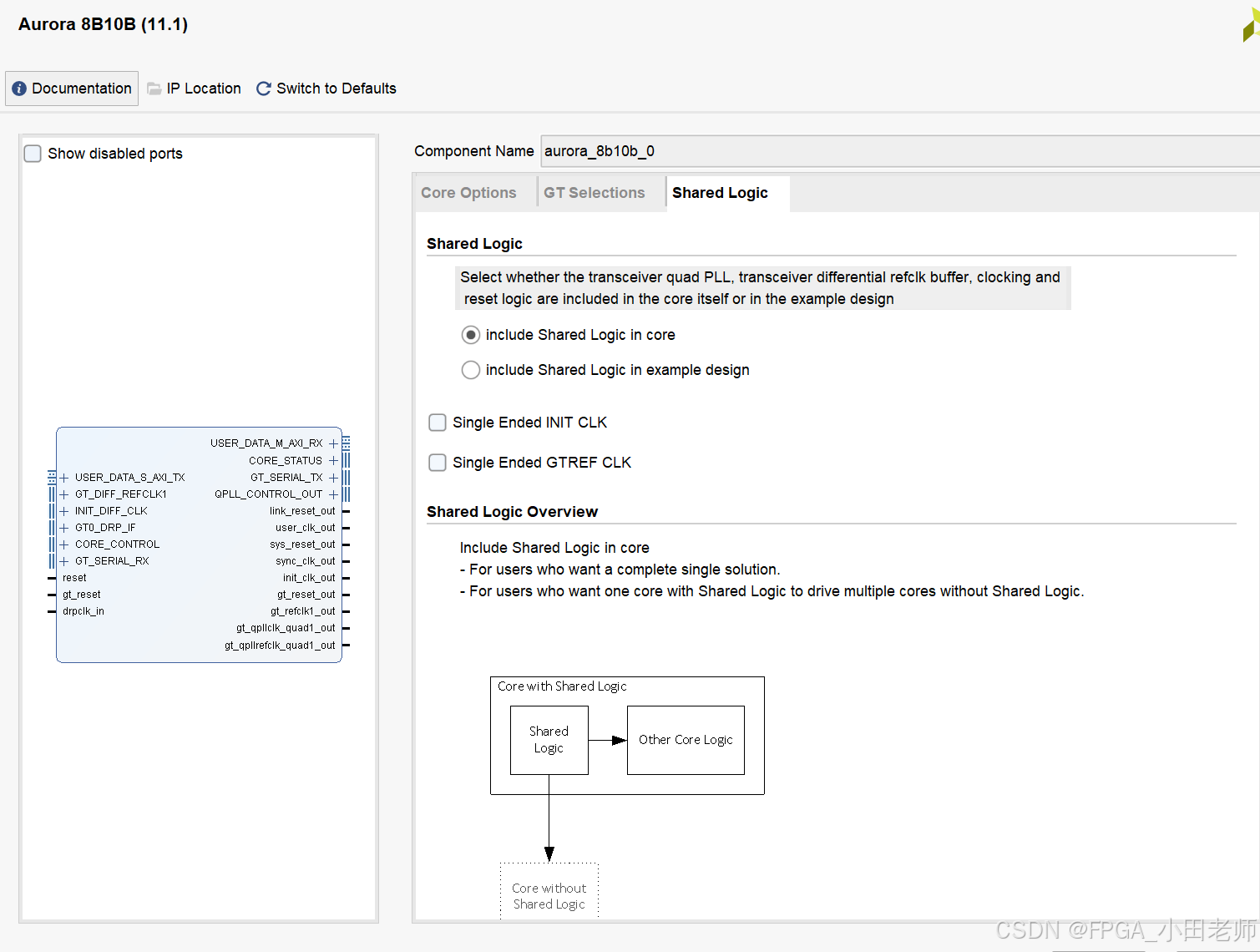

2 选项一:Include Shared Logic in Core(共享逻辑在核心内)

2.1 含义

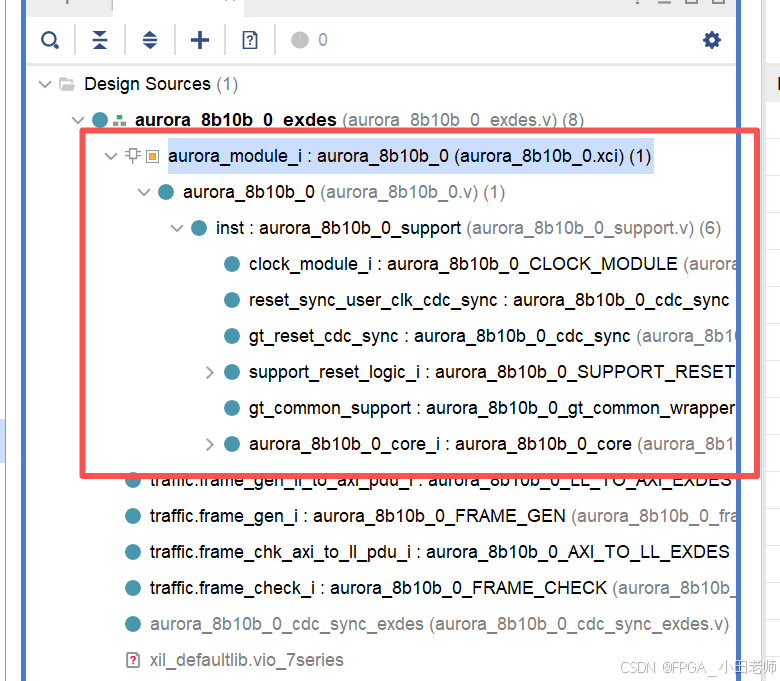

将所有共享逻辑(时钟、复位、公共模块)打包在 IP 核 aurora_8b10b_0 的内部。生成的 IP 核是一个功能完整、自包含的"黑盒子"。

Top-Level Design

└── aurora_8b10b_0 (IP Core)

├── <component_name>_support (Shared Logic)

│ ├── IBUFDS_GTE* (Refclk Buffer)

│ ├── GT*_COMMON (QPLL)

│ ├── Clock Module (MMCM/PLL, BUFG)

│ └── Reset Debouncer

└── <component_name>_core (Aurora Protocol Engine)2.2 端口变化

IP 核的端口会更"干净",主要是用户接口和串行收发端口。

它会输出一些由内部共享逻辑生成的时钟和状态信号,供用户逻辑使用,例如:

-

user_clk_out -

sync_clk_out -

gt_refclk1_out -

sys_reset_out -

gt_reset_out -

quad1_common_lock_out(PLL 锁定状态)

2.3 优点

-

简单易用:开箱即用,无需关心内部时钟和复位生成。对于初学者或快速原型开发非常友好。

-

自成一体:IP 核自身就是完整的,不需要外部依赖。

-

适合单一实例 :当你的设计中只有一个 Aurora IP 核时,这是最直接的选择。

2.4 缺点

-

资源浪费 :如果设计中有多个 Aurora IP 核(尤其是在同一个 Quad 内),每个核都会实例化自己的一套共享逻辑(如

GTHE2_COMMON),这会导致资源冲突和浪费,因为一个 Quad 只能有一个GTHE2_COMMON实例。 -

灵活性差 :难以让多个 IP 核共享同一套时钟和复位资源。

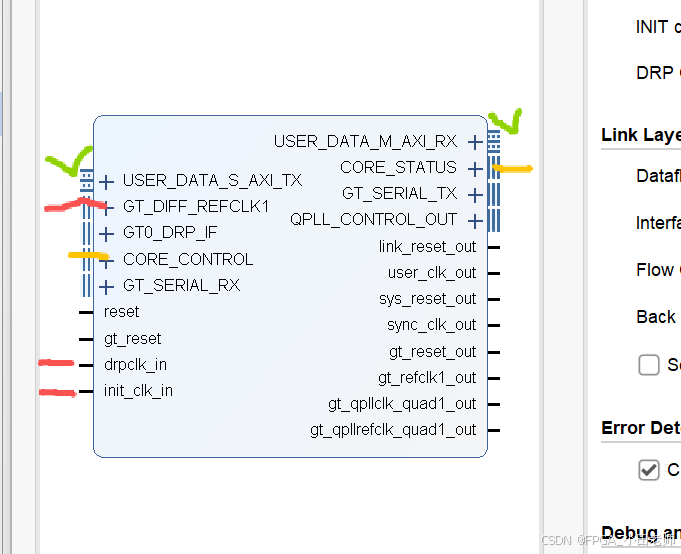

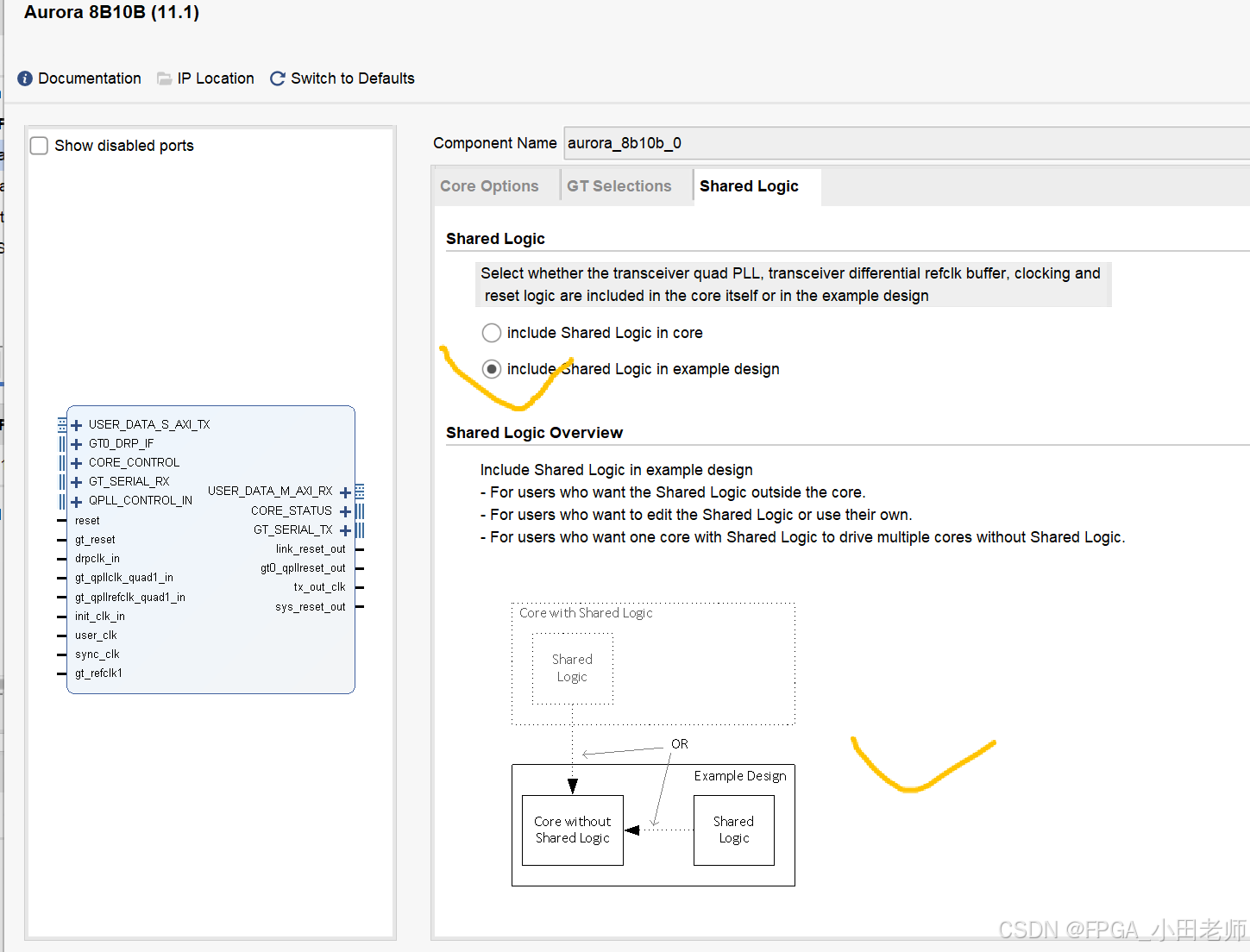

3 选项二:Include Shared Logic in Example Design(共享逻辑在示例设计中)

3.1 含义

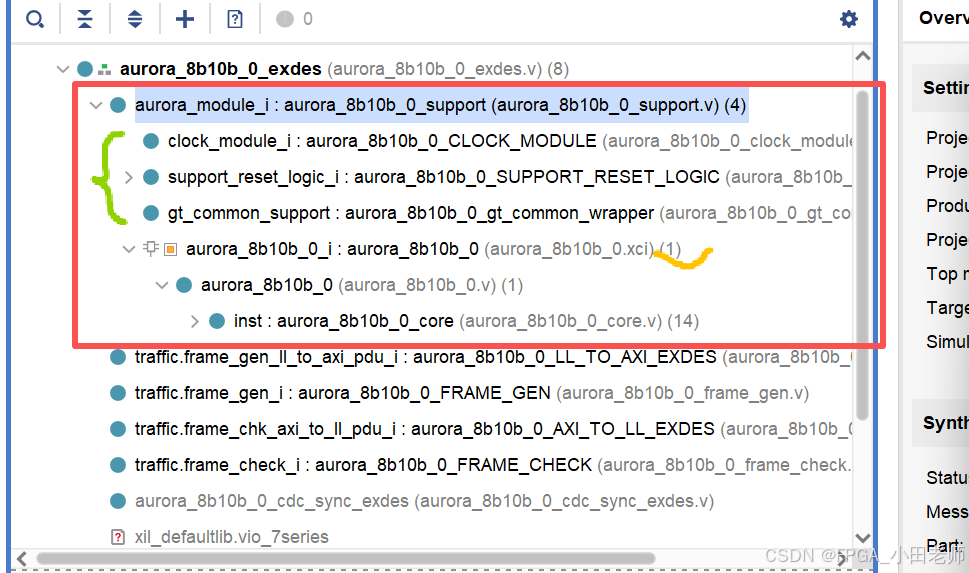

将共享逻辑从 IP 核内部剥离出来 ,放在更高一层的模块中(通常是自动生成的示例设计 aurora_8b10b_0_exdes)。IP 核本身 aurora_8b10b_0 变成一个"纯协议引擎",它需要从外部接收所有必要的时钟和复位信号。

Top-Level Design (e.g., aurora_8b10b_0_exdes)

├── <component_name>_support (Shared Logic - NOW OUTSIDE IP)

│ ├── IBUFDS_GTE* (Refclk Buffer)

│ ├── GT*_COMMON (QPLL)

│ ├── Clock Module (MMCM/PLL, BUFG)

│ └── Reset Debouncer

└── aurora_8b10b_0 (IP Core - "Core" only)

└── <component_name>_core (Aurora Protocol Engine)3.2 端口变化

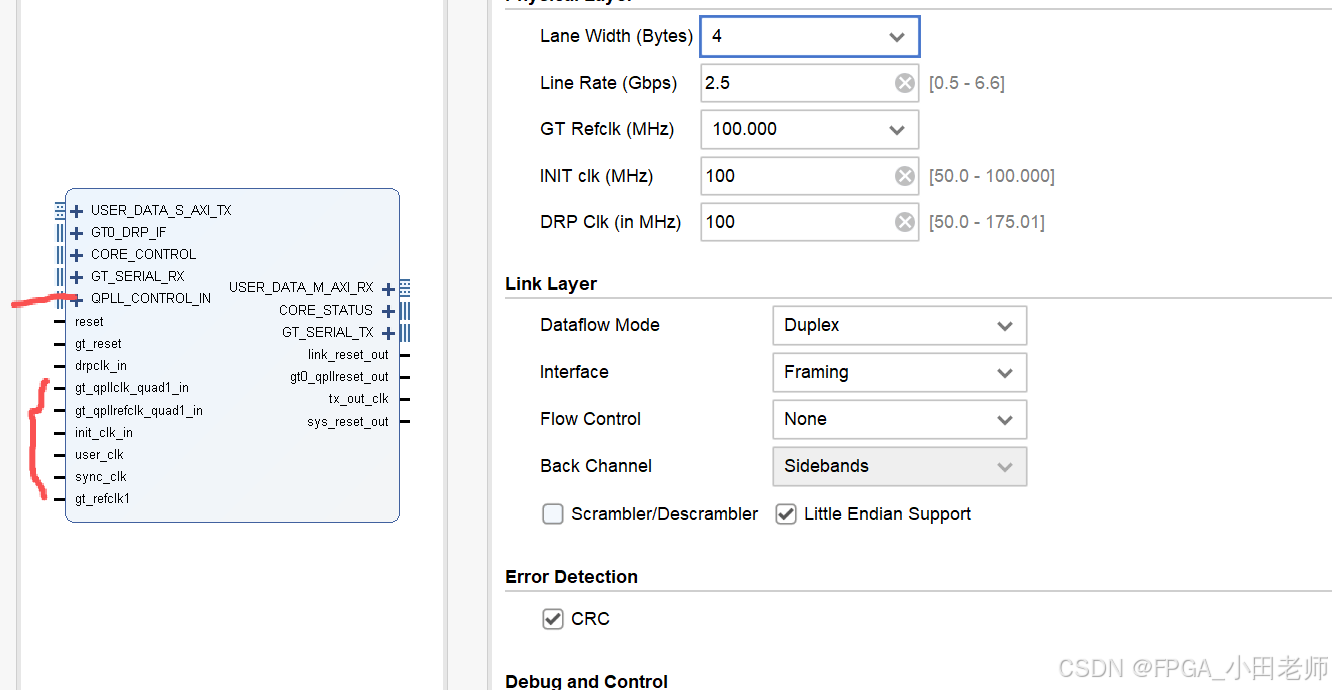

IP 核的端口会变得更"复杂",因为它需要输入所有由外部共享逻辑提供的信号.

-

gt_refclk1_in(而不是自己缓冲) -

gt0_pll0outclk_in(从外部 Common 模块来的时钟) -

init_clk_in(外部提供的初始化时钟) -

user_clk(外部提供,而不是自己输出) -

sync_clk(外部提供) -

gt_reset_in(外部提供去抖后的复位)

3.3 优点

-

资源优化 :这是多实例设计的关键 。一个共享逻辑模块(

*_support)可以驱动多个 Aurora IP 核,共享同一个 QPLL 和时钟网络,极大节省资源。 -

设计灵活:你可以创建自己的顶层模块,精细控制时钟和复位策略,让多个 IP 核协同工作。

-

符合最佳实践 :在复杂的、使用多个高速串行 IP 核的设计中,这是推荐和必需的方法。

3.4 缺点

-

复杂度高:用户需要负责正确连接所有从共享逻辑模块到 IP 核的时钟和控制信号。

-

依赖示例设计 :在开发初期,通常需要基于生成的示例设计进行修改,而不是直接实例化一个孤立的 IP 核。

4 决策指南:如何选择?

| 设计场景 | 推荐选项 | 理由 |

|---|---|---|

| 设计中只有一个 Aurora IP 核 | Include Shared Logic in Core |

简单,直接,避免不必要的连接复杂性。 |

| 快速原型/评估 | Include Shared Logic in Core |

快速生成比特流进行硬件测试,无需理解复杂的时钟连接。 |

| 设计中有多个 Aurora IP 核 | Include Shared Logic in Example Design |

必须选择此项。避免 QPLL 和时钟缓冲器冲突,优化资源使用。 |

| 在 IP Integrator 中使用 | Include Shared Logic in Example Design |

IPI 可以自动管理共享逻辑的连接,当放置多个实例时,工具会自动将其中一个配置为共享逻辑提供者。 |

| 需要自定义时钟/复位策略 | Include Shared Logic in Example Design |

提供更大的灵活性,让你完全控制时钟和复位来源。 |

5 高级技巧与注意事项

-

在 IP Integrator 中的行为 :当使用 IP Integrator 框图设计时,如果你放置了多个 Aurora IP 核,Vivado 会自动处理 共享逻辑。通常,第一个被放置的 IP 核会被设置为

Include Shared Logic in Core,后续的核会被自动设置为Include Shared Logic in Example Design,并且它们的共享逻辑端口会自动连接到第一个核。你可以通过右键点击 IP 核并选择 "Show IP Configuration..." -> "Shared Logic" 选项卡来查看和修改。 -

从旧版本迁移:如果你在升级一个使用旧版本 Aurora IP 的设计,很可能需要从 "in core" 模式迁移到 "in example design" 模式,这通常需要重新构建你的顶层连接。

-

调试 :当选择 "in example design" 时,如果链路无法建立,请务必先检查共享逻辑模块输出的时钟和锁定信号(如

user_clk,quad1_common_lock_out)是否正确,然后再去排查 Aurora 核本身的问题。

总而言之,这是一个在"易用性"和"灵活性与效率"之间的权衡。对于任何严肃的、可能扩展的多通道应用,从开始就选择 Include Shared Logic in Example Design 是更明智和面向未来的选择。