一、不同倍频对URAT串口实际波特率的影响

UART通信的双方需要约定一个相同的波特率,即每秒传输的比特数。在单片机/嵌入式系统中,这个波特率通常是由一个定时器(通常是波特率发生器)对系统时钟进行分频而产生的。

1.分频误差:

在通信和时钟系统中,分频误差(Baud Rate Error,BR Error) 是指由于分频器(Divider)的设置限制,导致实际生成的波特率与目标波特率之间的偏差。这种误差在异步串行通信(如UART)或时钟同步中尤为重要,可能直接影响通信的稳定性。

- MCU URAT串口的实际波特率

波特率由系统时钟分频得到,分频系数必须为整数,例如

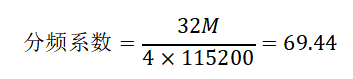

系统时钟频率为FCLK=32M,目标波特率为115200bps,4倍频采样,则分频系数应为

但实际只能取整数,因此取69,则分频波特率为

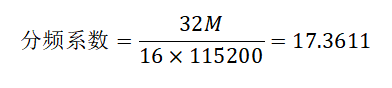

即MCU此时URAT串口实际波特率为115942bps。如果采用16倍采样则

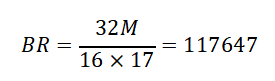

分频系数取17

由此可见由于分频系数只能取整数导致实际波特率偏离目标值且会随着采样倍频变化而变化,可通过以下方法改善此问题

(1)部分MCU支持小数分频器,可设置非整数分频系数。

(2)选用更高频率的主时钟,减少分频系数小数部分的影响。

(3)选择低误差的波特率和倍频数组合。

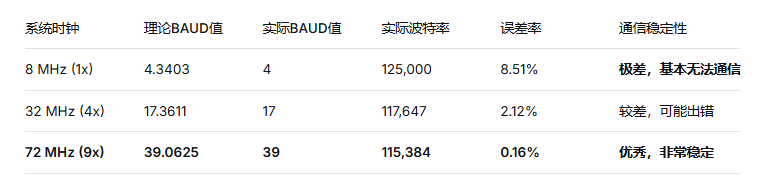

不同主频的影响

二、不同倍频数在采样上的不同

URAT采样的不同倍频数的主要区别是将1bit分成不同份数,如4倍频分为4份,数据位采样点为第3份(停止位采样点为第二份);16倍频分为16份,数据位采样点为第9份(停止位采样点为第8份)。采样点处出现异常波形(如上升下降沿、异常尖刺或占空比异常)则采样会出现异常。由于波特率一定的情况下,1bit时间固定,因此份数越多则采样时间越短相对越靠近中心。以速率115200bps为例分析高电平占空比偏高对采样的影响。

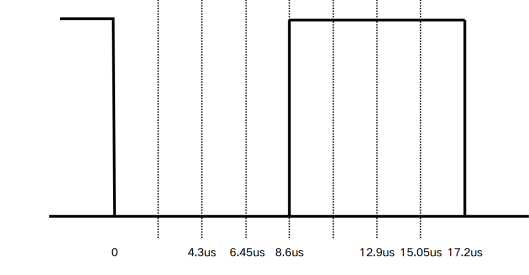

115200bps下1bit时长为8.6us,假设对一低一高波形采样,设开始变低的瞬间为时间零点,理想情况下如下图:

数据位采样点在第三份,则对图中低电平、高电平采样时间分别为横轴中4.3us-6.45us、12.9us-15.05us。

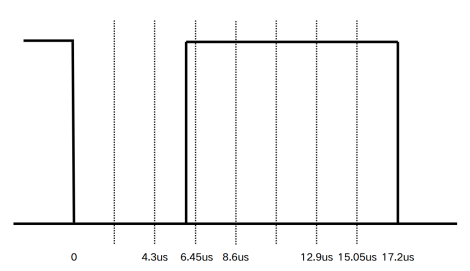

当波形产生异常时,如高电平占空比变高则波形变为如下情况

此时由于低电平的采样点被高电平侵占,使得低电平采样失败。

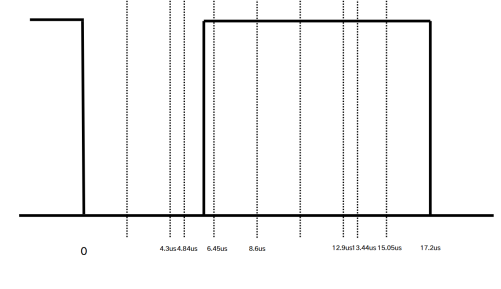

如果将4倍频改为16倍频,而高电平占空比不变的情况下

结论:16倍频下,采样点由4倍频的4份中的第3份变为16份中的第9份,即采样时间变为图中横轴上的4.3us-4.8375us、12.9us-13.4375us,此时高电平不再侵占低电平采样点,可见对高电平占空比变高的容忍度有所提升。