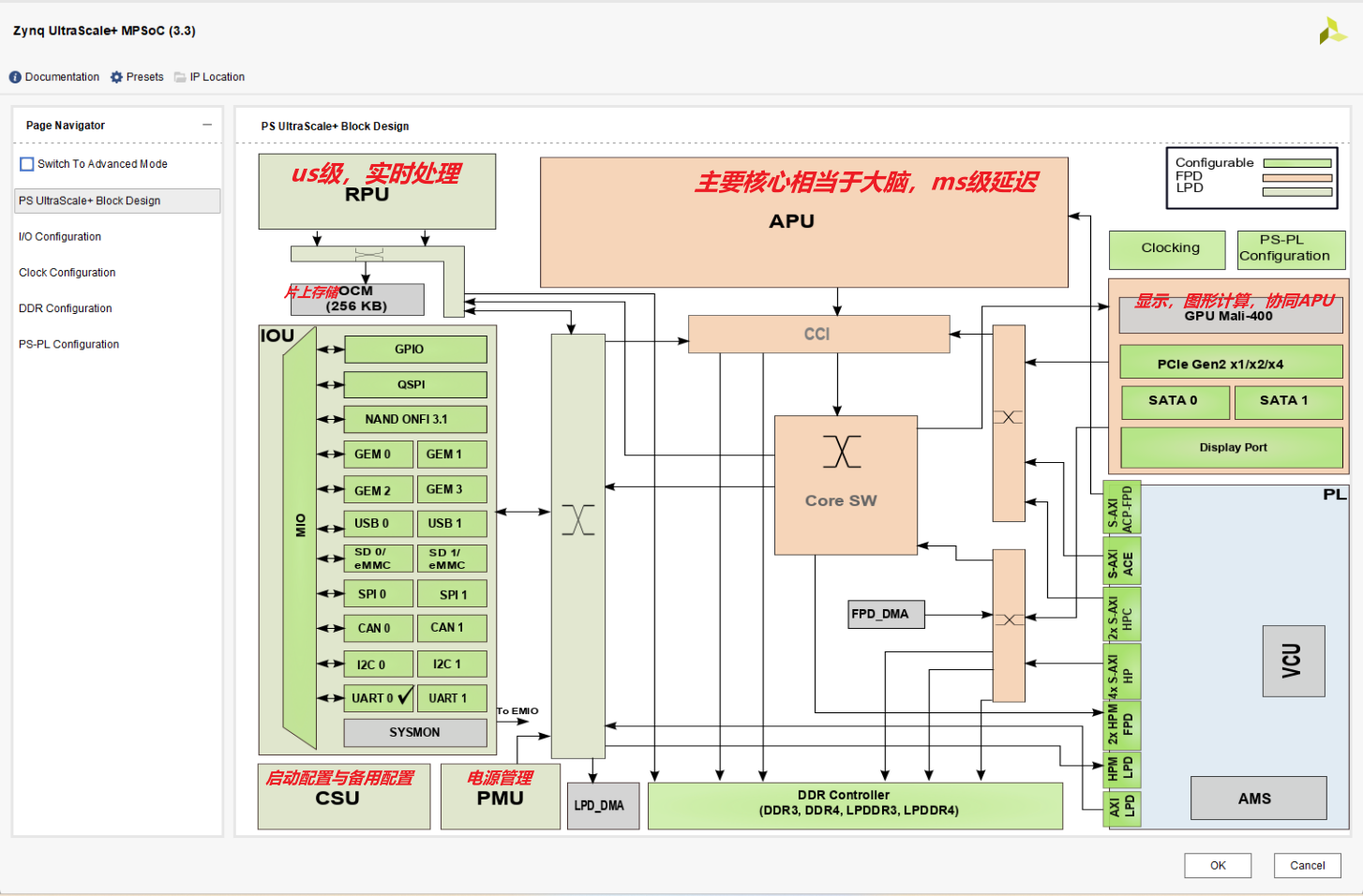

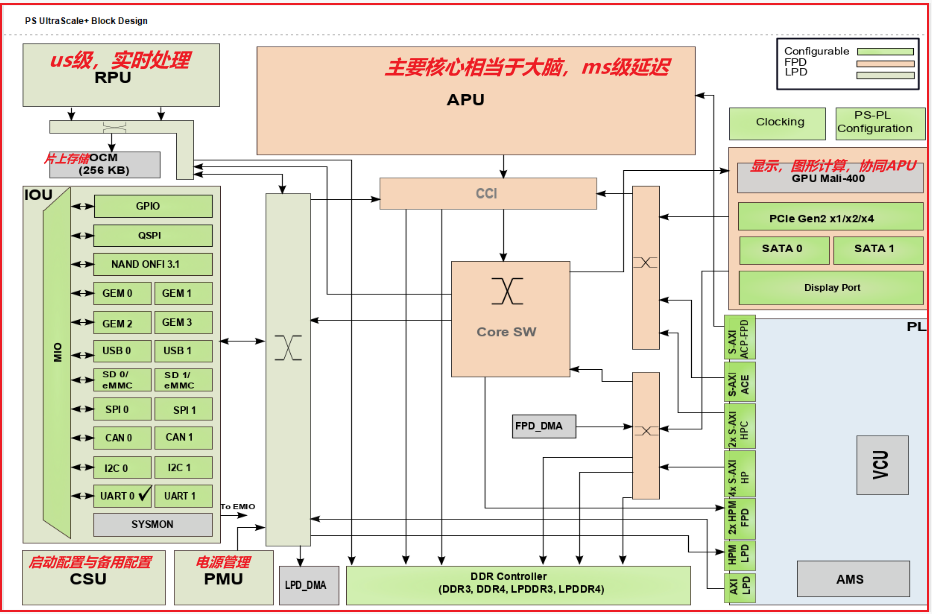

以上为block design中IP核的总览图,下面详细介绍

一. PS端结构总览

一、APU:Application Processing Unit(应用处理器单元)

1. 核心定义

- 全称:应用处理器单元,是 ZYNQ UltraScale+ 的「主计算核心」,面向复杂应用层任务。

- 架构配置 :

- 主流型号(如 XCZU9EG/XCZU19EG)搭载 4 核 ARM Cortex-A53 (32/64 位可配置,主频最高 1.5GHz)或 2 核 Cortex-A72 + 4 核 Cortex-A53 异构组合(高性能型号)。

- 支持对称多处理(SMP),运行 Linux、FreeRTOS 等带 MMU(内存管理单元)的操作系统。

2. 核心功能

- 处理非实时、高复杂度任务:操作系统运行、图形界面(GUI)、网络通信(Ethernet/PCIe)、数据存储(SD/eMMC)、复杂算法预处理(如核数据的批量滤波)。

- 负责 PL 逻辑的控制与配置(通过 AXI 总线与 PL 交互),例如启动时加载 FPGA 比特流、运行中配置 PL 内的 DSP 核参数。

3. 核科学 / DSP 场景应用

- 核探测器数据的 离线分析与存储(如 γ 能谱数据的批量处理、日志记录)。

- 远程控制与监控(通过 Ethernet 接收上位机指令,控制 PL 内的数据采集模块)。

- 复杂算法调度(如将实时性要求低的傅里叶变换预处理任务分配给 APU,实时滤波交给 RPU/PL)。

二、RPU:Real-Time Processing Unit(实时处理单元)

1. 核心定义

- 全称:实时处理单元,是面向「硬实时任务」的专用处理器,强调低延迟、高可靠性。

- 架构配置 :

- 2 核 ARM Cortex-R5F 处理器(锁步 / 非锁步模式可选),主频最高 600MHz。

- 无 MMU(内存管理单元),支持 MPU(内存保护单元),运行 FreeRTOS、VxWorks 等实时操作系统(RTOS)。

- 内置硬件除法器、CRC 加速器,支持单精度浮点运算,硬件层面优化实时 DSP 性能。

2. 核心功能

- 处理毫秒 / 微秒级实时任务:闭环控制、实时数据采集、低延迟信号处理、故障检测与容错。

- 直接与 PL 逻辑通过 AXI-Lite(控制)/AXI-Stream(数据流)总线高速交互,无需经过 APU 中转,降低延迟。

3. 核科学 / DSP 场景应用

- 核探测器的 实时数据预处理(如脉冲幅度分析、基线恢复、峰值检测,延迟要求 < 1μs)。

- 辐射剂量率的实时监控与报警(锁步模式提升可靠性,避免辐射环境下的单粒子翻转错误)。

- PL 内 DSP 核的实时配置(如动态调整 FIR 滤波器系数,适应不同辐射源的信号特性)。

三、PMU:Power Management Unit(电源管理单元)

1. 核心定义

- 全称:电源管理单元,是 ZYNQ UltraScale+ 的「电源中枢」,负责芯片各模块的电压调节、功耗监控和节能控制。

- 硬件组成:内置电压调节器(VR)、电源监控器、功耗计数器、唤醒 / 休眠控制器。

2. 核心功能

- 动态电压频率调节(DVFS):根据 APU/RPU/PL 的负载,自动调整核心电压和主频,平衡性能与功耗。

- 多电源域管理:为 APU、RPU、PL、OCM 等模块分配独立电源域,支持部分模块休眠(如 APU 休眠时 RPU 单独工作)。

- 电源故障检测:实时监控电压、电流,异常时触发复位或中断,避免辐射环境下的电源波动导致系统崩溃。

四、CSU:Configuration and Security Unit(配置与安全单元)

1. 核心定义

- 全称:配置与安全单元,是 ZYNQ UltraScale+ 的「启动与安全核心」,负责 FPGA 逻辑配置、芯片启动流程和安全认证。

- 核心角色:芯片上电后首先启动的模块,主导整个系统的初始化和安全校验。

2. 核心功能

- FPGA 配置管理:加载 PL 逻辑的比特流文件(支持从 SD 卡、QSPI Flash、Ethernet 加载),支持部分重配置(Partial Reconfiguration)。

- 安全启动与加密:

- 比特流加密:对 PL 比特流和 APU/RPU 固件进行 AES-256 加密,防止固件被篡改或窃取。

- 安全认证:支持 RSA/ECC 签名校验,确保加载的固件来自可信来源(避免辐射环境下的恶意注入攻击)。

- 故障恢复:PL 配置失败时,自动触发重新配置或切换到备用比特流。

3. 核科学场景应用

- 核安全级设备的 固件防篡改(如核电站辐射监测系统,避免恶意修改 PL 逻辑导致数据失真)。

- 辐射环境下的 PL 配置容错(部分重配置功能可快速修复单粒子翻转导致的 PL 逻辑错误)。

五、GPU:Graphics Processing Unit(图形处理单元)

1. 核心定义

- 全称:图形处理单元,是 ZYNQ UltraScale+ 的「并行计算与图形渲染核心」,基于 Xilinx 自研的 GPU 架构(而非 ARM Mali)。

- 架构配置:支持 OpenGL ES 3.1、OpenCL 1.2,具备 2D/3D 图形渲染引擎和并行计算单元(可用于通用计算)。

2. 核心功能

- 图形渲染:用于嵌入式 GUI 显示(如核仪器的触摸屏界面、辐射分布热力图显示)。

- 并行计算:通过 OpenCL 编程,将 GPU 作为并行处理器,加速矩阵运算、图像滤波、批量数据处理等任务。

- 与 APU/PL 协同:支持 OpenCL 内核在 GPU/PL 之间迁移,灵活分配计算资源。

3. 核科学 / DSP 场景应用

- 核图像的 并行处理(如 γ 相机的图像重建、辐射场分布可视化,GPU 并行计算提升处理速度 10 倍以上)。

- 大规模核数据的统计分析(如中子通量数据的直方图生成,利用 GPU 多线程并行计算)。

六、OCM:On-Chip Memory(片上存储器)

1. 核心定义

- 全称:片上存储器,是 ZYNQ UltraScale+ 内置的高速 RAM,用于处理器核心和 PL 逻辑的低延迟数据存储。

- 架构配置 :

- 容量:通常为 256KB ~ 1MB(分多个 bank,支持单端口 / 双端口访问)。

- 访问速度:主频与 RPU/APU 同步(最高 600MHz),延迟 < 1ns(远低于外部 DDR4 的 10ns+ 延迟)。

- 总线接口:支持 APU/RPU/PL 同时访问,通过 AXI 总线实现共享存储。

2. 核心功能

- 处理器缓存:作为 APU/RPU 的 L2 缓存扩展,存储频繁访问的指令和数据,减少对外部 DDR 的依赖。

- 高速数据流缓冲:PL 与 RPU 之间的实时数据流暂存(如核探测器的脉冲信号数据,通过 AXI-Stream 写入 OCM,RPU 直接读取处理)。

- 共享内存:APU、RPU、PL 之间的低延迟数据交换(如 RPU 处理后的实时数据写入 OCM,APU 读取后存储到 DDR)。

3. 核科学 / DSP 场景应用

- 实时 DSP 算法的 数据缓冲(如 FIR 滤波器的输入 / 输出数据暂存,避免 DDR 访问延迟导致的信号失真)。

- 核脉冲信号的峰值缓存(将检测到的峰值数据快速写入 OCM,RPU 实时计算幅度和能量,延迟 < 500ns)。

- 故障诊断数据的临时存储(辐射环境下 DDR 出错时,OCM 可作为应急缓存,避免关键数据丢失)。

七、各模块协同工作流程

以「核探测器实时数据采集与分析系统」为例,各模块的协同逻辑如下:

- 上电启动:CSU 首先启动,校验并加载加密的 PL 比特流(含 DSP 采集逻辑)和 RPU 固件,确保系统安全可信。

- 电源配置:PMU 为 APU(低功耗模式)、RPU(满主频 600MHz)、PL(DSP 核电压 1.0V)分配电源,启动 DVFS 监控。

- 实时采集与处理 :

- PL 内 DSP 核采集核探测器的脉冲信号,通过 AXI-Stream 写入 OCM(高速缓冲)。

- RPU 从 OCM 读取数据,执行实时峰值检测和能量计算(延迟 < 1μs),结果写入 OCM 共享区域。

- 数据存储与分析 :

- APU 从 OCM 读取 RPU 处理后的结果,批量存储到 eMMC,并通过 Ethernet 上传到上位机。

- 若需要可视化,GPU 从 DDR 读取数据,生成辐射剂量热力图,显示在触摸屏上。

- 容错与安全 :

- CSU 实时监控 PL 逻辑,若检测到单粒子翻转,触发部分重配置修复错误。

- PMU 监控电源电压,若辐射导致电压波动,自动调整 RPU/PL 电压,避免系统崩溃。

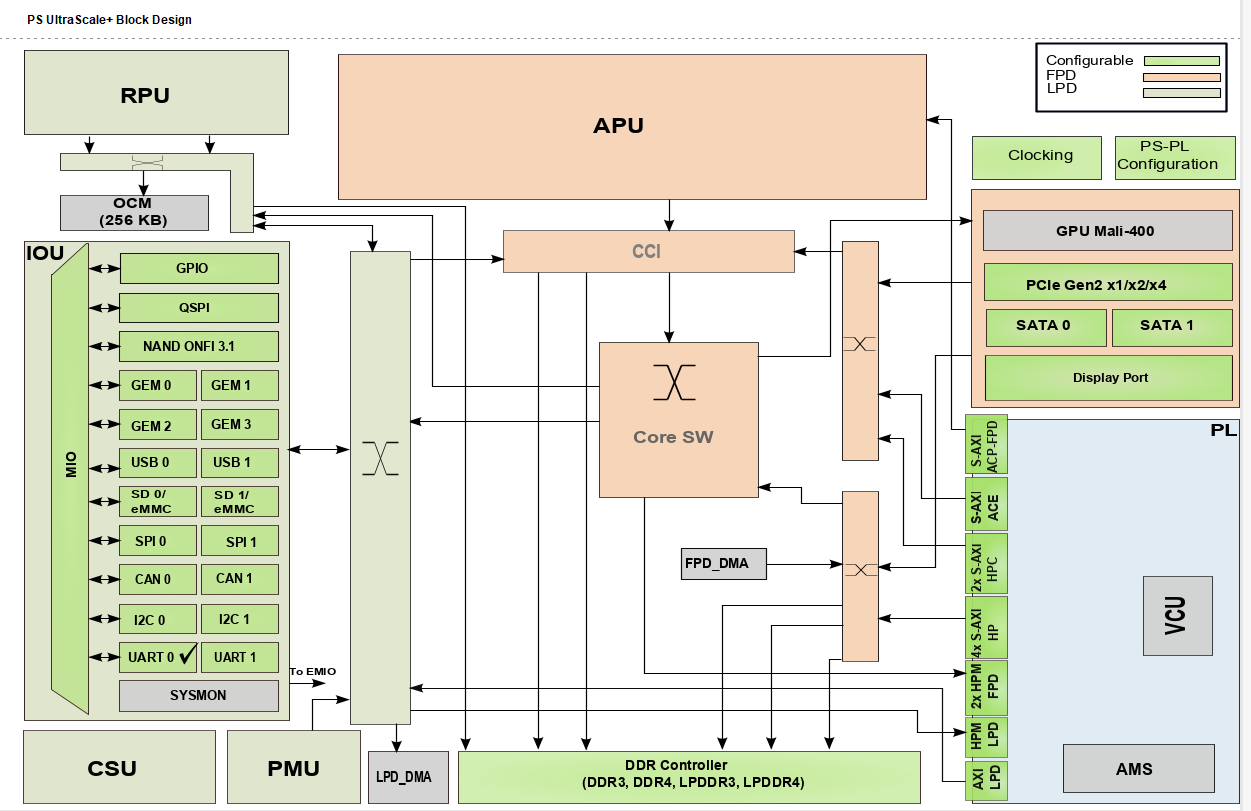

二. IP核配置

PS UltraScale+ ™ 模块设计页面中的颜色具有以下含义:

- 浅绿色显示低功耗域

- 浅橙色显示全功率域

- 深绿色显示可以配置的组件。

I/O 配置中主要针对PS元件接口的各个信号的引脚分配。包括

- Low Speed

接口部分分为低速,高速和参考时钟

先由低速开始。低速接口支持 QSPI,NAND 和 SD。

在硬件设计上 PS 端连接了 1 片 8GB eMMC FLASH 存储芯片,1 片 256Mb 的 QSPI FLASH 用来静态存储 MPSoCs 的操作系统、文件系统及用户数据,1 片 32GB MicroSD 用于存储操作系统镜像和文件系统。

- High speed

高速接口支持 GEM (Gigabit Ethernet Module)(in SGMII mode),USB,PCIe,DP 和 SATA

在硬件设计上 PS 端连接了1个GEM ,1个USB3.0 和 PCIe3.0x2

- Reference clocks

选择 PLL 时钟单元的时钟源,具体可以在System PLL Units 时钟配置中查看

- 视频参考时钟:PSU VIDEO REF CLK(设备引脚,正常源)

- 备用 PS 参考时钟 :PSS ALT REF CLK(两个 MIO 引脚之一)

在 ZYNQ UltraScale+ 中,GPIO(General Purpose I/O)是通用输入输出接口的总称,用于芯片与外部外设(如传感器、按键、LED、探测器)进行数字信号(高低电平)交互 ;而 MIO(Multi-IO)和 EMIO(Extended MIO)是 GPIO 的两种具体实现形式 ,核心区别在于「引脚归属(PS/PL)」「是否占用物理引脚」和「扩展能力」,尤其适配 FPGA 开发中「PS 软件控制」与「PL 硬件协同」的灵活需求。

一、MIO:Multi-IO(PS 侧专用 GPIO)

1. 核心定义

- 归属 :属于 ZYNQ 的 PS(Processing System,即 APU/RPU 所在的处理系统)模块,是 PS 自带的「专用物理 GPIO 引脚」。

- 硬件特点 :

- 引脚数量:不同型号 ZYNQ UltraScale+ 差异不大,通常为 54 个 MIO 引脚(分多个 bank,如 Bank 0~5)。

- 直接连接 PS 内部的 GPIO 控制器,无需经过 PL 逻辑,延迟极低(ns 级),且不占用 PL 的可编程资源(LUT/FF)和引脚。

- 功能复用:每个 MIO 引脚可配置为 GPIO 或专用外设接口(如 UART、SPI、I2C、SDIO、CAN),通过 Vivado 的 PS 配置工具(PS-PL Configuration)选择功能。

2. 核心功能

- 由 PS 的 APU/RPU 直接通过软件(如 Linux 驱动、FreeRTOS 代码)控制,实现:

- 输出控制:高低电平输出(如控制外部设备的电源使能、复位信号)。

- 输入检测:读取外部设备的状态信号(如按键按下、探测器就绪信号)。

- 中断触发:支持上升沿 / 下降沿 / 双边沿中断(如探测器的异常信号触发 PS 中断处理)。

3. 核科学 / FPGA 开发场景应用

- 简单外设控制 :

- 控制核探测器的电源使能(MIO 输出高电平启动探测器,低电平关闭)。

- 读取探测器的状态反馈(如 MIO 输入引脚检测探测器是否完成校准)。

- 板载 LED 指示灯(如辐射剂量超标时 MIO 输出高电平点亮报警灯)。

- 专用外设复用 :

- 将 MIO 配置为 UART 接口,与核仪器的串口模块通信(传输控制指令)。

- 将 MIO 配置为 SDIO 接口,控制 SD 卡存储核数据(无需占用 PL 资源)。

4. 配置要点

- 打开 Vivado 工程,进入「Block Design」,双击 PS 模块(ZYNQ UltraScale+ MPSoC)。

- 在「MIO Configuration」标签页,选择需要的引脚功能(如 GPIO、UART、SPI)。

- 若配置为 GPIO,需在「GPIO Configuration」中启用对应 bank 的 GPIO 控制器(如 Bank 0~1 对应 GPIO 0~31)。

- 生成比特流后,通过软件代码(如 C 语言)控制 GPIO 方向、电平、中断(依赖 Xilinx 提供的

xgpiops驱动库)。

二、EMIO:Extended MIO(PL 侧扩展 GPIO)

1. 核心定义

- 归属:属于 ZYNQ 的 PL(Programmable Logic,FPGA 可编程逻辑)模块,是 MIO 的「扩展接口」,本质是通过 PL 引脚实现的 GPIO 扩展。

- 硬件特点 :

- 引脚数量**:无固定上限,取决于 PL 的可用引脚数量(ZYNQ UltraScale+ 芯片的 PL 引脚通常有数百个,扣除高速接口、电源引脚后,可灵活分配 EMIO)。**

- 连接方式:EMIO 信号先从 PS 的 GPIO 控制器引出,通过 AXI 总线连接到 PL 逻辑,再由 PL 的物理引脚与外部设备交互。

- 资源占用:需要占用 PL 的少量逻辑资源(用于信号缓冲和引脚映射),但不占用 PS 的 MIO 引脚。

- 双向控制:既可由 PS 的 APU/RPU 通过软件控制(与 MIO 操作方式一致),也可由 PL 内的硬件逻辑(如 Verilog 代码)直接控制(适合与 PL 内的 DSP 核、采集模块协同)。

2. 核心功能

- 补充 MIO 引脚不足的场景(如需要控制数十个外部传感器、探测器阵列)。

- 实现 PS 与 PL 、外部设备的三方协同(如 PL 内的 DSP 核采集数据后,通过 EMIO 触发 PS 处理,或 PS 通过 EMIO 配置 PL 逻辑)。

- 支持与 PL 内的高速接口(如 AXI-Stream)联动(如 EMIO 作为数据采集的同步触发信号,与 PL 内的 ADC 采集逻辑协同)。

3. 核科学 / FPGA 开发场景应用

- 多探测器阵列控制 :

- 核辐射探测阵列(如 16 路 γ 探测器)的触发信号控制(每路探测器对应 1 个 EMIO 输出引脚,由 PS 或 PL 控制启动采集)。

- 多路探测器的状态反馈读取(EMIO 输入引脚读取每路探测器的校准状态、数据就绪信号)。

- PL 逻辑与外部设备的协同 :

- PL 内的 DSP 核处理核脉冲信号时,通过 EMIO 输出同步信号(如峰值检测完成信号),触发外部存储模块存储数据。

- 外部设备(如高速 ADC)的配置信号(如采样率切换)由 PL 逻辑通过 EMIO 控制,无需 PS 介入,降低延迟。

- 高可靠性场景 :

- 核安全级设备中,用 EMIO 实现冗余控制(如 PS 控制 1 路 EMIO,PL 控制另一路 EMIO,双重保障探测器的电源使能)。

4. 配置要点

- 打开 PS 模块配置界面,在「GPIO Configuration」标签页,启用「EMIO GPIO」,并设置 EMIO 的通道数(如 32 路、64 路)。

- 在 Block Design 中,PS 模块会自动生成 EMIO 信号接口(如

GPIO_0_0~GPIO_0_31),需要将这些信号与 PL 的物理引脚绑定(通过「Package Pin」约束)。 - 若需 PL 逻辑控制 EMIO,可在 Verilog 代码中直接例化 EMIO 对应的信号(如

input wire emio_detector_trig;),与 PL 内的 DSP 核、状态机联动。 - 软件控制 EMIO 与 MIO 完全一致(通过

xgpiops驱动库),仅引脚编号不同(EMIO 引脚编号从 MIO 最大编号后开始,如 MIO 最大 53,则 EMIO 从 54 开始)。

三、BANK

可以把 BANK 理解为 ZYNQ 芯片的「引脚分区」------ 每个分区(BANK)有三个核心共性:

- 统一电源域:同一 BANK 内的所有引脚共享同一个电源(如 VCCIO_BANK0、VCCIO_BANK1),支持的电平标准(如 3.3V、2.5V、1.8V)由该电源决定(用户需通过硬件设计为每个 BANK 提供对应电压);

- 功能特性一致:同一 BANK 内的引脚支持相同的专用外设复用类型(如部分 BANK 支持 UART/SPI,部分支持 SDIO/CAN)、驱动能力(如 4mA/8mA/12mA);

- 软件配置独立:每个 BANK 对应独立的配置寄存器(如 GPIO 控制器按 BANK 启用、中断控制器按 BANK 分配中断通道),软件可单独配置某一 BANK 的功能,不影响其他 BANK。

简单说:BANK 是 Xilinx 为了方便用户「电源设计、外设适配、软件配置」而做的硬件模块化划分,用户无法新增 / 删除 / 合并 BANK,但可以灵活利用每个 BANK 的特性适配外部设备。

一、ZYNQ UltraScale+ 中 BANK 的具体划分(以 MIO/EMIO 为例)

BANK 主要针对「有物理引脚的 IO 模块」(MIO、PL 引脚),核心分为两类:MIO BANK(PS 侧) 和 EMIO 关联的 PL BANK(PL 侧),两者的划分逻辑完全由硬件固定:

1. MIO BANK(PS 侧的核心 BANK 类型)

MIO 作为 PS 侧的专用物理引脚,其 BANK 划分是 ZYNQ 最常用的场景,以主流型号(如 XCZU9EG)为例:

- 数量与引脚范围:共 6 个 BANK(BANK 0~5),对应 54 个 MIO 引脚(每个 BANK 含 8~10 个引脚,具体数量因型号略有差异);

- 电源域与电平 :每个 BANK 对应一个独立的 VCCIO 电源(如 BANK0 对应 VCCIO_BANK0),支持的电平标准由电源电压决定:

- 高电平 BANK(如 BANK0、BANK1):支持 3.3V/2.5V(适合连接按键、LED、探测器电源使能引脚等普通外设);

- 低电平 BANK(如 BANK4、BANK5):支持 1.8V/1.2V(适合连接高速外设,如 SD 卡、SPI 闪存、ADC 配置接口等);

- 功能复用限制 :同一 BANK 内的引脚只能复用同一类专用外设,例如:

- BANK0~1 的引脚可复用为 UART、SPI、I2C;

- BANK2~3 的引脚可复用为 CAN、GPIO;

- BANK4~5 的引脚可复用为 SDIO、GPIO。

四、QSPI

在 ZYNQ UltraScale+ 中,QSPI(Quad SPI)和 NAND 都是非易失性存储接口 ,用于存储系统固件、FPGA 比特流、核数据日志等关键信息(断电后数据不丢失)。两者核心差异在于「接口类型、容量、速度、可靠性、适用场景」,尤其在核科学场景中,需根据「启动速度、数据容量、抗辐射性」选择 ------QSPI 侧重「高速启动、小容量固件存储」 ,NAND 侧重「大容量数据存储、低成本」。

QSPI 支持单片和双片 FLASH,需要注意如果需要使用 QSPI 的情况下,低地址的 SPI 接口(QSPI_0)是必选的,不能单独使用 QSPI_1 接口。

- 硬件关联 :

- 接口归属:属于 PS 侧外设,通过 MIO 引脚与外部 QSPI 闪存(如 SPI NOR Flash)连接(MIO 需配置为 QSPI 功能,通常占用 BANK0~1 的特定引脚,支持 3.3V 电平)。

- 控制模块:由 ZYNQ 的 CSU(配置与安全单元)和 APU 共同控制------ 上电时,CSU 优先从 QSPI 读取加密的 FPGA 比特流和 APU/RPU 固件(支持安全启动);运行时,APU 可通过 QSPI 接口读写数据(如日志更新)。

- 关键特性:支持「XIP(Execute In Place,片上执行)」,固件无需加载到 DDR/OCM 即可直接运行,启动速度极快(毫秒级)。

五、NAND

- 全称:NAND Flash 接口,是并行 / 串行混合的存储接口,核心用于连接 NAND Flash 芯片(如并行 NAND、eMMC 本质是集成控制器的 NAND)。

- 硬件关联 :

- 接口归属:属于 PS 侧外设,通过 MIO 引脚与外部 NAND 芯片连接(MIO 需配置为 NAND 功能,通常占用 BANK2~3 的特定引脚,支持 3.3V/1.8V 电平)。

- 控制模块:主要由 APU 控制(通过 NAND 控制器驱动),用于大容量数据存储,不参与 CSU 启动流程(ZYNQ 上电无法直接从 NAND 加载固件,需先从 QSPI/SD 启动后,再读取 NAND 数据)。

- 关键特性:容量大(GB 级)、成本低,但存在「坏块」问题(需软件层面做坏块管理和 ECC 纠错),读取速度低于 QSPI(串行 NAND 略快,并行 NAND 速度中等)

六、SD卡

SD 卡接口(基于 SDIO 协议)是通用、灵活的非易失性存储方案,核心优势是「可插拔、中等容量、支持热插拔、配置简单」

本质:SDIO 协议的通用存储接口

SD 卡接口在 ZYNQ 中属于 PS 侧外设,基于 SDIO(Secure Digital Input/Output)协议,支持标准 SD 卡(SDHC/SDXC)、microSD 卡,核心硬件特性:

- 引脚与 MIO/BANK 关联 :

- 占用 PS 的 MIO 引脚(固定为 MIO_40~MIO_45,对应 SD_CLK、SD_CMD、SD_D0~D3),属于 BANK4 或 BANK5(低电平 BANK,支持 3.3V/1.8V 电平,实际需与 SD 卡电平匹配,常用 3.3V);

- 引脚数量少(6 个核心引脚),无需占用 PL 资源,硬件设计简单(仅需串联 47kΩ 上拉电阻,适配 SD 卡电平标准)。

- 控制模块 :

- 由 ZYNQ 的 SDIO 控制器 驱动,支持 CSU 启动(作为备用启动设备)和 APU 运行时读写;

- 支持 SDHC(最大 32GB)、SDXC(最大 2TB),传输速度可达 50MB/s(UHS-I 模式),满足中等容量数据的读写需求。

- 与 QSPI/NAND 的核心差异:SD 卡是「外部可插拔存储」,数据可直接脱离设备导出;而 QSPI/NAND 是「板载固定存储」,数据需通过 Ethernet 等方式传输,灵活性远低于 SD 卡。

SD 卡与 QSPI/NAND 的协同工作流程

以「便携式辐射检测仪」为例,三者协同逻辑如下:

- 上电启动:CSU 优先从 QSPI 读取加密比特流和固件,启动 APU/RPU/PL;

- 数据采集:PL 内 DSP 核采集辐射信号,RPU 实时处理后,将原始数据传给 APU;

- 数据存储 :APU 同时将数据写入两处:

- SD 卡:以文件形式存储(便于现场导出);

- NAND:长期备份(避免 SD 卡丢失导致数据丢失);

- 现场操作 :

- 导出数据:用户拔出 SD 卡,插入电脑读取能谱文件;

- 固件升级:用户插入存新固件的 SD 卡,APU 读取文件并更新 QSPI 中的旧固件;

- 故障应急:若 QSPI 损坏,CSU 自动从 SD 卡启动,确保设备可正常工作。

七、SWDT

PS 中有三个系统看门狗定时器 (SWDT) 单元。它们都基于 Arm 系统看门狗定时器架构。

- LPD_SWDT:使用 SWDT 寄存器集,有时称为 swdt0。

- FPD_SWDT:使用 WDT 寄存器集,有时称为 SWDT1。

- CSU_SWDT:使用CSU_WDT寄存器集。

通常需要配合 PMU 固件使用,用于检测系统故障并从中恢复。看门狗定时器可用于防止系统锁定;例如,当软件陷入死锁时。在正常操作中,在处理器上运行的中断处理程序在计时器倒计时到零之前定期重新启动监视程序计时器。如果定时器确实达到零并且看门狗被启用,则会产生以下信号的一个或组合:系统复位、中断或外部信号。看门狗超时周期和任何输出信号的持续时间都是可编程的。

八、Triple Timer Counter (TTC)

四个三重计时器计数器 (TTC) 单元位于 LPD 区域,每个单元有三个类似的计数器。TTC 可以生成周期性中断 ,也可用于 MIO 引脚或 PL 生成波形输出 (例如 PWM)或者时钟分频。所有三个计数器必须具有相同的安全状态,因为它们共享一条 APB 总线。

九、GEM**、USB、PCIe、DisplayPort、SATA**

都是面向不同场景的高速外设接口

一、GEM:Gigabit Ethernet MAC(千兆以太网接口)

- 本质:PS 侧集成的千兆以太网媒体访问控制器(MAC),支持 10/100/1000Mbps 以太网传输,基于 IEEE 802.3 协议。

- 硬件配置 :

- 归属:PS 侧外设,部分高端型号(如 XCZU19EG)支持 2 个 GEM 控制器(GEM0/GEM1)。

- 引脚:占用 MIO 引脚(如 GEM0 对应 MIO_16~MIO_23,含 TXD/RXD/CLK/MDIO 等),属于 BANK0~1(3.3V 电平),无需占用 PL 资源。

- 关键特性:支持 TCP/IP、UDP、IPv4/IPv6,集成硬件校验(CRC)、DMA 传输,可通过 LWIP 协议栈实现高速数据传输(最大 1Gbps,实际核场景可达 800Mbps+)。

Vivado 硬件配置

- 打开 Block Design,双击 PS 模块,进入「MIO Configuration」标签页,将 GEM0 对应的 MIO 引脚(如 MIO_16=TXD0、MIO_17=RXD0、MIO_18=CLK、MIO_19=MDIO)配置为「GEM」功能。

- 切换到「Peripheral Configuration」标签页,启用 GEM0,配置:

- 速率:1000Mbps(千兆模式);

- 启用 DMA(减少 CPU 占用);

- 启用 MDIO(用于自动协商速率)。

- 添加「AXI Ethernet Lite」IP 核(可选,用于 PL 侧数据直接通过 GEM 传输),通过 AXI 总线与 PS 连接。

二、USB:Universal Serial Bus(通用串行总线)

- 本质:PS 侧集成的 USB 控制器,支持 USB 2.0(High-Speed 480Mbps)或 USB 3.0(SuperSpeed 5Gbps,高端型号支持),兼容 USB 外设(U 盘、鼠标、串口适配器)。

Vivado 硬件配置

- 打开 PS 模块配置,进入「MIO Configuration」标签页,将 USB0_DP(MIO_28)、USB0_DM(MIO_29)配置为「USB」功能。

- 切换到「Peripheral Configuration」标签页,启用「USB 2.0 Controller」,选择「Host Mode」。

- 硬件设计需添加 USB 电源管理电路(如 5V 供电、ESD 保护),避免插拔时电压波动。

三、PCIe:PCI Express(高速串行总线)

- 本质:高速串行互联总线,用于 ZYNQ 与外部高速设备(如 FPGA 加速卡、高速 ADC/DAC、SSD)的低延迟、高带宽通信,支持 PCIe Gen1/Gen2/Gen3(速率 2.5/5/8Gbps)。

- 硬件配置 :

- 归属:PS 侧或 PL 侧均可实现(PS 侧集成 PCIe 控制器,PL 侧需例化 Xilinx PCIe IP 核)。

- 引脚:PL 侧 PCIe 需占用专用高速差分引脚(如 PCIe_TX0±/RX0±),支持 x1/x2/x4 链路宽度。

- 关键特性:带宽高(x4 Gen3 可达 32Gbps)、延迟低(ns 级),支持 DMA 传输,适合海量核数据的高速交互。

四、DisplayPort(显示接口)

- 本质:高速数字显示接口,用于核数据的可视化输出(如辐射剂量热力图、γ 能谱曲线),支持高分辨率(4K@60Hz)、高刷新率,基于 DisplayPort 1.2/1.4 协议。

- 硬件配置 :

- 归属:PL 侧实现(需例化 Xilinx DisplayPort TX IP 核),PS 侧通过 AXI 总线传输图像数据。

- 引脚:占用 PL 高速差分引脚(如 DP_TX0±/CLK±),支持单链路 / 双链路传输。

- 关键特性:支持 RGB 格式、HDMI 兼容(通过转接器),核场景主要用于本地可视化监控。

五、SATA:Serial ATA(串行 ATA 接口)

- 本质:高速串行存储接口,用于连接 SATA 硬盘(HDD)或 SATA SSD,实现大容量、高速数据存储,支持 SATA II(3Gbps)/SATA III(6Gbps)。

- 硬件配置 :

- 归属:PS 侧集成 SATA 控制器(部分高端型号支持),或 PL 侧例化 SATA IP 核。

- 引脚:占用 MIO 引脚(如 SATA_TX±/RX±/CLK),属于 BANK5(1.8V 电平),需添加 SATA 电源管理电路。

- 关键特性:容量大(HDD 可达 10TB)、速度快(SATA III 读取速度可达 500MB/s),支持热插拔(部分型号)。

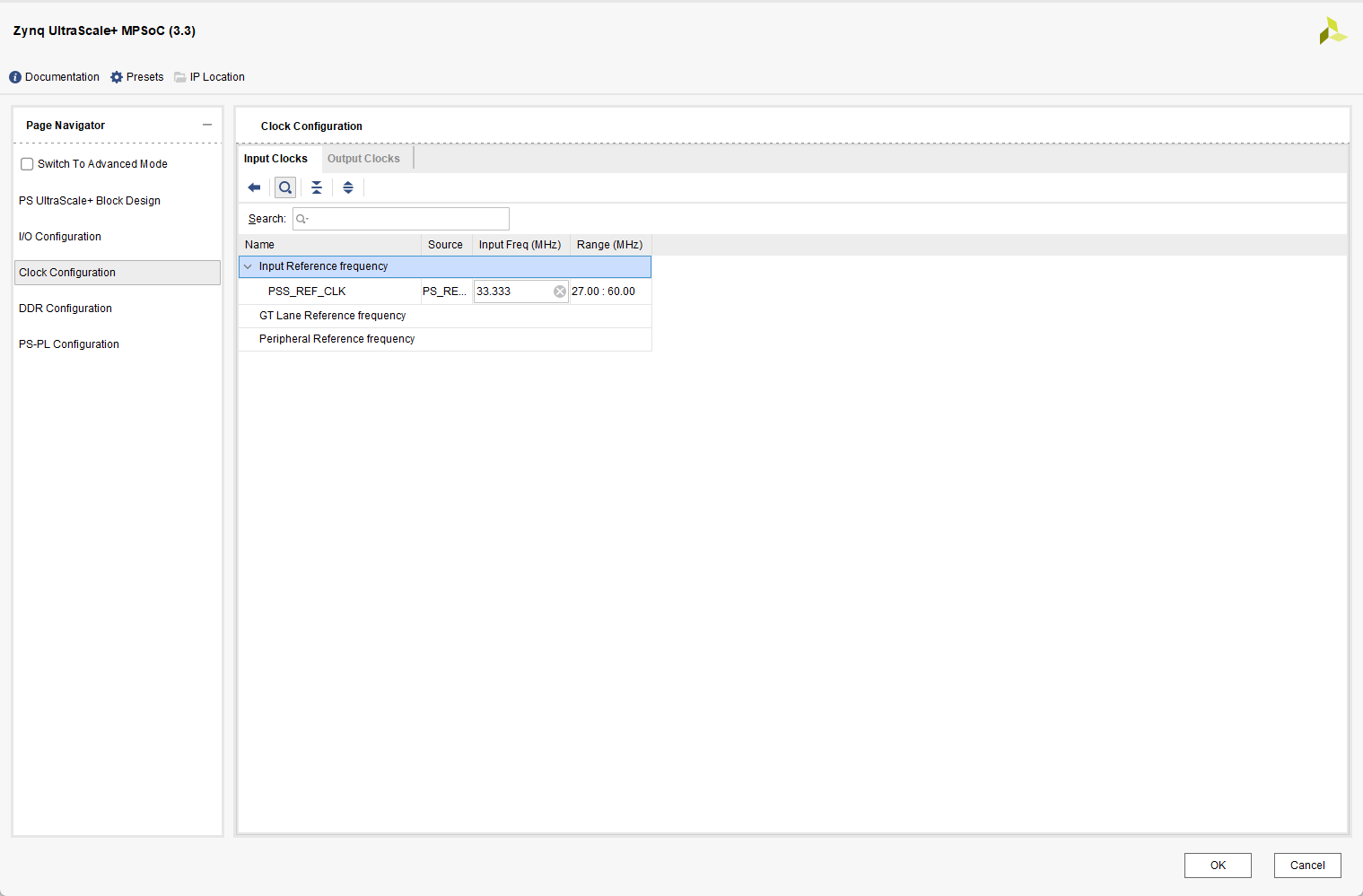

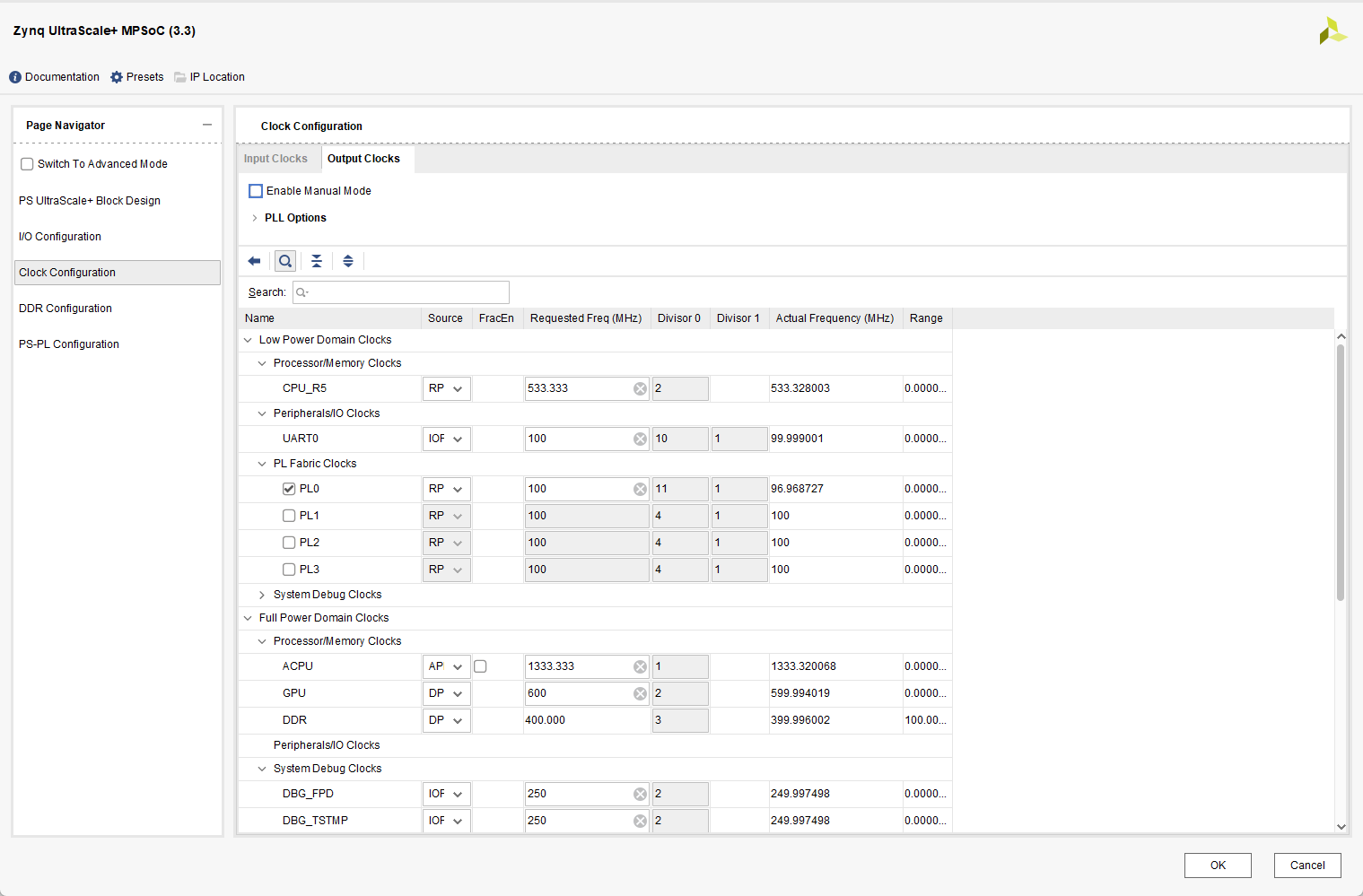

三. 时钟配置

一、输入时钟(Input Clocks):系统的 "时钟源"

输入时钟是整个系统的基准时钟来源,图中主要包含三类:

- PSS_REF_CLK :

- 是 PS 侧的核心参考时钟,源为

PS_REF,输入频率33.333MHz,工作范围27.00~60.00MHz。它是 APU、RPU、外设等模块时钟的 "母钟",通过 PLL 倍频 / 分频生成各类输出时钟。

- 是 PS 侧的核心参考时钟,源为

- GT Lane Reference frequency :(图中未完全显示,通常用于高速串行接口如 PCIe、GTH 等)

- 为高速串行收发器提供参考时钟,确保高速数据传输的时序稳定性。

- Peripheral Reference frequency:(图中未完全配置,用于外设时钟参考)

二、输出时钟(Output Clocks):各模块的 "定制化时钟"

输出时钟通过 PLL 对输入时钟进行倍频、分频,为不同功能模块(APU、RPU、GPU、外设、PL 等)生成差异化时钟,同时兼顾性能、功耗、时序约束的平衡。配置界面按电源域和功能模块分层组织:

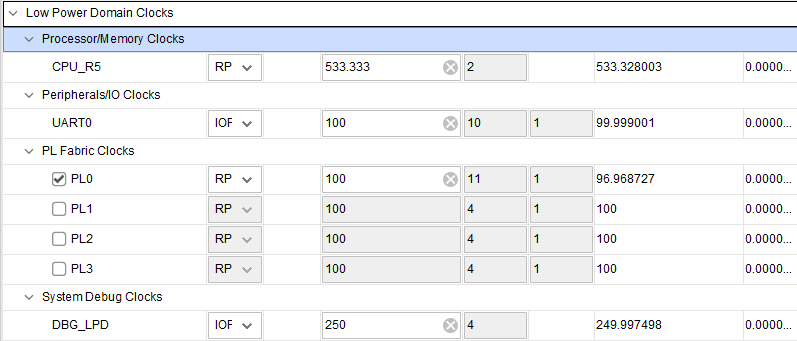

1. 低功耗域时钟(Low Power Domain Clocks)

用于 RPU(Cortex-R5)、低功耗外设等对功耗敏感的模块,兼顾实时性与低功耗:

- 处理器 / 内存时钟(Processor/Memory Clocks) :

CPU_R5:为实时处理器 Cortex-R5 提供时钟,请求频率533.333MHz,经分频后实际频率533.328MHz,满足实时任务的低延迟需求。

- 外设 / IO 时钟(Peripheral/IO Clocks) :

UART0:为串口外设提供时钟,请求频率100MHz,经分频后实际99.999MHz,确保串口通信的波特率精度。

- PL Fabric 时钟(PL Fabric Clocks) :

PL0、PL1等:为 PL 侧可编程逻辑提供时钟,例如PL0请求100MHz,经分频后实际96.97MHz,用于驱动 PL 内的 DSP 核、逻辑电路等。

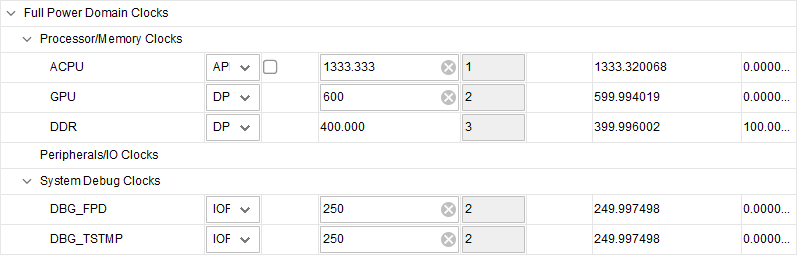

2. 全功耗域时钟(Full Power Domain Clocks)

用于 APU(Cortex-A53)、GPU、DDR 等高功耗但高性能的模块:

- 处理器 / 内存时钟(Processor/Memory Clocks) :

APU:为应用处理器 Cortex-A53 提供时钟,请求频率1333.333MHz,实际1333.320MHz,满足 Linux 系统、复杂算法的高性能需求。GPU:为图形处理器提供时钟,请求600MHz,实际599.994MHz,支撑图形渲染或并行计算任务。DDR:为外部内存 DDR 提供时钟,请求400MHz,实际399.996MHz,保障内存带宽以支持大数据吞吐。

- 外设 / IO 时钟(Peripheral/IO Clocks):覆盖高速外设(如 PCIe、SATA 等)的时钟需求,确保高速接口的时序稳定性。

- 系统调试时钟(System Debug Clocks) :

DBG_FPD、DBG_TSTMP:为调试模块提供时钟,请求250MHz,实际249.997MHz,支持在线调试、断点跟踪等功能。

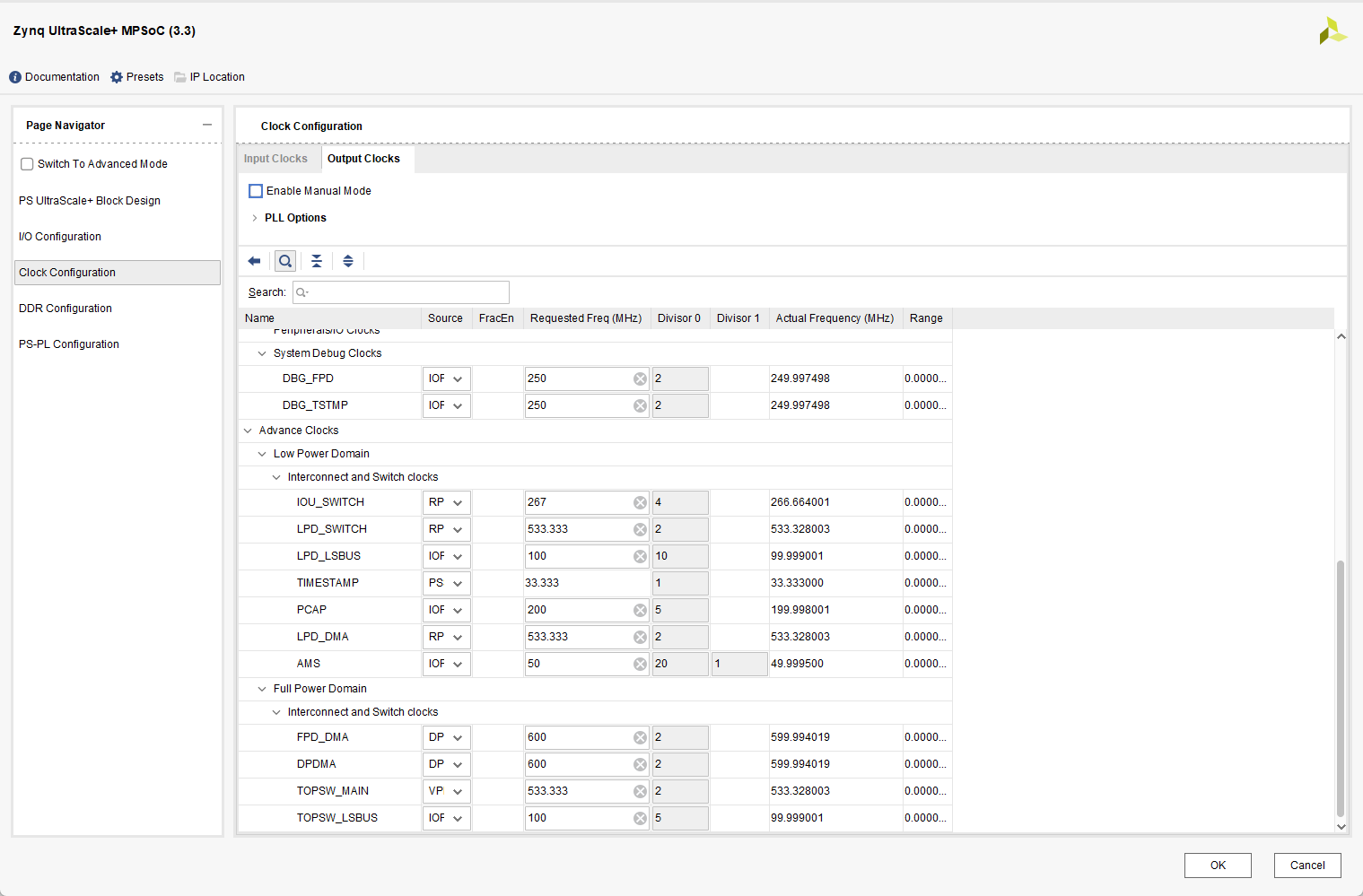

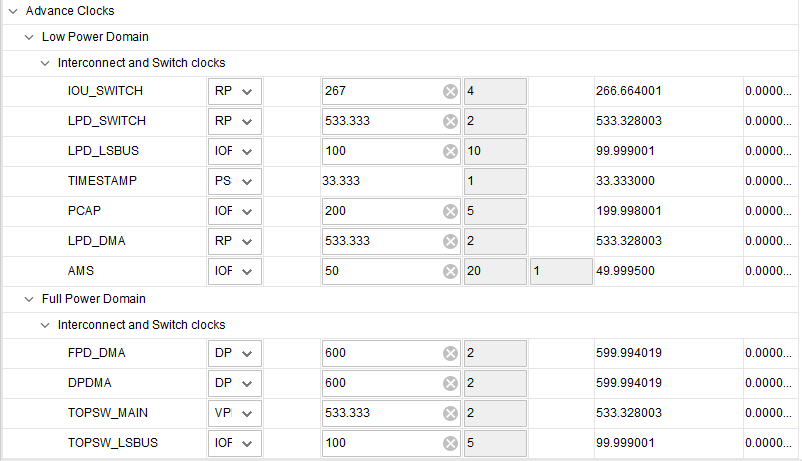

- 高级时钟(Advance Clocks) :

- 互联开关时钟(如

IOL_SWITCH、LPD_SWITCH):为 PS 内部总线互联提供时钟,确保数据在不同模块间的稳定传输。 - DMA 时钟(如

LPD_DMA、FPD_DMA):为直接内存访问模块提供时钟,保障高速数据搬运的效率。

- 互联开关时钟(如

注:LPD(Low Power Domain,低功耗域)和 FPD(Full Power Domain,全功耗域)

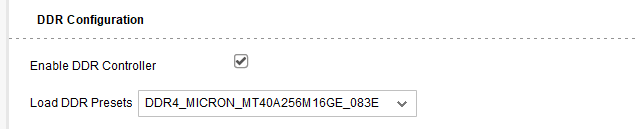

四. DDR配置

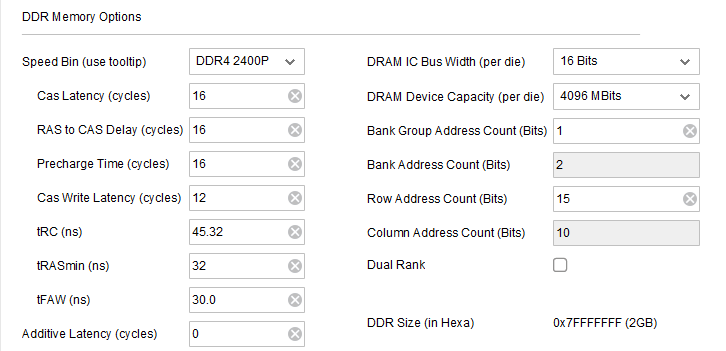

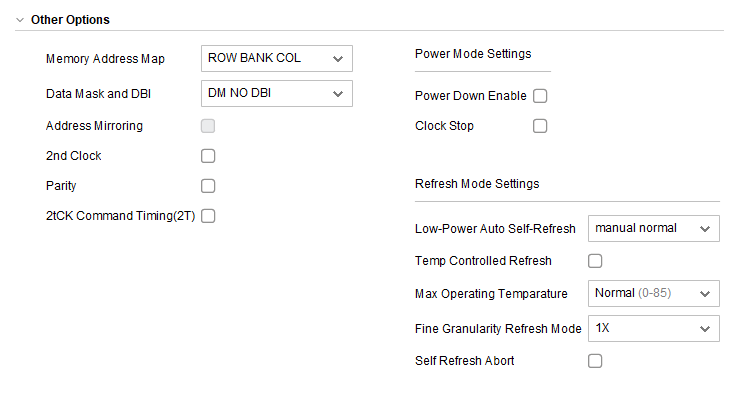

PS 硬件配置的是 4片 MICRON 的 MT40A512M16LY-062E 型号的 DDR4。可以在载入 DDR 预设时选用相近的这个型号,方便在下面载入参数,再根据手册中进行对应的修改,修改过参数后,这里会变成 custom。

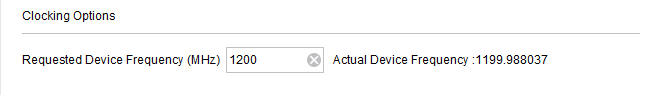

这里 IP 支持的频率范围为 100-1200MHz,主要是由于 DPLL 的 VCO 频率设置为了 2400MHz,对于 DDR 时钟只能进行整数分频,因此最大为 1200MHz

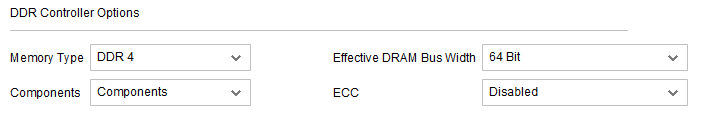

单片 DDR 是 16-bit,4 片构成 64-bit 数据位宽,硬件上直接用 DDR 芯片所以选择 components

上述选项一般情况下保持默认即可;

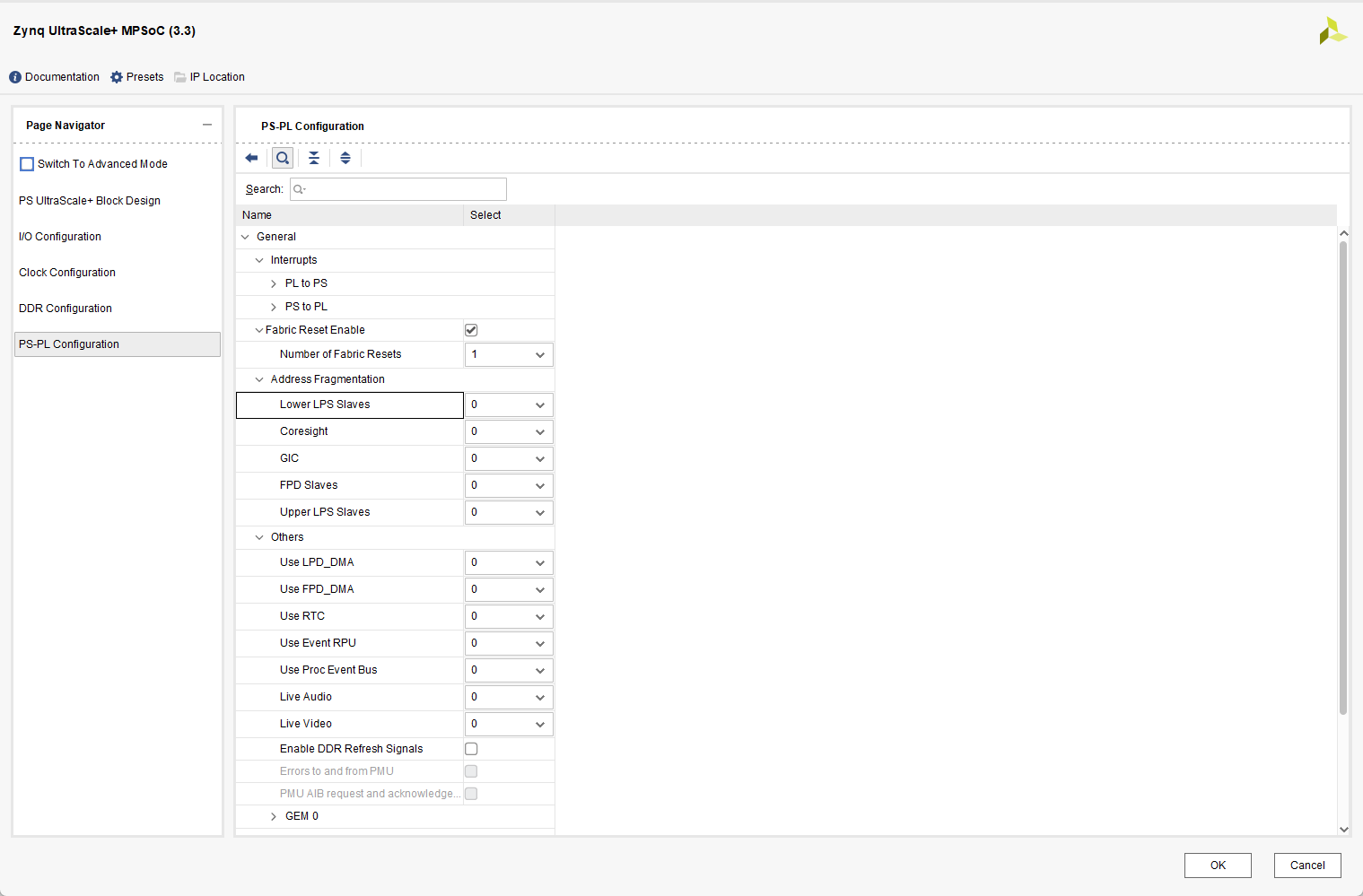

五. PS-PL配置

一、通用配置(General):基础交互与功能使能

1. 中断(Interrupts)

- PL to PS :PL 向 PS 发送中断请求,用于 PL 通知 PS 事件(如 "核数据采集完成""PL 逻辑异常")。

- 核场景示例:PL 内 DSP 核完成 γ 能谱预处理后,触发中断让 PS(APU)读取结果并存储。

- PS to PL :PS 向 PL 发送中断请求,用于 PS 控制 PL 动作(如 "启动 PL 数据采集""重置 PL 逻辑")。

- 核场景示例:PS(RPU)发送中断,触发 PL 内 ADC 开始采集核脉冲信号。

2. Fabric Reset(逻辑复位)

- Fabric Reset Enable :启用 PS 对 PL 逻辑的复位控制,可在系统启动时初始化 PL,或 PL 逻辑出错时强制重置。

- 核场景示例:核辐射导致 PL 逻辑 "单粒子翻转" 时,PS 触发 Fabric Reset 恢复 PL 功能。

- Number of Fabric Resets:配置复位信号的数量(通常设为 1),确保 PL 逻辑全范围复位。

3. 地址分段(Address Fragmentation)

- Lower LPS Slaves、Coresight、GIC、FPD Slaves 等 :配置 PS 可访问的 PL 内 AXI 从设备数量,对应不同 功耗域(LPS 低功耗、FPD 全功耗) 和功能模块(调试、中断控制器等)。

- 作用:确保 PS 能正确寻址 PL 内的各个模块(如 DSP 核、AXI 从设备),避免地址冲突。

地址分段允许根据在 MPSoC 中分配外设的地址空间来扩展外设,可选项如设置中所示。通过配置,地址编辑器(BD中的address editor)中只会显示所选外围设备的列表。这可用于要求为 PL 组件提供更多地址空间的情况,而不是分配给 MPSoC 可寻址组件的单个地址块。

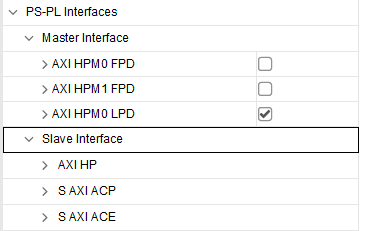

二、AXI 总线接口(PS-PL Interfaces):高速数据传输的血管

ZYNQ 中 PS 和 PL 之间的AXI 总线 是高速数据传输的核心通道,分为Master(PS 为主,访问 PL)和 Slave(PL 为主,访问 PS)两类接口,且区分功耗域(FPD 全功耗、LPD 低功耗):

1. Master Interface(PS 主设备 → PL 从设备)

- AXI HPM0 FPD :全功耗域的高性能主接口 ,数据宽度 128 位,用于 PS(APU)向 PL 传输大数据量配置(如复杂 DSP 核的系数矩阵)。

- 核场景:PS 向 PL 内的三维辐射场重建模块写入校准参数,带宽需求高,选 FPD 接口。

- AXI HPM0 LPD :低功耗域的主接口,数据宽度 32 位,用于 PS(RPU)向 PL 传输实时控制信号(如探测器触发指令)。

- 核场景:RPU 向 PL 内的脉冲采集模块发送 "启动采集" 指令,需低延迟、低功耗,选 LPD 接口。

2. Slave Interface(PL 主设备 → PS 从设备)

- AXI HP0 FPD :全功耗域的高性能从接口 ,PL 可直接读写 PS 的 DDR 内存,用于 PL 向 PS 传输海量数据。

- 核场景:PL 内 ADC 采集的原始核数据(每秒数百 MB),通过 AXI HP0 FPD 直接写入 PS 的 DDR,避免数据瓶颈。

- 其他 AXI HP/ACP/ACE 接口:按需启用,如 AXI ACP 用于 PL 访问 PS 的 L2 缓存,提升数据读取效率。

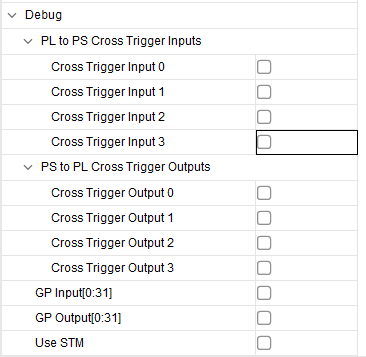

三、调试配置(Debug):系统调试的桥梁

1. 交叉触发(Cross Trigger)

- PL to PS Cross Trigger Inputs:PL 向 PS 发送调试触发信号,用于 PL 事件触发 PS 调试动作(如 PL 内逻辑异常时,触发 PS 断点)。

- PS to PL Cross Trigger Outputs:PS 向 PL 发送调试触发信号,用于 PS 控制 PL 调试(如 PS 触发 PL 内逻辑的单步执行)。

- GP Input/Output:通用调试触发引脚,可自定义 PL 和 PS 之间的调试信号交互。

- Use STM:启用系统跟踪模块(STM),用于记录 PS 和 PL 之间的交互时序,辅助调试复杂逻辑(如核数据采集的时序问题)。

以 "核探测器实时采集与分析系统" 为例,典型配置逻辑:

- 数据传输通道 :

- PL 内 ADC 采集核脉冲 → 通过 AXI HP0 FPD 高速写入 PS DDR(大数据量、高性能需求)。

- PS(RPU)通过 AXI HPM0 LPD 向 PL 发送 "采集频率配置" 指令(低功耗、实时性需求)。

- 中断交互 :

- PL 采集完成 → 触发 PL to PS 中断,通知 APU 读取数据并分析。

- PS 需紧急停止采集 → 发送 PS to PL 中断,控制 PL 停止 ADC。

- 复位与调试 :

- 系统启动时,PS 触发 Fabric Reset 初始化 PL 逻辑。

- 调试阶段,启用 Cross Trigger 和 STM,跟踪 PL 采集时序与 PS 分析逻辑的同步性。