目录

一、寄存器与锁存器的区别

经过前面的学习我们明白了,锁存器其实就是一个能保持状态不变的环形电路。他的关键在于保持不变,那么寄存器又是什么呢?他和锁存器有什么不同?

(1)触发机制不同:寄存器仅在时钟信号的特定边沿(上升沿 / 下降沿)更新数据,边沿过后输入信号变化不影响输出;锁存器在时钟信号的高 / 低电平期间持续响应输入,电平不变时保持数据。

(2)抗干扰能力不同:寄存器抗干扰性强,仅在边沿瞬间采样,受输入信号抖动影响小;锁存器在电平有效期间易受输入噪声干扰,可能误触发。

(3)使用场景不同:寄存器适合同步时序电路,用于精确时钟控制下的数据存储(如 CPU 寄存器、移位寄存器);锁存器适合异步电路或电平控制的数据暂存(如地址锁存、简单数据缓冲)。

简单来说就是寄存器往往用多个锁存器、或者触发器电路来构建一种边沿更新数据的元件。他既有锁存器保持数据持久化的特点,又不局限于1位数据,往往可以有8位甚至更多位。

二、移位寄存器

(1)移位寄存器的基本原理

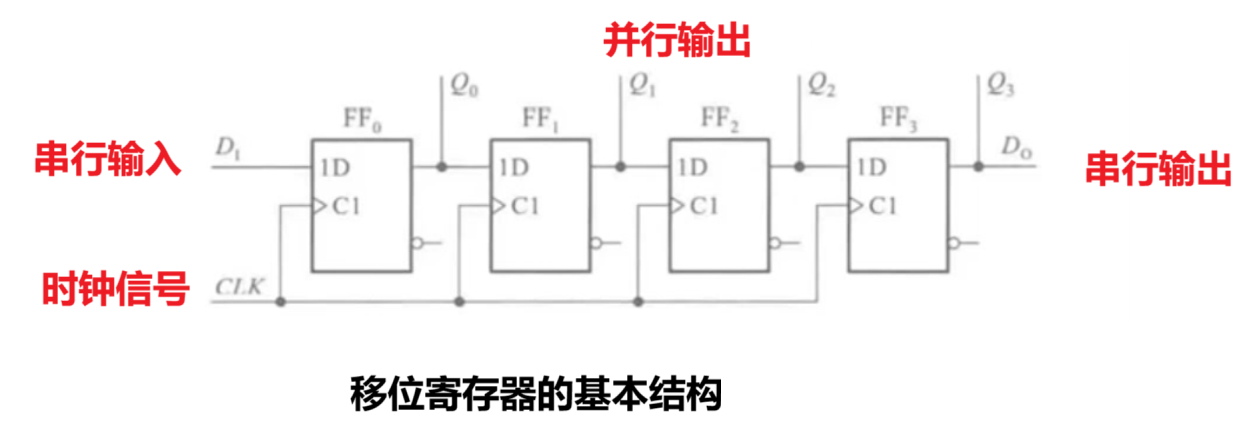

移位寄存器就是用多个D触发器级联构成的。他可以存储多位数据,不仅支持一位一位的向左、向右移动的串行输出;还能支持并行输入输出。是数字电路很重要的基本单元。

简单分析其工作原理:

Di处输入串行数据,当CLK产生一个上升沿时,会将Di的数据移入下一级D触发器。逐级往后移动,呈现移位的效果。

而并行输出是把各级D触发器的输出端引出来,直接对外输出。

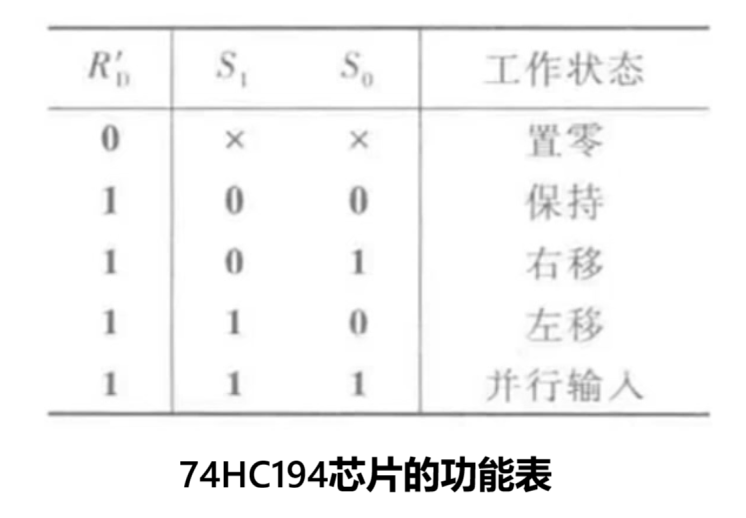

(2)封装成74HC194芯片

由于移位寄存器十分基本且重要,人们将其封装成了一颗芯片。他在上述结构的基础上扩展补充了一些功能,比如左移、右移、置零、保持、并行输入等等。

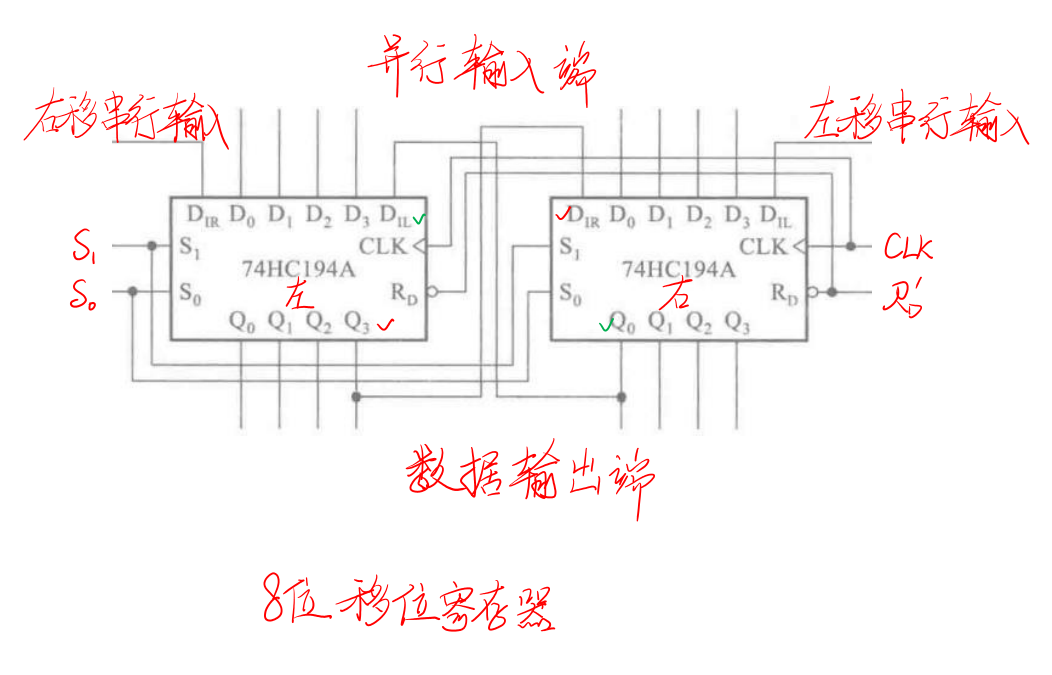

(3)级联

两颗74HC194芯片就能级联成8位的移位寄存器。其实只用把上一级的输出级联到下一级的输入即可。即把左边的Q3连接到右边的DiR;把右边的Q0连接到左边的DiL。而并行输入端、8位数据输出端则直接用原本的就行。

(4)乘除法运算

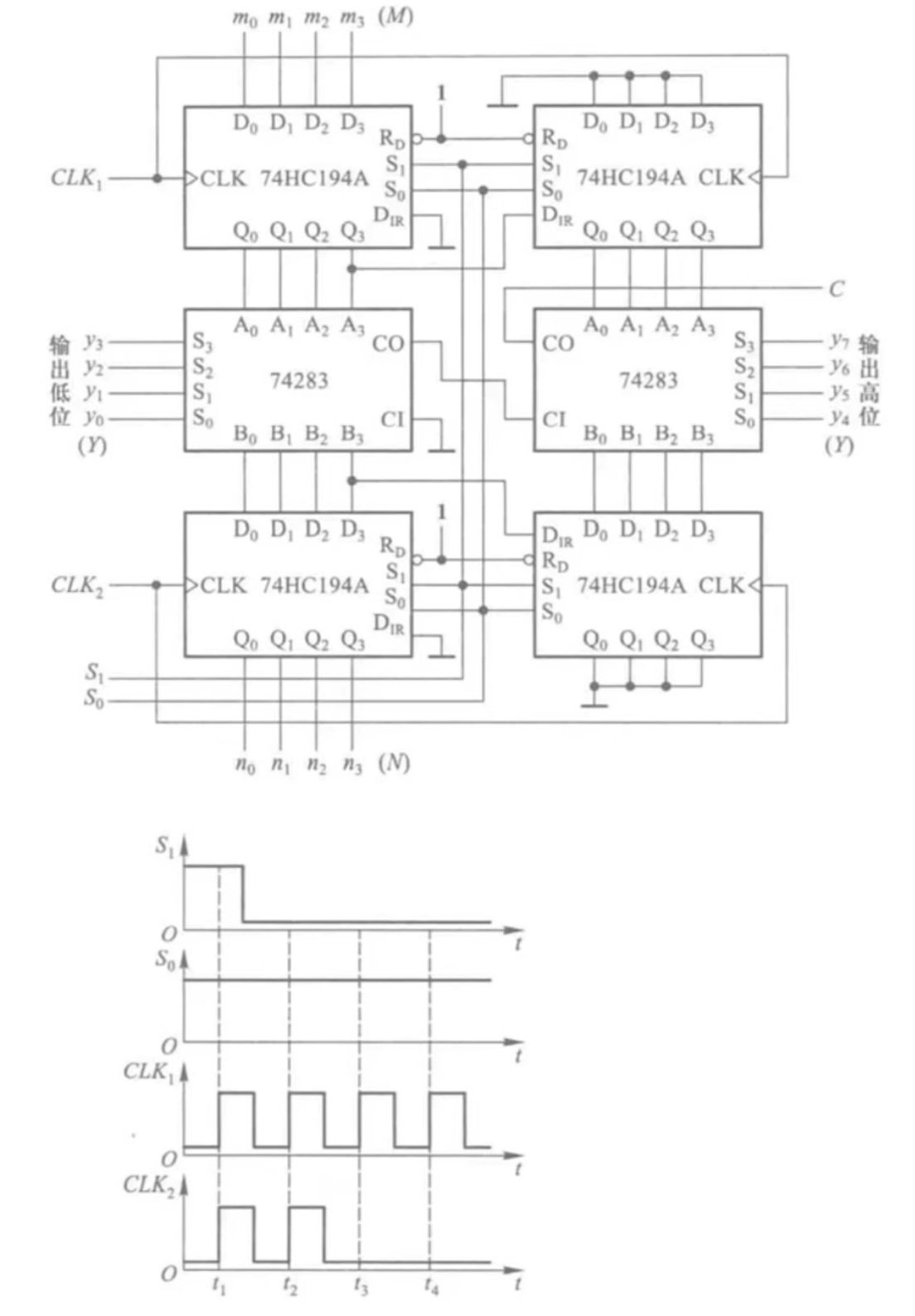

我们来分析一下该电路的工作流程:

(1)首先在两个移位寄存器的输入端输入M、N两个4位数值。

(2)在CLK上升沿的时候,将数据往右移动(虽然图中是从左往右移动,但是是低位向高位移动),即数据乘2了。

(3)由于CLK2只有两个上升沿,所以N只乘以4;而CLK1有4个上升沿,所以乘以16。

(4)最后16M和4N在中间的加法器相遇,低位加低位,高位加高位。最终得到8位的16M+4N的结果。

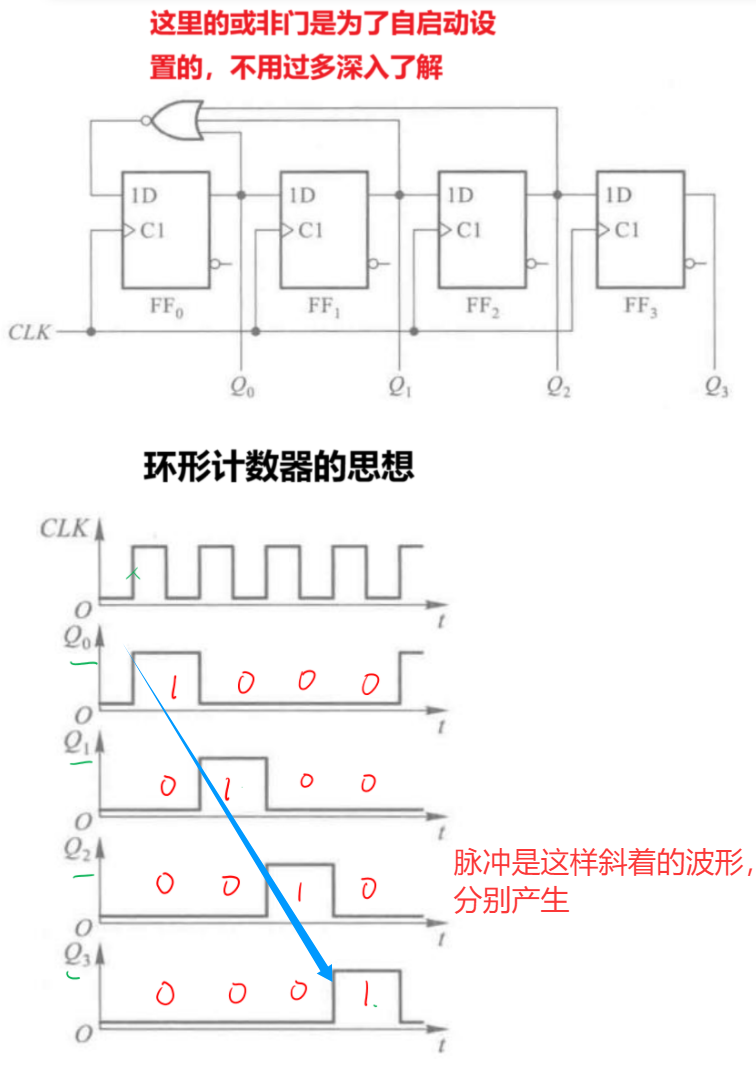

(5)构造环形计数器

如果将移位寄存器的输出端重新连接到输入端,则形成了一个环形,状态将永远在里面循环。

(1)假设你在输入1000这个值,在4个上升沿之后,每个触发器就会记录住1、0、0、0。

(2)此后就算你不输入了,Q3的输出也会重新输入到Di处进行循环,即4状态循环。

然而这样的环形计数器存在一些问题:

(1)无法自启动:当电路由于外部干扰错误的进入某个循环,无法立马恢复到我们想要的状态。

(2)利用率低:我们说4个2进制位最多可以表示16种状态,而这里仅仅只利用了其中的4个循环态。

约翰逊为了提高利用率,将其输出端改到了FF3的Q'处,构成了扭环形计数器。他的本质与环形技术器一致,但是可以在8个状态中循环了。

三、顺序脉冲发生器

(1)移位寄存器构造顺序脉冲

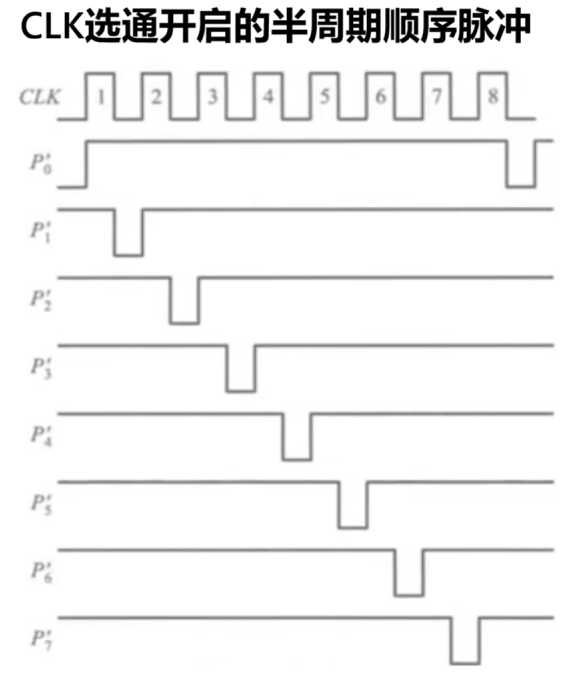

所谓的顺序脉冲发生器,就是在每个始终周期内,只有一个端口输出脉冲,其余端口都输出0/1(不论是0还是1,只要保证其余的都输出一样即可)

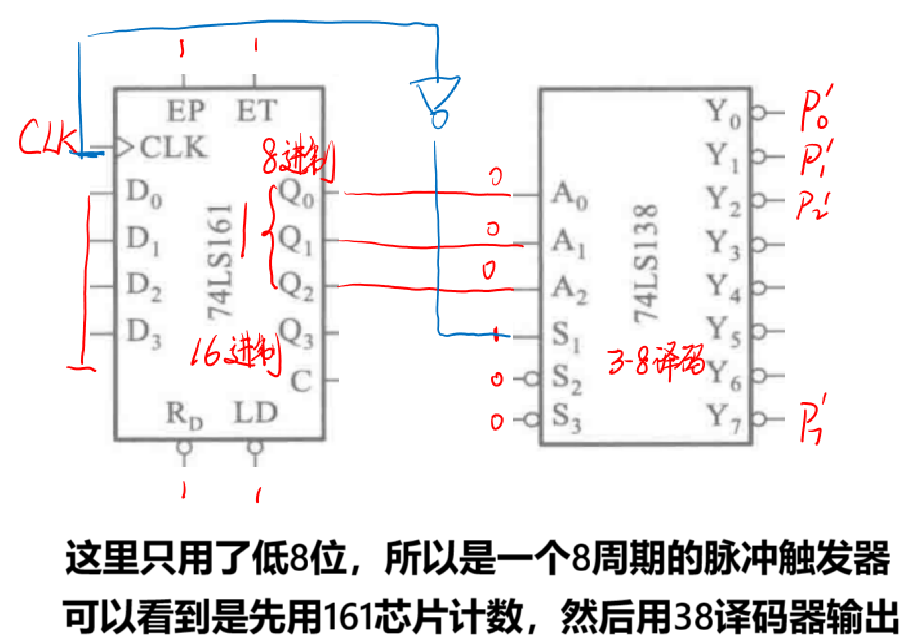

但是这样需要多少个状态的脉冲,则需要多少个触发器,比较浪费资源。于是人们想到用计数器先计数,然后将计数的输出传给译码器,由译码器再来输出。比如你要16个周期的顺序脉冲,原思路需要16个D触发器,而现在只需要1个161芯片+2个138译码器即可,大大减少了硬件的成本。

(2)计数器+译码器构造顺序脉冲

关于图中蓝色部分其实是选通信号,让38译码器间歇性工作来规避竞争冒险现象。

因为芯片的运算必定有延迟,所以161芯片输出给38译码器的可能出现一定竞争现象,而由于延迟通常很小,往往远小于半个时钟周期。

这里38译码器的使能端接入CLK反向的选通信号后,会在CLK=1期间不工作,从而不响应。而当CLK经过半个周期后才被使能工作。直接避免了竞争-冒险现象,变得更加安全。

不过这种方式使得输出的顺序脉冲宽度只有原来的一半。

四、序列信号发生器

所谓序列信号,就是一个串行的特定信号。比如10010011串行发送出去就是一个序列信号。一般情况下,一款序列信号发生器设定好了就就会持续发送这种特殊序列,不能改变。

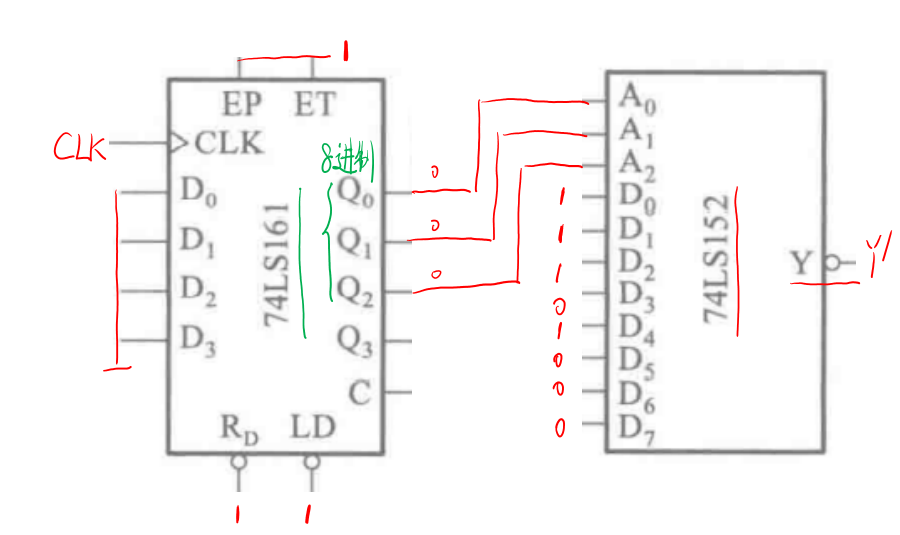

(1)计数器+数据选择器构造序列信号

比如这里我们想要发送00010111这个8位的序列信号:

其中161芯片负责8状态切换,而数据选择器将他的8个状态作为地址去选择输出。在时钟CLK的驱动下最终串行发出。