实验一、BCD加法器设计

实验要求:

- 使用Verilog语言设计4位二进制输入的BCD码加法器(输入数值范围0~9),能够自动识别输入合规性,输入值>9,输出一个E字符;

- 输出功能定义如下:

- 1、7段数码管低2组作为加法器结果输出,结果范围0-18,十进制格式输出;

- 2、7段数码管最高1组作为输入错误告警,输入数据>9,则输出E;

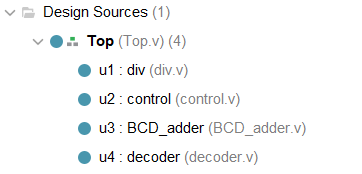

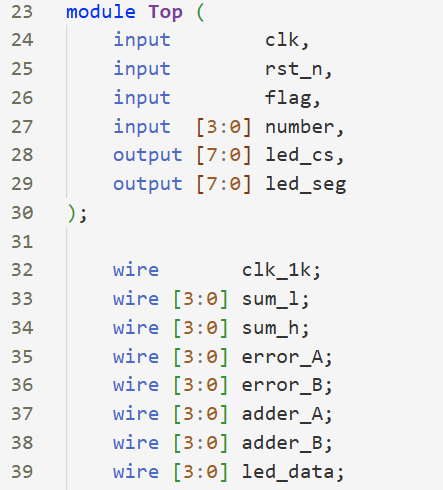

- 代码结构如下,下面将进行各模块说明:

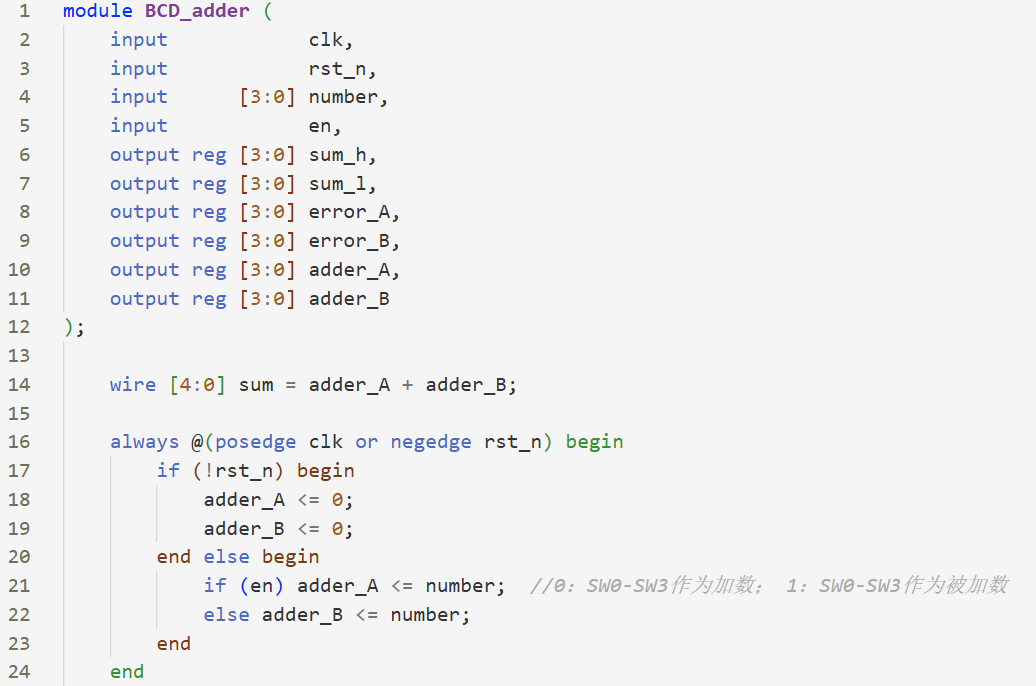

1. BCD_adder模块:

根据实验要求,我们使用低四位拨码开关作为加数/被加数的输入,使用第8位拨码开关选择输入数据为加数还是被加数:

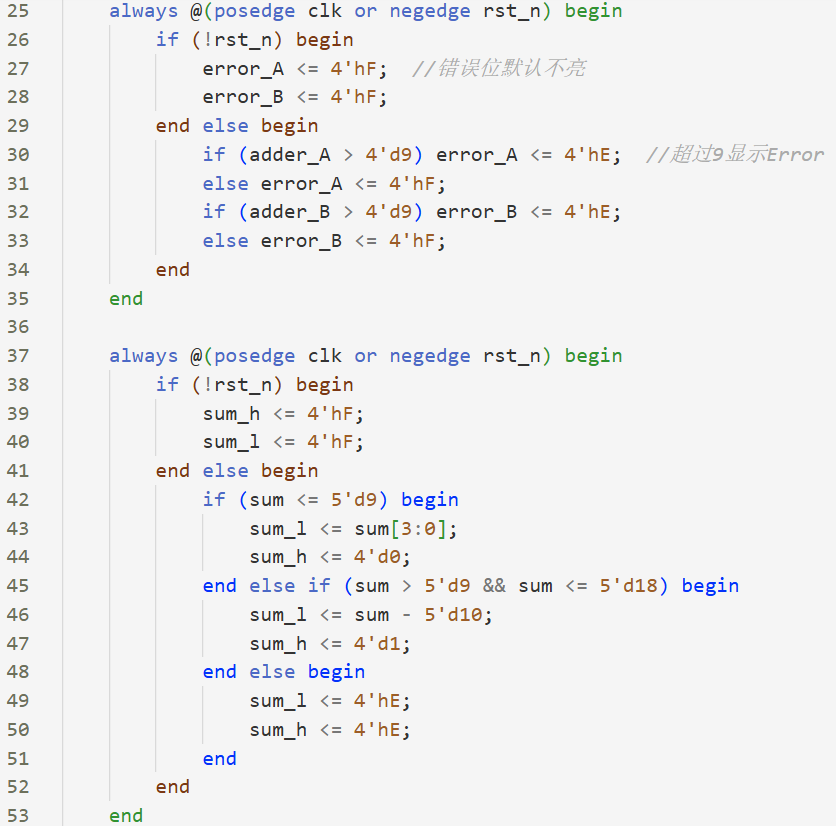

BCD加法逻辑如下,如果加数或被加数超过9,则将对应错误位置1,否则不亮;如果sum小于等于9,则直接输出和的低四位,如果sum大于9且小于等于18,则将输出的sum_h置1,将sum减10作为sum_l的输出;如果和大于18,则将sum_l与sum_h标记为Error:

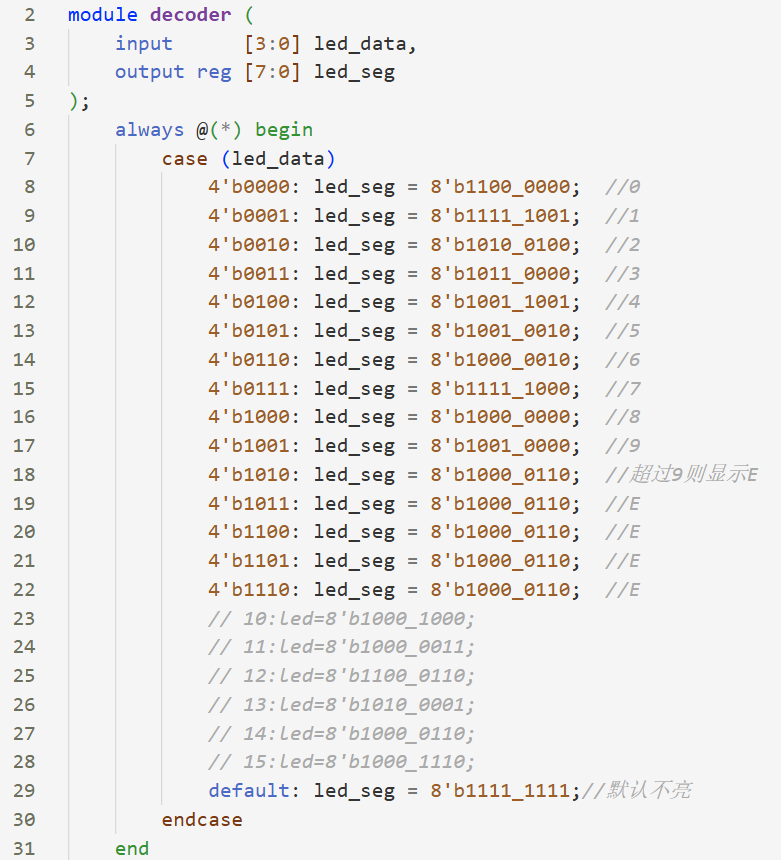

2. 数码管译码模块

七段共阳极数码管码表如下,对于本实验,当数据大于9时则显示E:

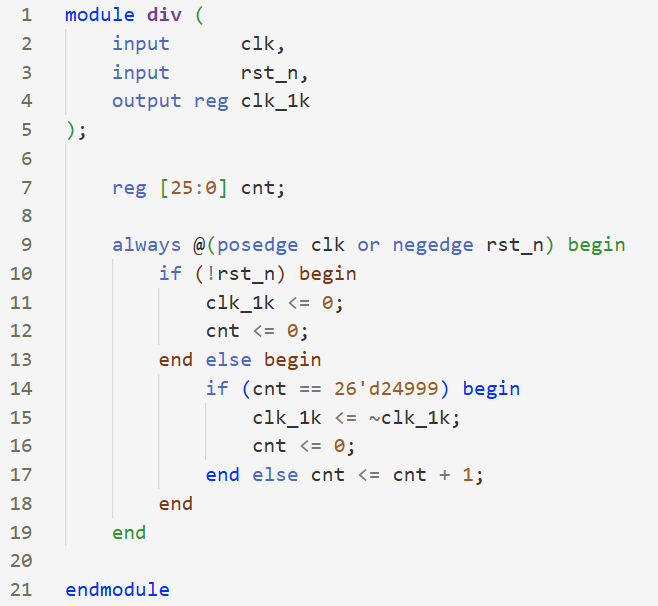

3. 分频模块 & 数码管控制模块

对50MHz时钟进行分频得到1KHz时钟:

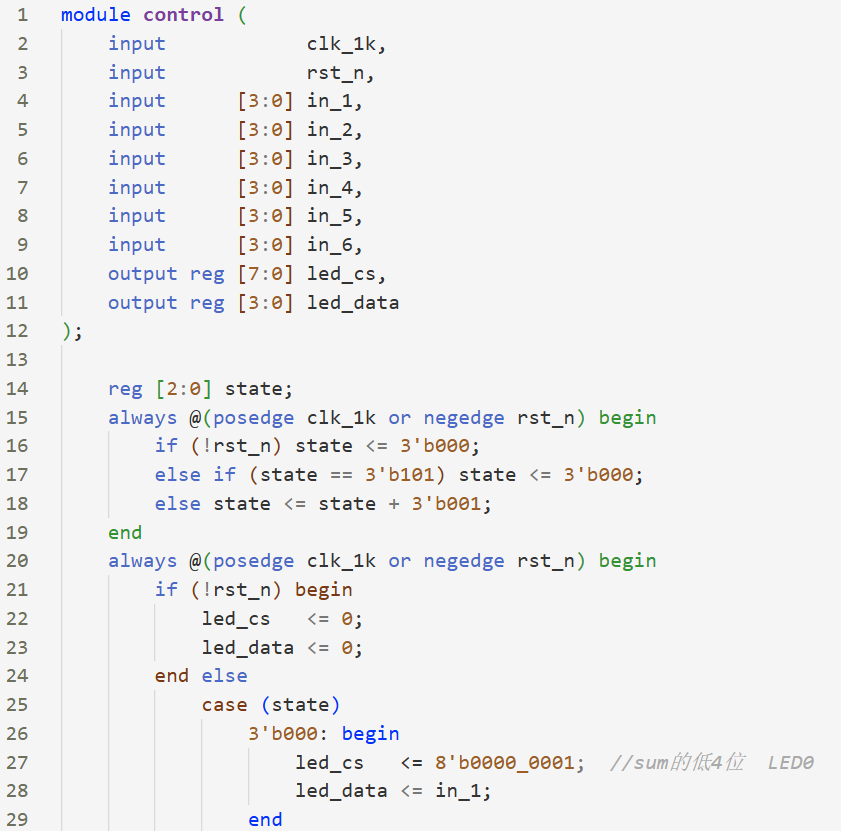

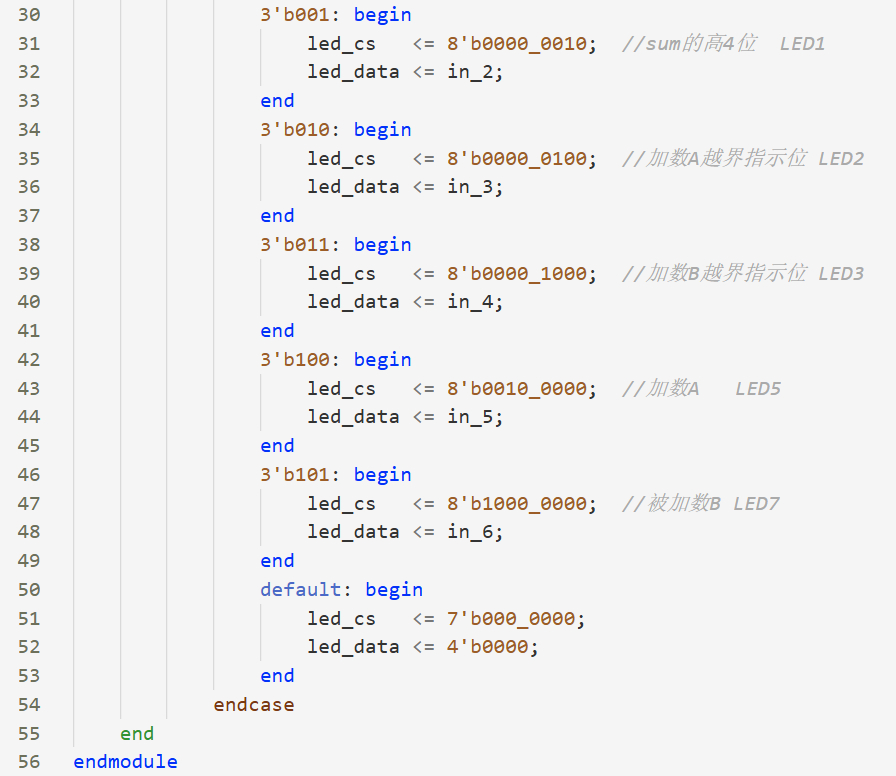

使用1KHz时钟信号驱动数码管,快速切换8个数码管的显示内容,利用视觉暂留效应,使其看起来同时点亮:

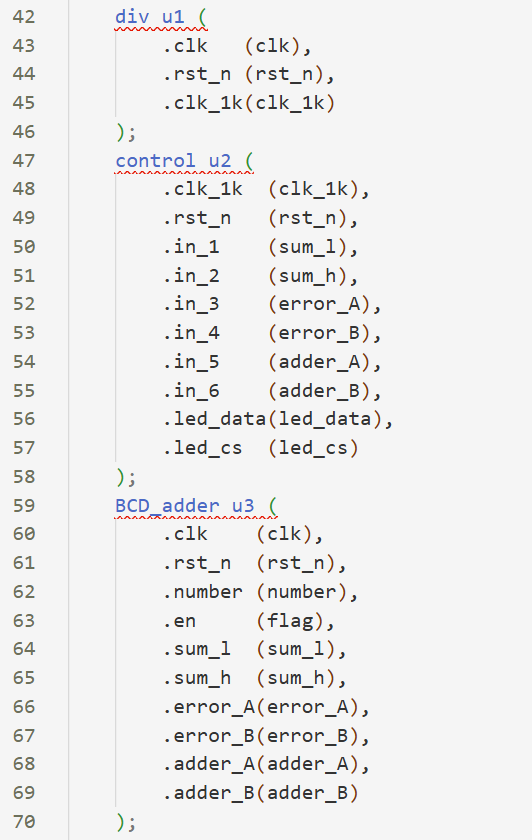

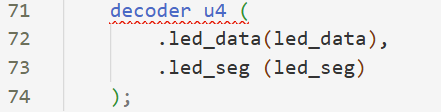

4、顶层模块

将各模块实例化并进行连接即可:

给出测试激励:

cpp

initial begin

rst_n = 0;

clk = 0;

flag = 0;

number = 0;

#10 rst_n = 1;

#100 number = 7;

#200 flag = 1;

number = 8;

#100000 flag = 0;

number = 6;

#100 flag = 1;

number = 4;

#100000 flag = 0;

number = 9;

#100 flag = 1;

number = 10;

#200;

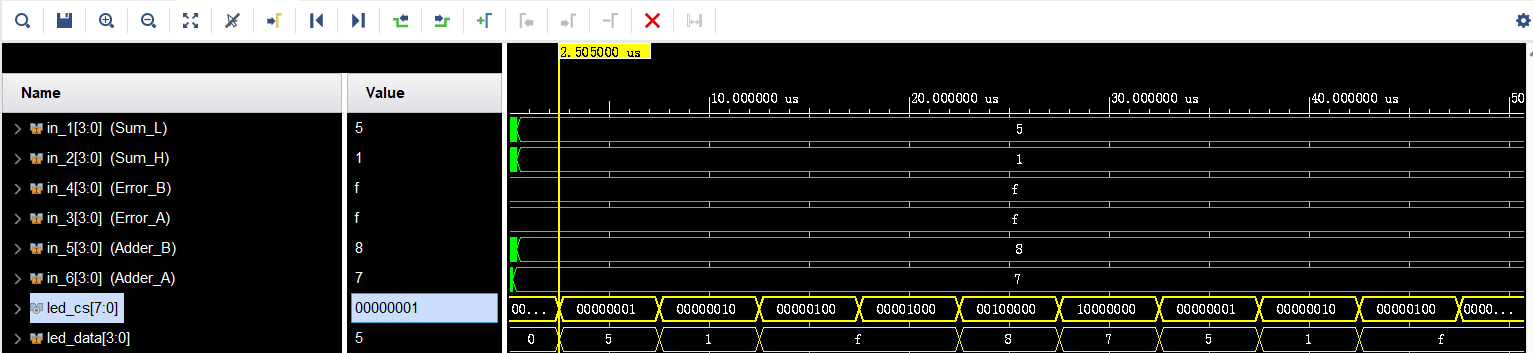

end仿真结果如下,正确实现功能:

led_cs控制数据在哪个数码管上显示,led_data控制显示数据的值:

约束文件:

cpp

# led_cs[7:0]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H22} [get_ports {led_cs[7]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN G20} [get_ports {led_cs[6]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN U1} [get_ports {led_cs[5]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN T1} [get_ports {led_cs[4]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN M21} [get_ports {led_cs[3]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN M22} [get_ports {led_cs[2]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN L20} [get_ports {led_cs[1]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN L21} [get_ports {led_cs[0]}]

# led_seg[7:0]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J21} [get_ports {led_seg[7]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H19} [get_ports {led_seg[6]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J20} [get_ports {led_seg[5]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN K19} [get_ports {led_seg[4]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN K22} [get_ports {led_seg[3]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN J22} [get_ports {led_seg[2]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN H20} [get_ports {led_seg[1]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN K21} [get_ports {led_seg[0]}]

# number[3:0]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN V2} [get_ports {number[0]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN W2} [get_ports {number[2]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN W1} [get_ports {number[1]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN W4} [get_ports {number[3]}]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN Y18} [get_ports rst_n]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN Y9} [get_ports flag]

set_property -dict {IOSTANDARD LVCMOS33 PACKAGE_PIN Y19} [get_ports clk]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {clk_IBUF}]上板验证:

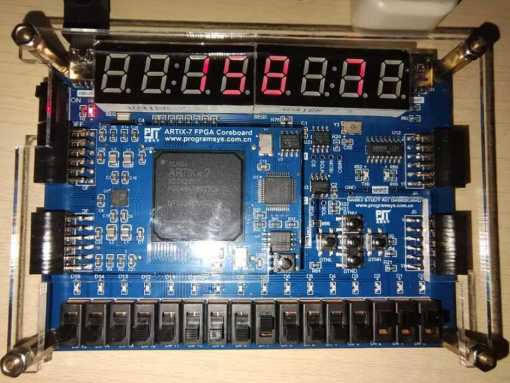

① 8+7=15:

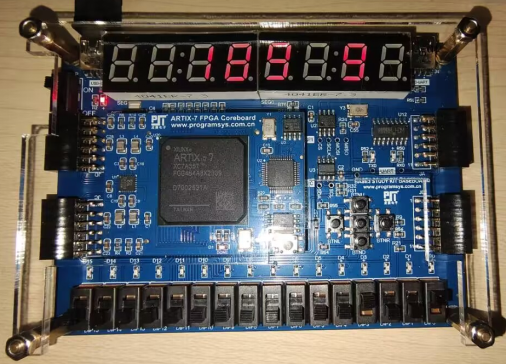

②9+9=18

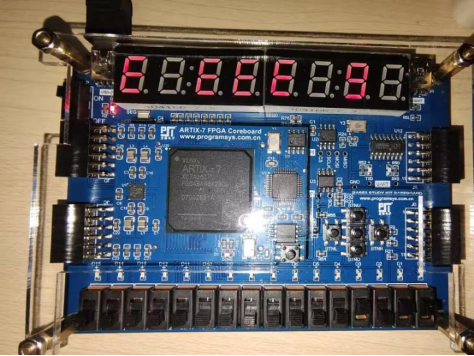

③加数为11,大于9,显示E;结果为11+9,大于18,显示EE:

------ 未完待续 ------