问题:与驱动联调,驱动端显示PCIE一直自动重启;

在FPGA侧,抓取信号发现,link up一直高低切换,LTSSM状态机也在进行状态切换。

phy_rdy_n信号:持续为0,说明复位没有发生高低跳变,但是LTSSM状态机改变意味着,PCIE链路训练有问题。

问题分析:

搭建单独的PCIE+BRAM的测试环境,PCIE启动正常。

而实际的工程是PCIE+Aurora的工作机制

考虑是PCIE与Aurora相互影响:

查看程序:

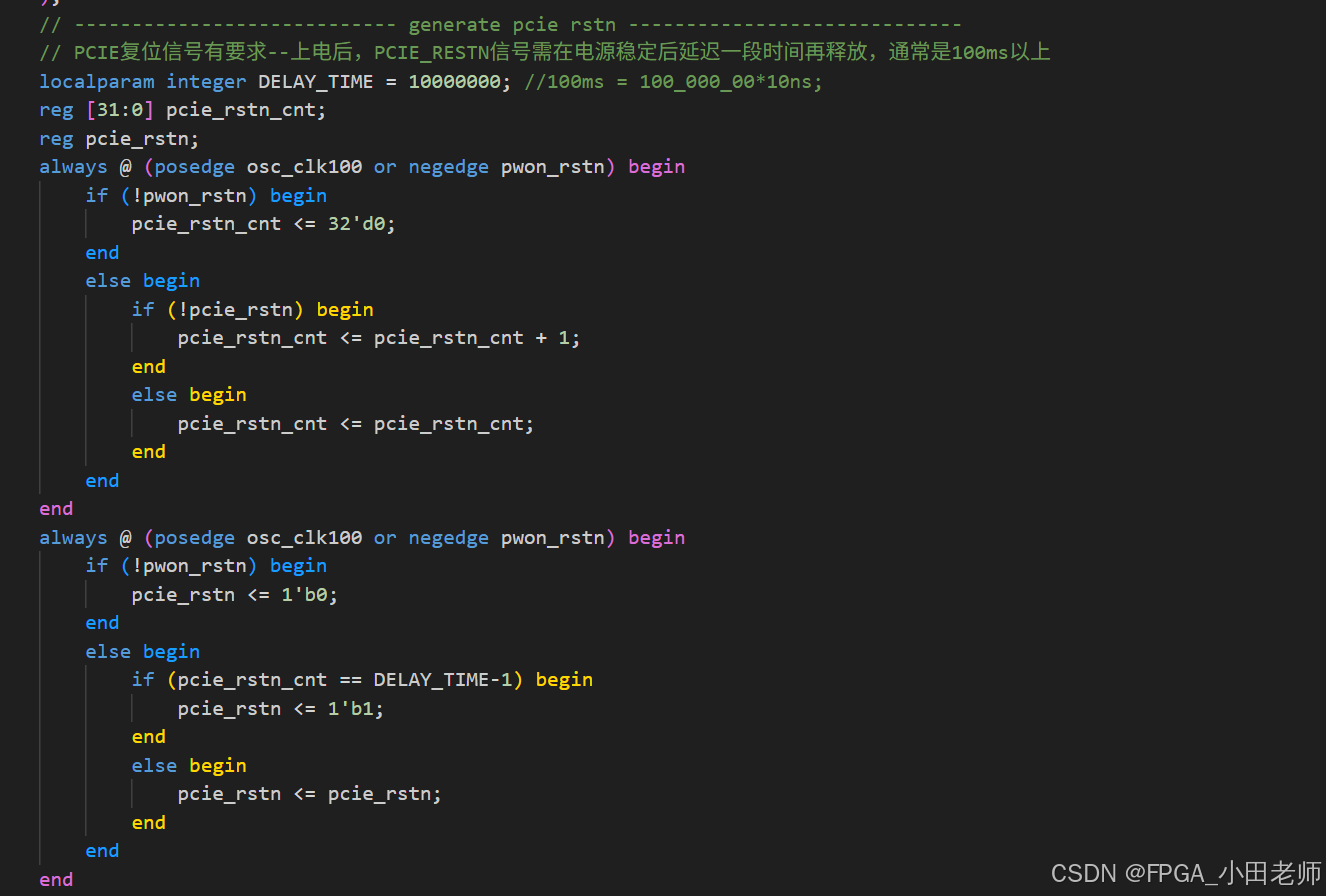

1 PCIE是上电100ms之后释放复位

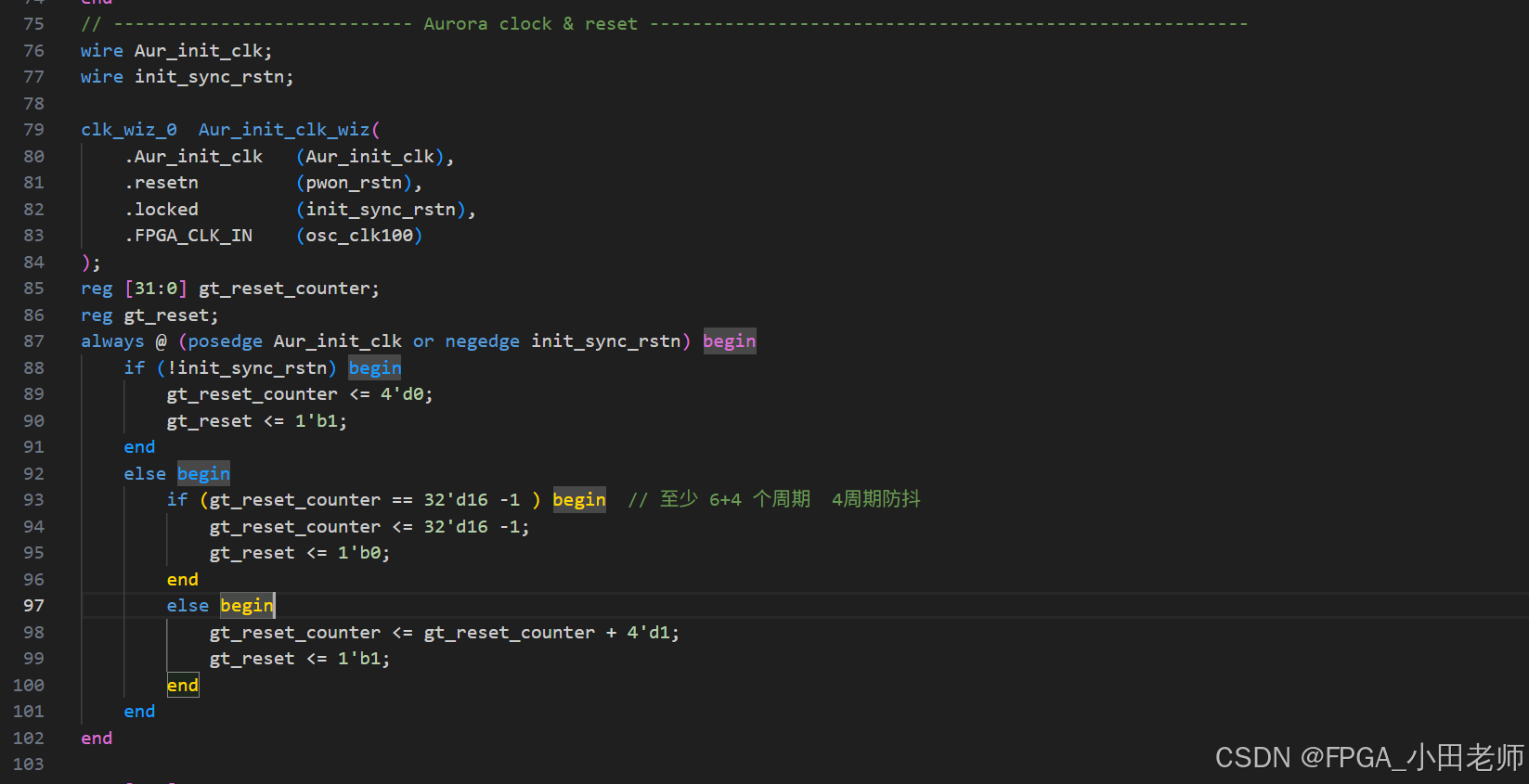

2 Aurora是上电之后大约16个clk就释放复位信号

虽然从理论上来说,满足各自的复位时序要求,但是PCIE释放复位的时机晚于Aurora接口。

我们本次使用的是Xilinx 7系列FPGA,具体型号是XC7A100T。这个器件有多个Quad,每个Quad包含4个收发器通道和一个共享的QPLL。我们使用的是两个不同的Quad(Quad213用于PCIe,Quad216用于Aurora)。

首先,我们需要理解这两个Quad在硬件上的时钟和复位架构。虽然每个Quad都有自己的QPLL,并且参考时钟是从外部输入的,但是它们之间可能存在一些共享的时钟资源,例如时钟缓冲器(如IBUFDS_GTE2)和时钟分布网络。此外,PCIe和Aurora IP核在初始化时可能会对全局的时钟和复位有一些要求。

根据Xilinx的文档,++PCIe硬核的复位序列有严格的要求。PCIe硬核必须在一个稳定的参考时钟下进行复位,而且这个参考时钟必须满足一定的稳定性要求。如果Aurora的GT复位在PCIe复位之前释放,那么Aurora的收发器可能会开始工作,并可能影响到共享的时钟资源(例如,如果两个Quad使用了同一个时钟缓冲器或同一个时钟区域),从而可能导致PCIe的参考时钟变得不稳定,进而导致PCIe初始化失败。++

另外,即使两个Quad使用独立的参考时钟,它们也可能共享同一个时钟区域(Clock Region)的资源,或者存在一些全局复位信号(例如,用户逻辑产生的复位)同时影响了两个Quad。因此,++为了保证PCIe的稳定初始化,通常建议先释放PCIe的复位,确保PCIe核心已经稳定,然后再释放其他收发器(如Aurora)的复位。++

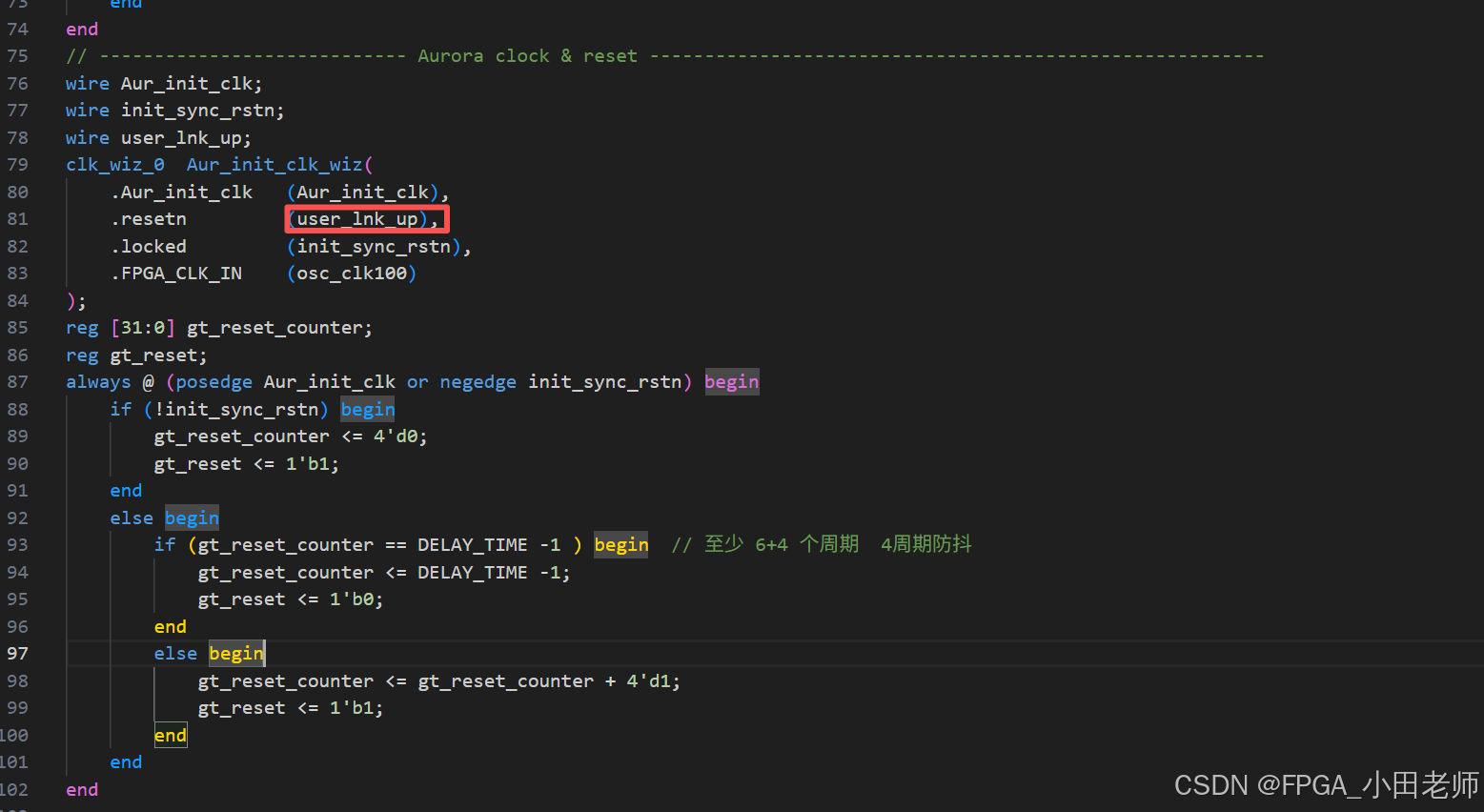

鉴于此,我们对复位时序进行修改:Aurora在等待PCIE的link up拉起之后100ms再释放Aurora的复位。

为什么PCIe的复位不能在Aurora的GT复位之后释放?可能是因为Aurora的GT复位释放后,Aurora收发器开始工作,可能会对时钟网络造成一些扰动(例如,时钟缓冲器的输出可能因为Aurora的复位释放而发生变化),而PCIe对参考时钟的稳定性非常敏感,因此必须确保在PCIe复位期间和复位之后,参考时钟都是稳定的。

所以,正确的做法是:

-

确保PCIe和Aurora的参考时钟稳定。

-

先释放PCIe的复位,并等待PCIe核心初始化完成(例如,等待PCIe的locked信号或稳定状态)。

-

然后再释放Aurora的复位。

这样能够保证PCIe在初始化过程中有一个稳定的时钟环境。