在JESD204B Subclass2系统中,确定性延时的精度主要依据device clock和SYNC。和subclass1相似,首先应确定应用中对确定性延时范围DLU的要求,然后再确定SYNC和device clock的延时匹配。

SYNC延时计算

和Subclass1采样SYSREF相似,Subclass2的时序主要在对SYNC的采样。但主要区别在SYNC为跨设备信号,没有办法独立分析,时序处理难度就更大,需要考虑的时序因素包括:

• 不同设备收到device clock的延时,clock distribution skew(DS_DCLK)

• 不同设备收到SYNC的延时,SYNC distribution skew (DS_SYNC)

• 采集SYNC的建立保持时间,时钟到输出SYNC延时

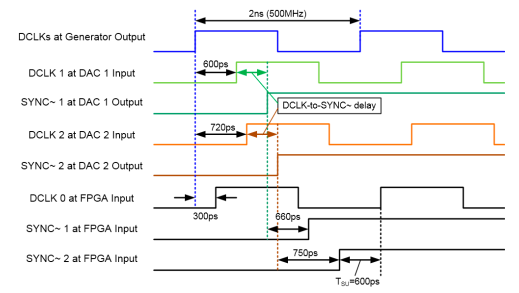

典型系统如下,时钟芯片给AD/DA和FPGA提供同源的deivce clock,SYNC通过片间连线实现。

协议附录B中建议Subclass2的deivce clock最高500M,如果有系统使用更高频率需求则建议换为Subclass1。所以示例中deivce clock定为最高的500MHz,示例PCB上不同走线延时分别为:

• Clock to FPGA = 300 ps

• Clock to DAC1 = 600 ps

• Clock to DAC2 = 720 ps

• SYNC~1 to FPGA = 660 ps

• SYNC~2 to FPGA = 750 ps

参照下图,在不考虑jitter和PVT(不同芯片不同电压不同温度)的情况下,假定device clock到SYNC输出边沿固定为230ns,和fpga采样最接近的是SYNC2,用周期减一下可以得到建立时间裕量是600ps。

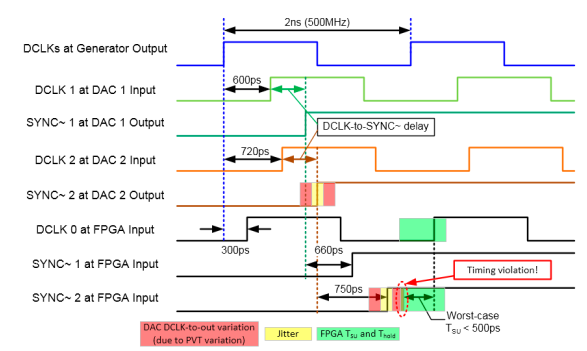

但实际应用中肯定是包含jitter和PVT因素的,假定jitter抖动范围150ps(图中黄色),PVT差异范围300ps(图中红色),假定建立时间要求是500ps,此时裕量为负值,即会出现时序违例。

总结确定性延时范围DLU的影响因素如下表,对于多设备还要多一个设备间sync的延时。

确定性延时范围

示例假定建立时间T_SU为½ T_DCLK,保持时间T_HOLD是¼ T_DCLK。

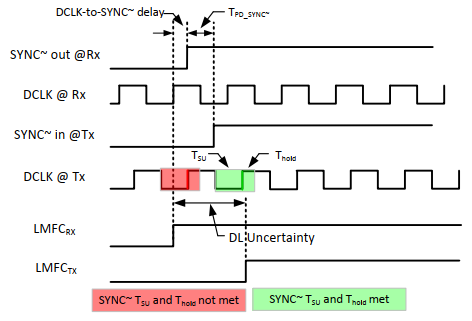

理想情况下DLU应该等于DS_DCLK,即大家都在同device clock边沿开始一个LMFC多帧,延时仅因为设备之间device clock的偏移产生,也就是DS_DCLK。实际这个延时从路径上看是由时钟到SYNC输出延时,SYNC片间延时和建立时间裕量构成,所以DLU计算如下。

DLU=DS_DCLK=T_CLKtoSYNC+T_PDSYNC+T_SU

下图中红色表示该边沿没采到sync,可能因为没满足建立保持时间也可能就是错过了,绿色表示采到sync。其实文档中的这个图片和前面描述有些矛盾,按图中时序其实DLU=DS_DCLK+T_DCLK即多沿了一个周期。可能是RX端可以调节LMFC延后一个时钟周期开始,否则时序也太难达到了,还需要PCB步线时强行将DS_DCLK差的比较大才可能实现。

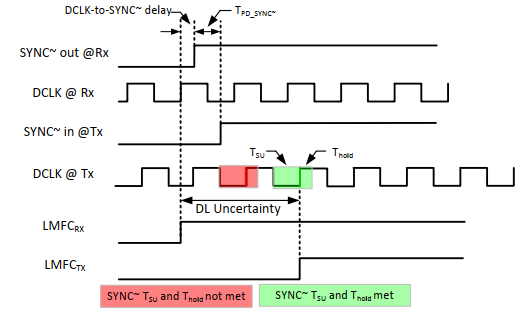

假定DS_DCLK比较小,则上面等式很难达到,无法满足建立时间。所以如果是这种差一些的情况还会比上边情况再错开1个device clock,此时DLU计算如下,下图中可以看到LMFC开始又晚了一个周期。

DLU=DS_DCLK=T_CLKtoSYNC+T_PDSYNC+T_SU+T_DCLK

对比总结

Subclass0不需要考虑确定性延时,实现比较简单。对于多转换器同步的场景可以通过在数据中添加时间戳来实现数据对齐,例如AD9625和AD9680就支持相应功能。

Subclass1在考虑确定性延时的同时可以达到很高的device clock时钟频率,适用于采样速率很高的场景,当然同样适用于低采样率。当device clock低于500M时不使用额外的相位调节等方法也比较容易满足时序。

Subclass2同样适用于device clock低于500M的场景,相比之下优势是可以节省IO,每个转换器或设备省了一个SYSREF接口。

参考资料

ADI Technical Article MS-2677:JESD204B Subclasses (Part 2): Subclass 1 vs. Subclass 2 System Considerations