理解PC-CFR之前,必须先了解它要解决的核心问题:高峰均比。

-

峰均比:指一个信号在特定时间段内,其峰值功率与平均功率的比值。

-

峰值功率:信号瞬间能达到的最高功率。

-

平均功率:信号长时间的平均功率水平。

-

PC-CFR 的全称是 峰值对消峰均比降低。它是一种非常经典且有效的CFR算法。

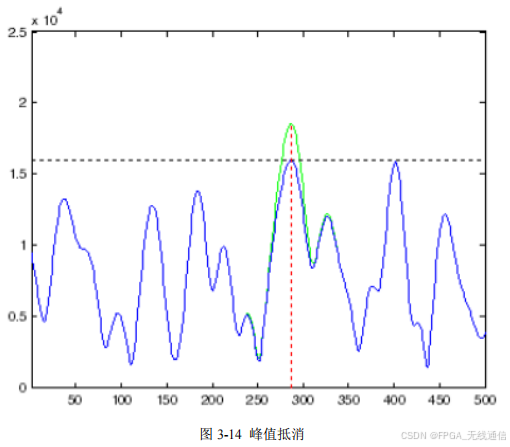

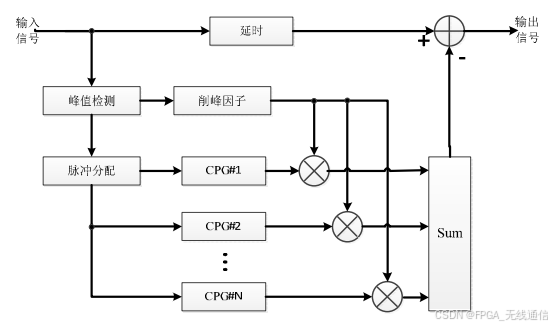

它的核心思想非常直观:"削掉"信号中过高的峰值,并立即生成一个与这些峰值形状相反、相位相同的"对消脉冲",将其从原始信号中减去,从而平滑掉峰值,而不是简单粗暴地硬砍。

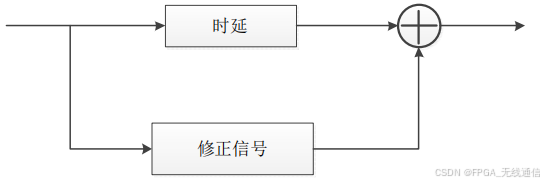

波峰因子降低CFR是基于在原始信号的基础上减去一个修正信号的原理实现;

修正信号就是原始信号经过限幅后再经过滤波的信号,也就是在限幅门限以上的信号是经过了噪声成型滤波器滤波的。

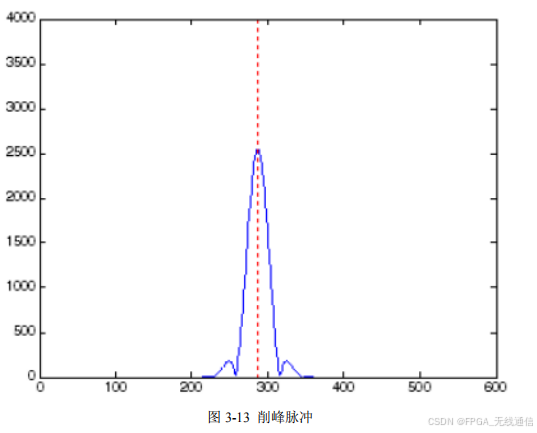

在峰值对消CFR算法中,修正信号就是一些独立的对消脉冲的和,这些独立的对消脉冲由寻找到的信号峰值产生,每一个脉冲就是与信号频谱相匹配的滤波器的冲击响应;

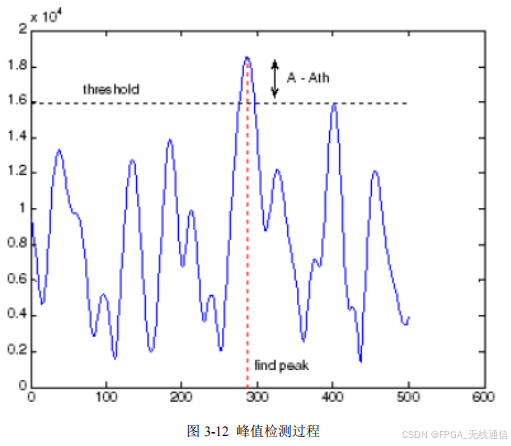

峰值检测过程就是对输入信号寻找超出门限值的信号峰值,计算出幅度超过门限值的部分(A-Ath);

抵消脉冲是单位幅度信号的冲击响应乘以(A-Ath)x e^θ, θ为相位;

也就是说,抵消脉冲是由峰值信号幅度超出削峰门限部分与相位共同决定的;因为信号是复信号,每个抵消脉冲必须旋转到与相应峰值信号相匹配的相位。当原始信号减去抵消脉冲,则将峰值信号的幅度降低到门限值,同时保持了信号的相位不变。

对于PC-CFR算法来说,只要设定适当的门限值,生成对应的削峰脉冲,就可以将原始信号的峰值抑制到门限值以内,并且由于削峰脉冲的频谱和原始信号的频谱是一致的,因此不会带来带外泄露;

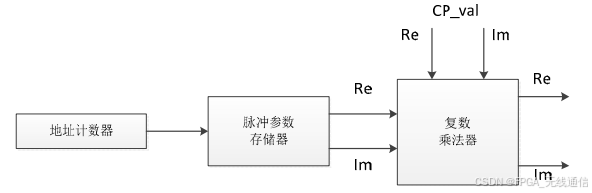

在硬件上,抵消脉冲是抵消脉冲生成器产生的,在抵消脉冲生成器中,地址计数器必须在适当的时间触发以放出脉冲,同时复数乘法器需要正确的输入因子;

注意:一个特定的信号,并不是经过一次削峰过程就能够将所有的峰值都消除掉,一般需要进行多次迭代;

PC-CFR原理图

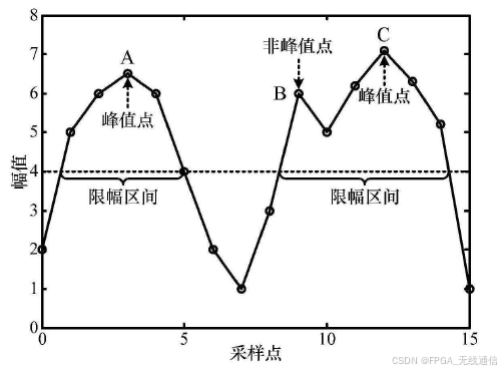

1)峰值检测

目的是在一个区间内鉴别出超出CFR门限值并且幅度最大的采样点,这些门限值是通过寄存器输入;

峰值检测方法:

-

判断采样点与相邻样点的幅度大小,如果采样点幅度大于相邻样点,且超过了设定的门限值,那么该采样点就是峰值;

-

在一个门限区间内寻找最大值作为峰值;门限区间的定义是,如果信号幅度曲线与限幅门限相交于两个点x1和x2,x1、x2之间的采样点幅度均大于门限值,则[x1,x2]称为一个门限区间;

2)峰值因子

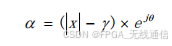

峰值因子为抵消脉冲生成复数因子,用来修正削峰脉冲;算法在实现过程中的峰值缩放是采用的复数缩放,为了缩放后不影响信号的相位,必须使抵消脉冲的相位与信号的相位一致,因此将峰值因子用于每个峰值的削峰脉冲系数,使抵消脉冲的幅度和相位满足要求。

该模块将峰值检测模块获得的信号幅度和相位作为输入,信号峰值与门限值的差就是缩放的幅度,信号峰值的相位就是峰值因子的相位。

α 是峰值因子,γ 是削峰门限值, θ是峰值信号的相位,|x|是信号峰值的幅度;

3) 脉冲分配器

进行削峰运算时,CPG资源的分配主要靠脉冲分配器来完成。系统最开始时,所有的CPG均处于闲置状态,当检测到第1个峰值信号到来时,脉冲分配器分配第一个闲置的CPG,用于削峰处理,同时把CPG标识为占用状态,直到削峰周期结束;然后系统继续检测下1个峰值信号,并为下一个峰值信号分配剩下的闲置的CPG;一直到所有闲置的CPG分配结束,如果还有峰值信号到来,那么就需要进行下一次迭代来进行削峰处理;

如果输入信号的峰值过于密集,则需要一个分配器间距参数来缓减这类情况,如果信号峰值的距离小于分配间距参数,那么脉冲分配器将不会分配CPG,当前峰值不会被处理;

4)抵消脉冲发生器

主要目的是产生抵消脉冲用于削峰处理,设计抵消脉冲其实就是设计一个滤波器,抵消脉冲的系数通过滤波器的设计方法得到,占据的带宽与输入信号相同,设计好的系数放置在预先准备好的存储器中,根据系统不同的带宽配置,可以设计多组抵消脉冲的系数,统一放置在存储器中,在使用时,通过简单的选择器找到合适的系数来产生抵消脉冲。