FPGA教程系列-番外篇Model Composer之HDL滤波器仿真

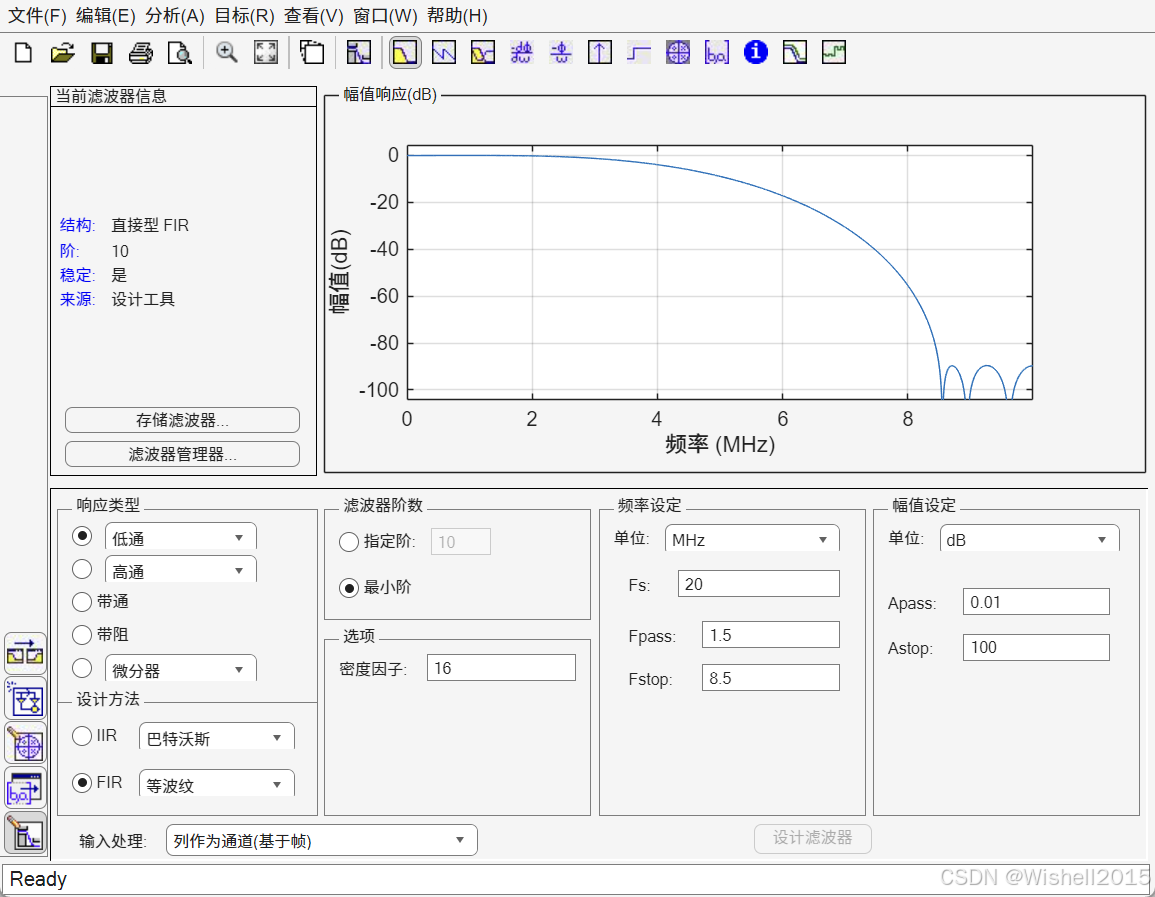

采用Simulink对滤波器进行仿真以后,可以添加HDL模块了

添加模块

1、从 AMD 工具箱 > HDL > 工具,选择 FDATool 并将其添加到设计中。

2、展开 AMD 工具箱 > HDL 菜单,选择 DSP、Non AXI-S,然后选择数字 FIR 滤波器。

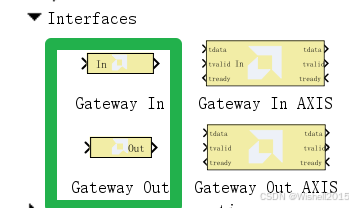

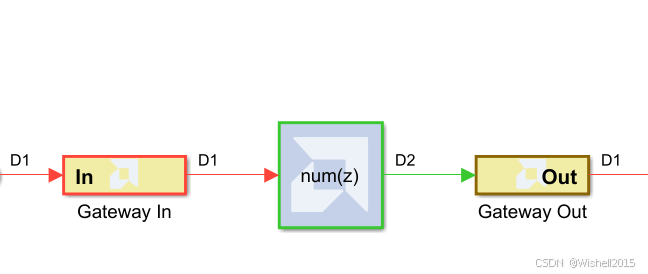

3、在接口菜单中选择网关输入和输出,并将其添加到设计中。

4、从 Utilites 菜单的代码生成菜单下,将 Vitis Model Composer Hub 块(用于定义 FPGA 技术)添加到 Simulink 设计中。

设置HDL模块

1、定义滤波器系数,与仿真一致

2、在 "滤波参数 "部分,用 xlfda_numerator( [bdroot, '/FDATool']) 代替现有系数(系数向量),以使用模型顶层的 FDATool 实例所定义的系数(这也是使用 MATLAB "bdroot "命令的原因)。

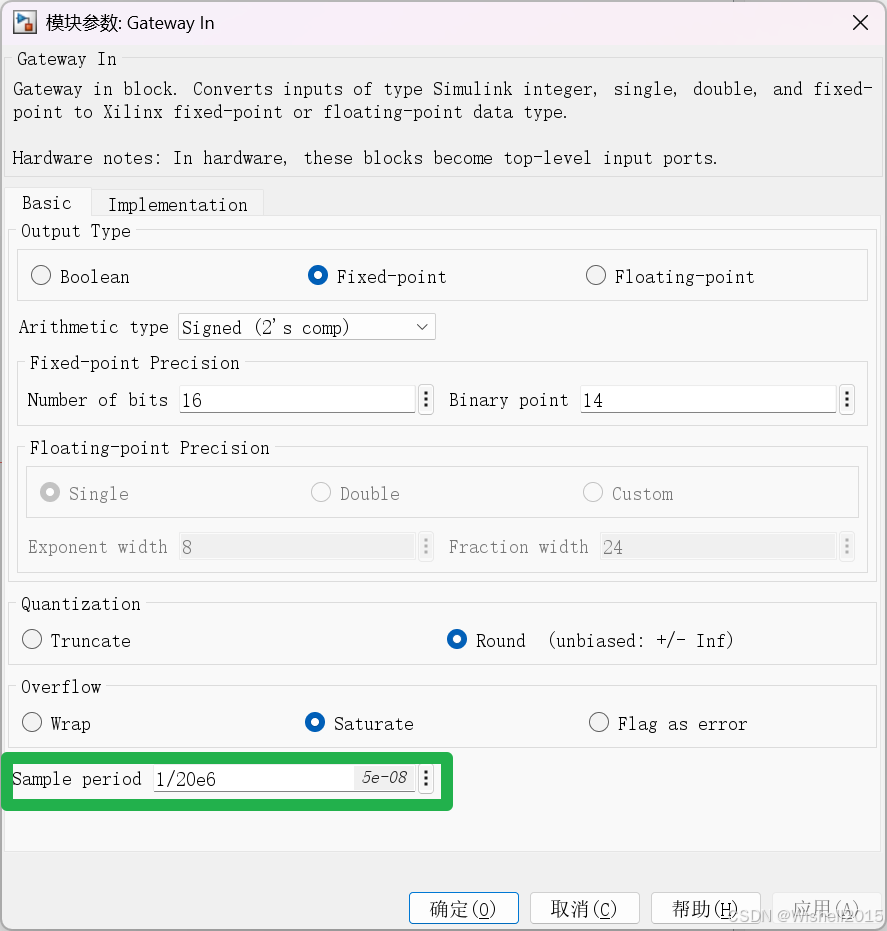

3、设置Gateway in参数

标准 Simulink 环境中使用的连续时间与 FPGA 硬件环境中的离散时间之间的转换是通过定义 Gateway In 块的采样率来确定的。这决定了连续输入波形的采样频率。Vitis Model Composer 会自动将此采样率传递给设计中的其他模块。同样,用于表示数据的位数也在网关输入模块中定义,并在系统中传播。

4、创建子系统

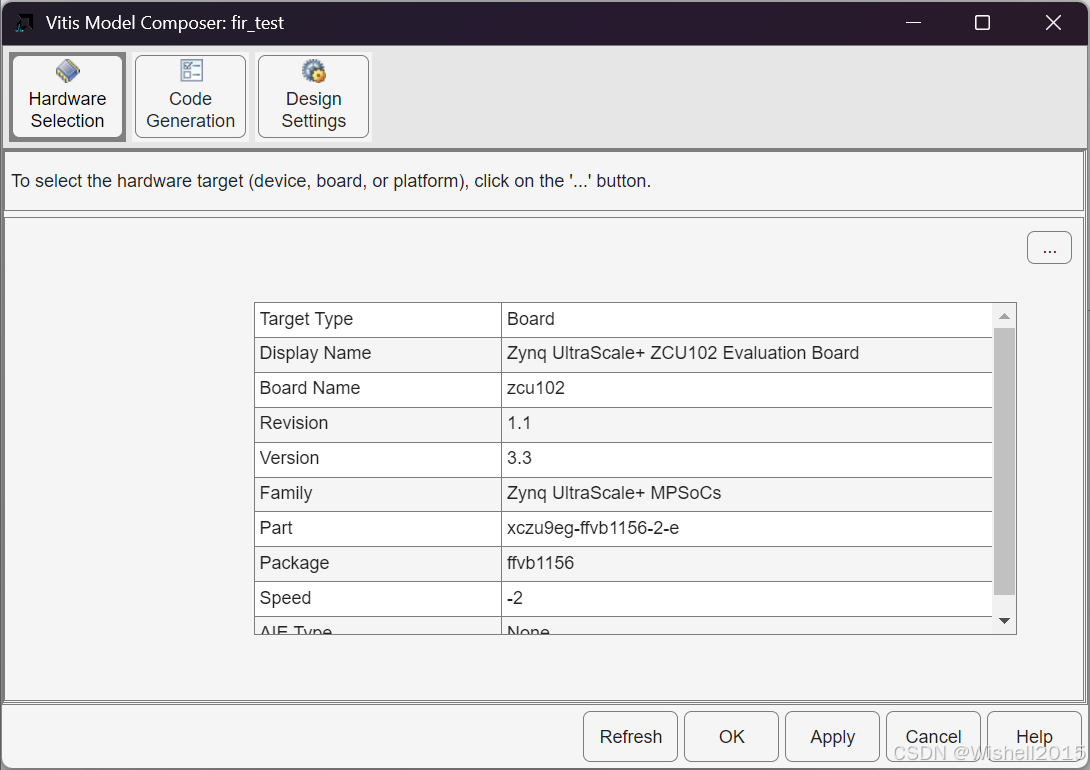

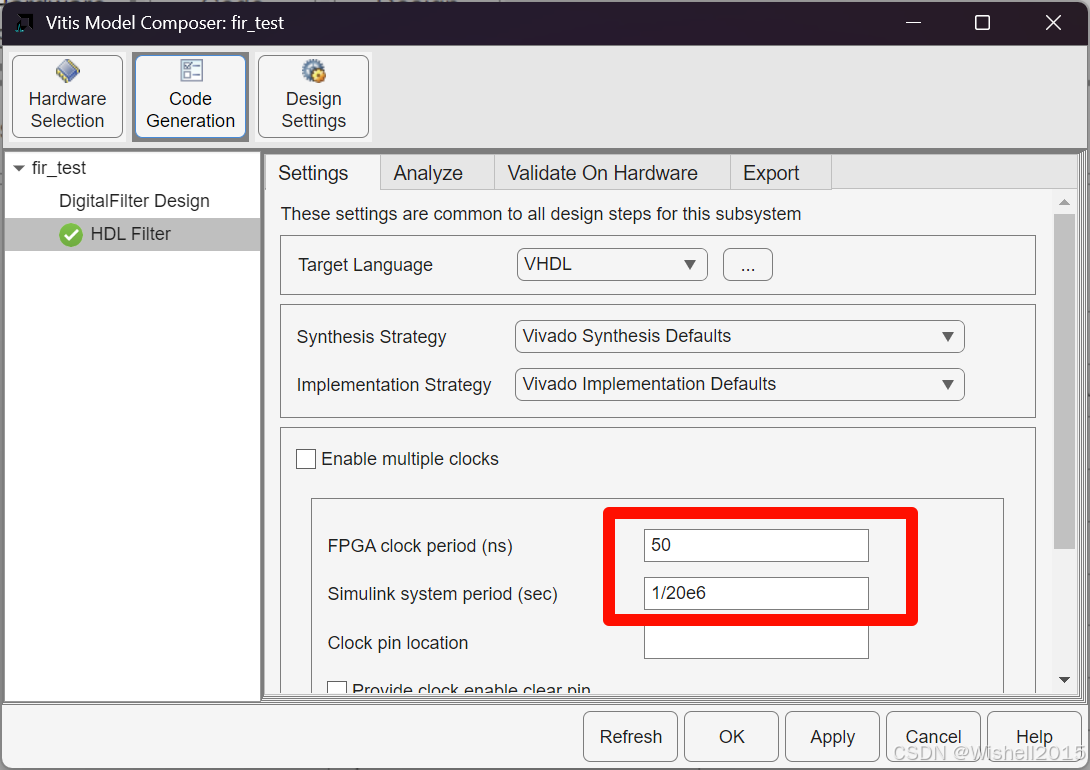

5、设置Vitis Model Composer Hub

由于输入端口的采样频率为 20 MHz,因此必须将 FPGA 的时钟频率和 Simulink 的采样周期定义为至少 20 MHz。

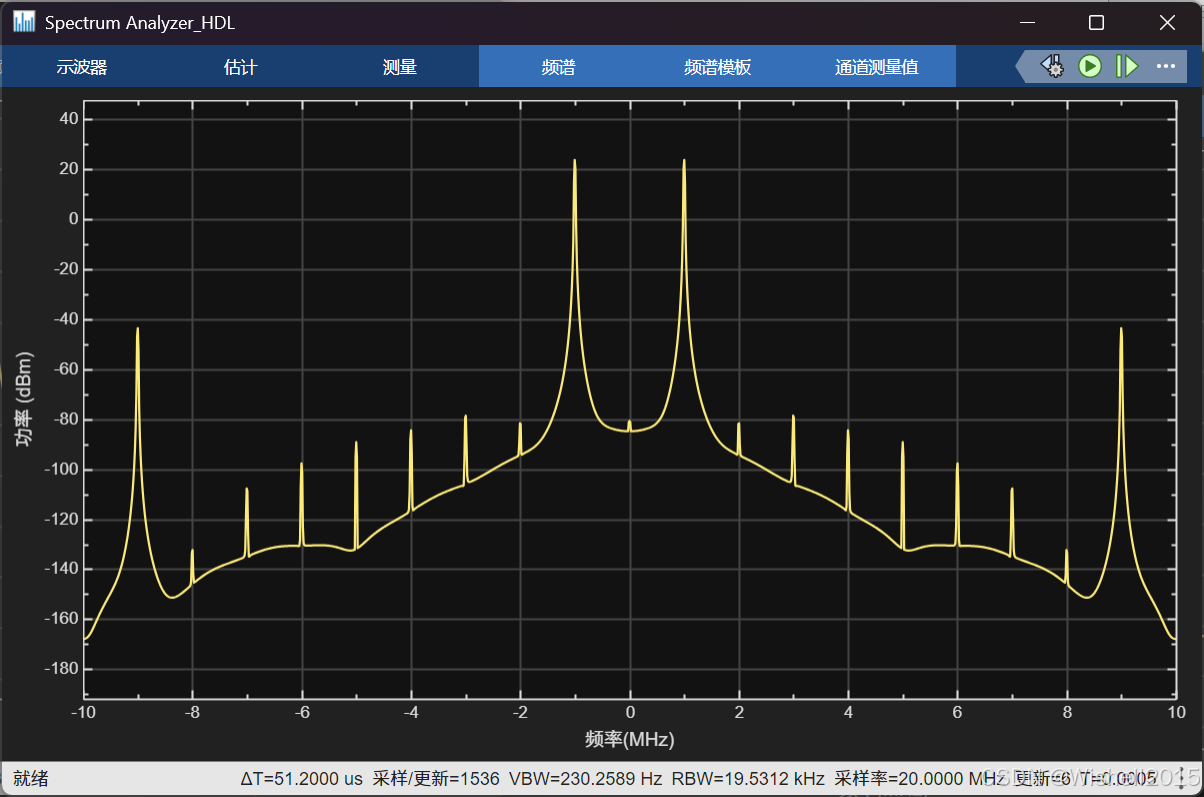

仿真

结果显示频谱分析仪 HDL 窗口与原始设计略有不同。这是由于用离散时间硬件描述连续时间系统时固有的量化和采样效应造成的。

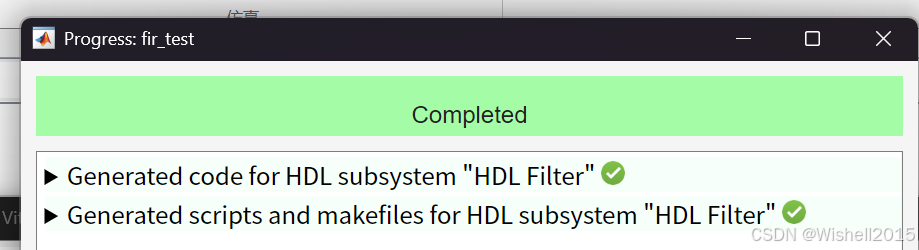

最后一步是在硬件中实现这一设计。这一过程将把网关输入和网关输出模块之间的所有内容综合为硬件描述。该设计描述将以 Verilog 或 VHDL 硬件描述语言 (HDL) 的形式输出。此过程由 Vitis Model Composer Hub 控制。

创建IP核

在 Model Composer Hub 块中,选择 "导出 "选项卡。确保导出类型设置为 IP 目录。这将确保输出为 IP 目录格式。此外,请使用默认的硬件描述语言 VHDL。