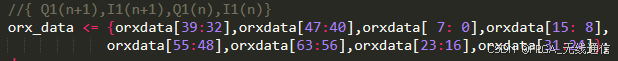

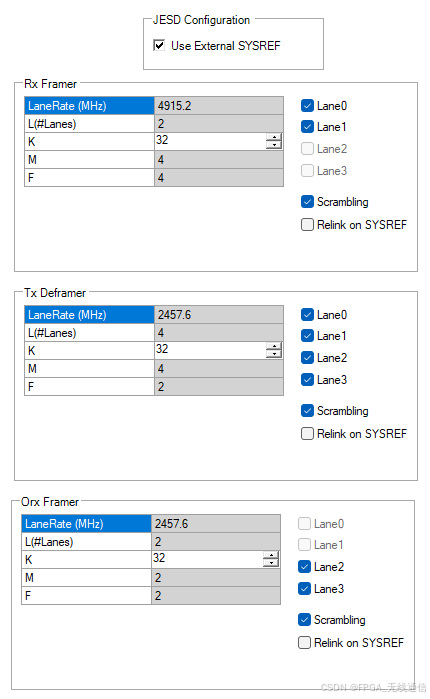

AD9371属于零中频架构,接收侧直接通过本振下边到零频(基带);

接收器带宽(并非射频前端的模拟带宽):7.5MHz 至 100MHz;

带宽的定义:从数据接口侧,能完整的解析或者解调频谱的范围;

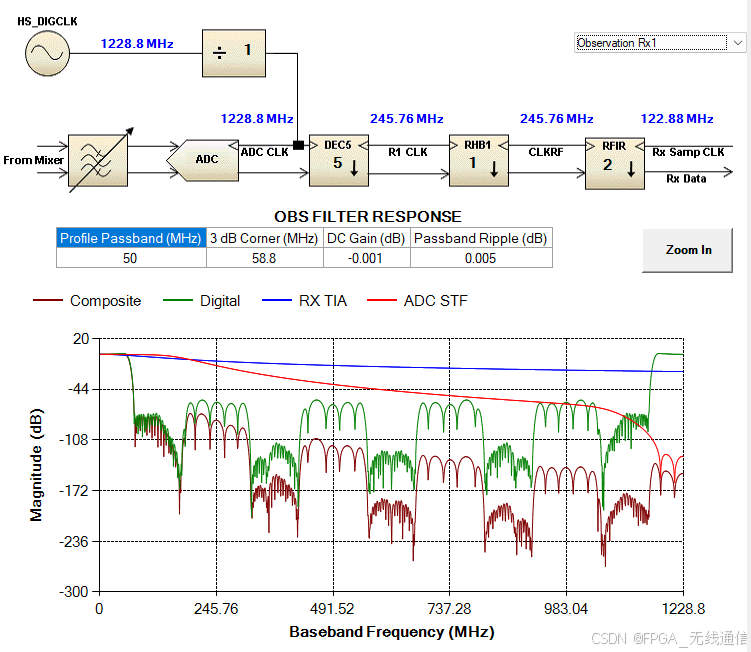

ORX 属于观察通道,用于TX发射的相关指标校正,PA线性度的调整(DPD);

AD9371接收侧有4个Lane是204B的接口,两个Lane用于RX,两个Lane用于ORX;

AD9371发送侧则是4个Lane用于TX;

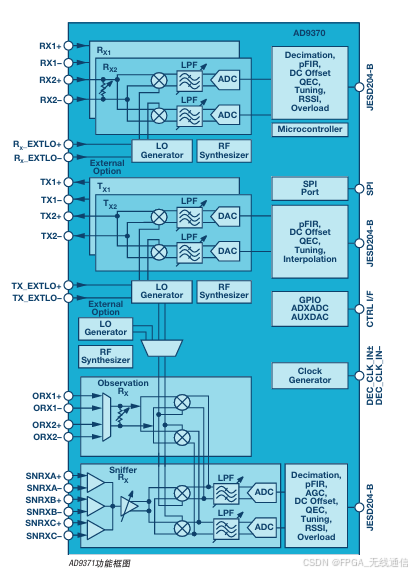

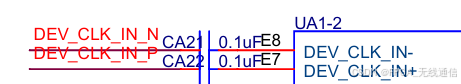

时钟是只需要提供一路device clock 即可;经device clock就能够产生采样时钟等;

时钟芯片给AD9371提供 sysref 和 device clock;

时钟芯片同时给AD9371和FPGA提供SYSREF;

根据AD9371的数据手册和典型应用,可以明确两点:AD9371内部包含处理SYSREF信号的电路,但它通常被设计为接收外部SYSREF,而不是作为主要来源向FPGA提供。

在实际系统设计中,由专用时钟芯片(如AD9528)同时向FPGA和AD9371提供SYSREF信号,才是确保JESD204B链路稳定工作的标准且推荐做法

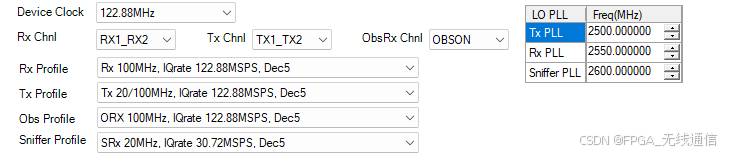

AD9371的软件设置

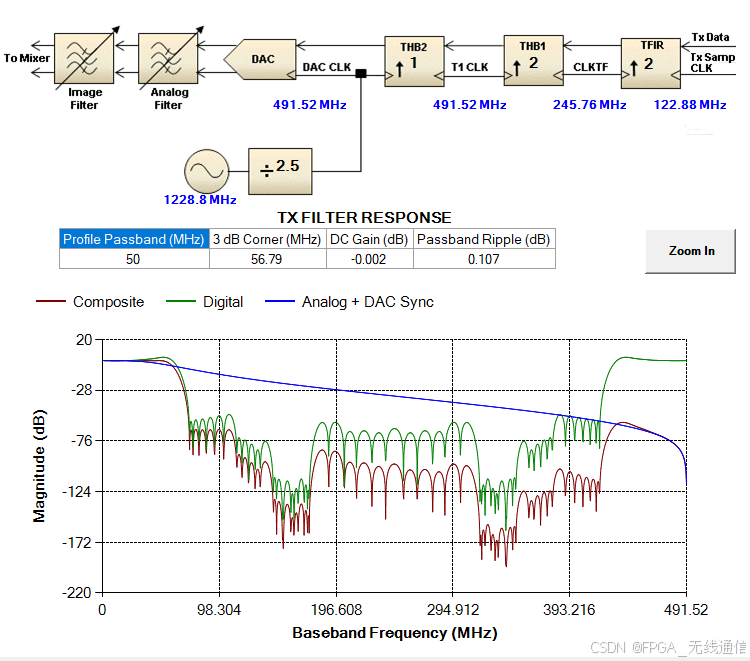

设置采样率和通道使能:

设置校准方案:

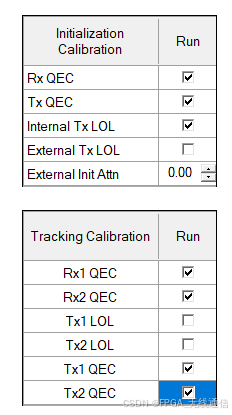

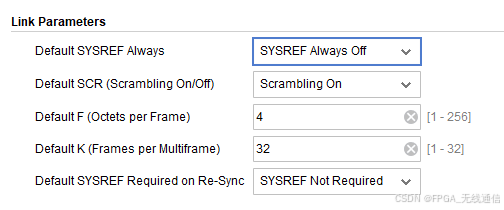

204B接口使能方案:

RX通道:

TX通道:

ORX通道:

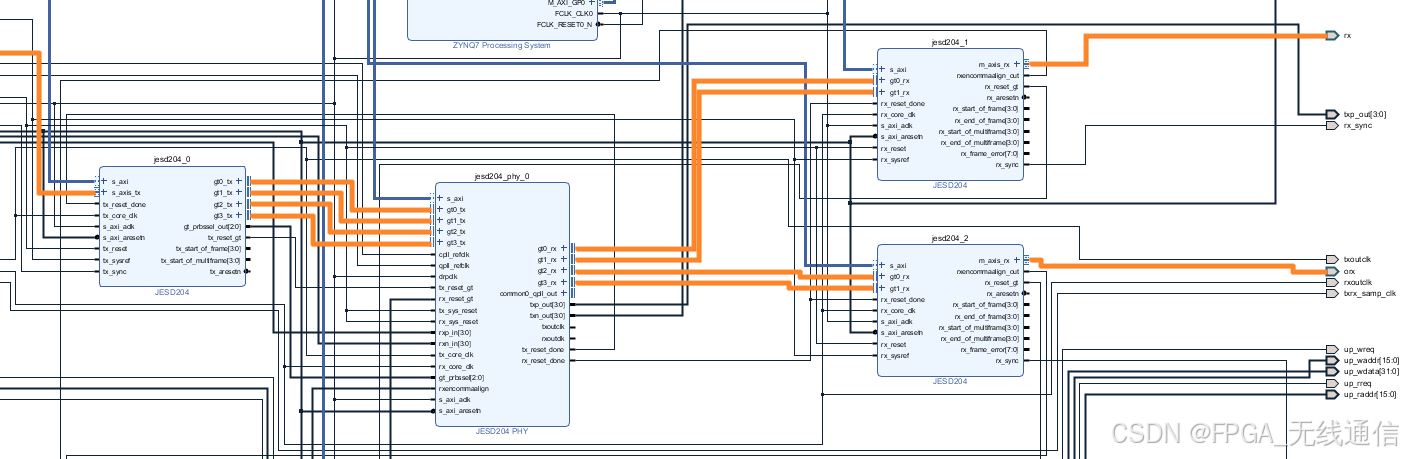

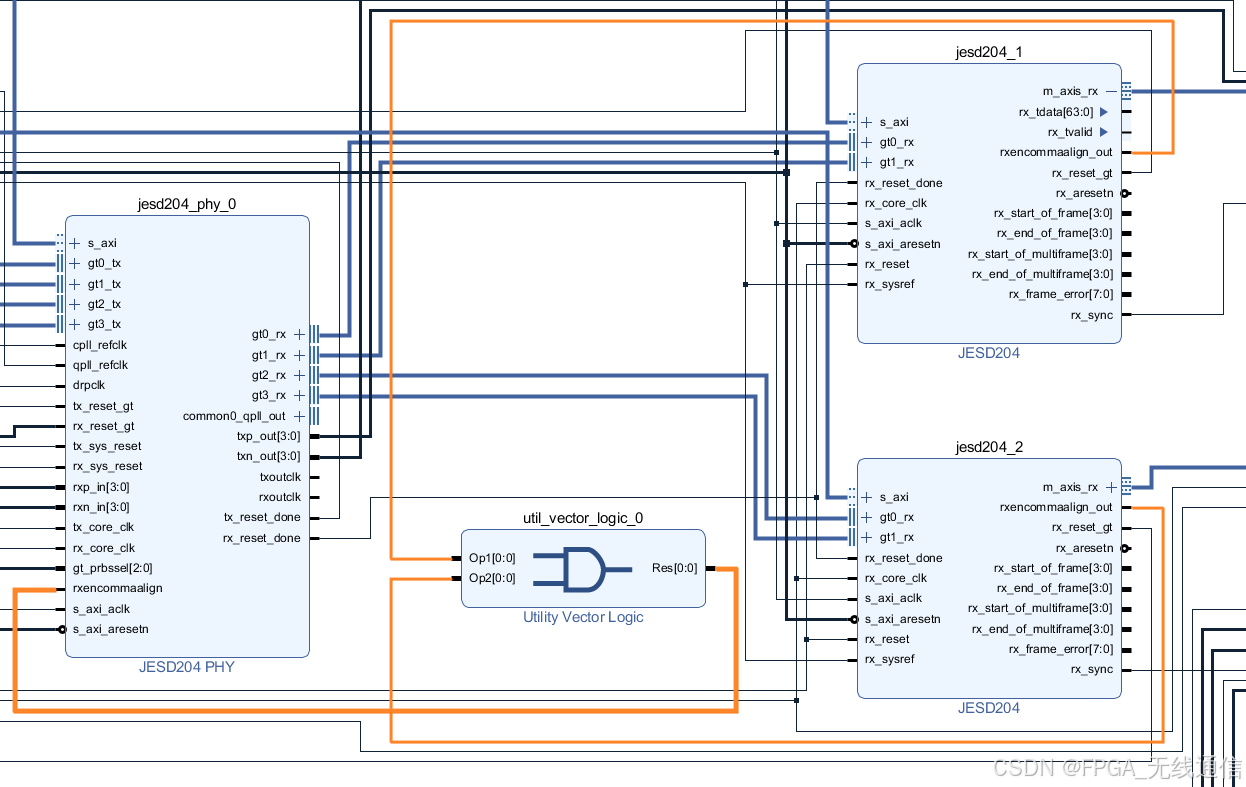

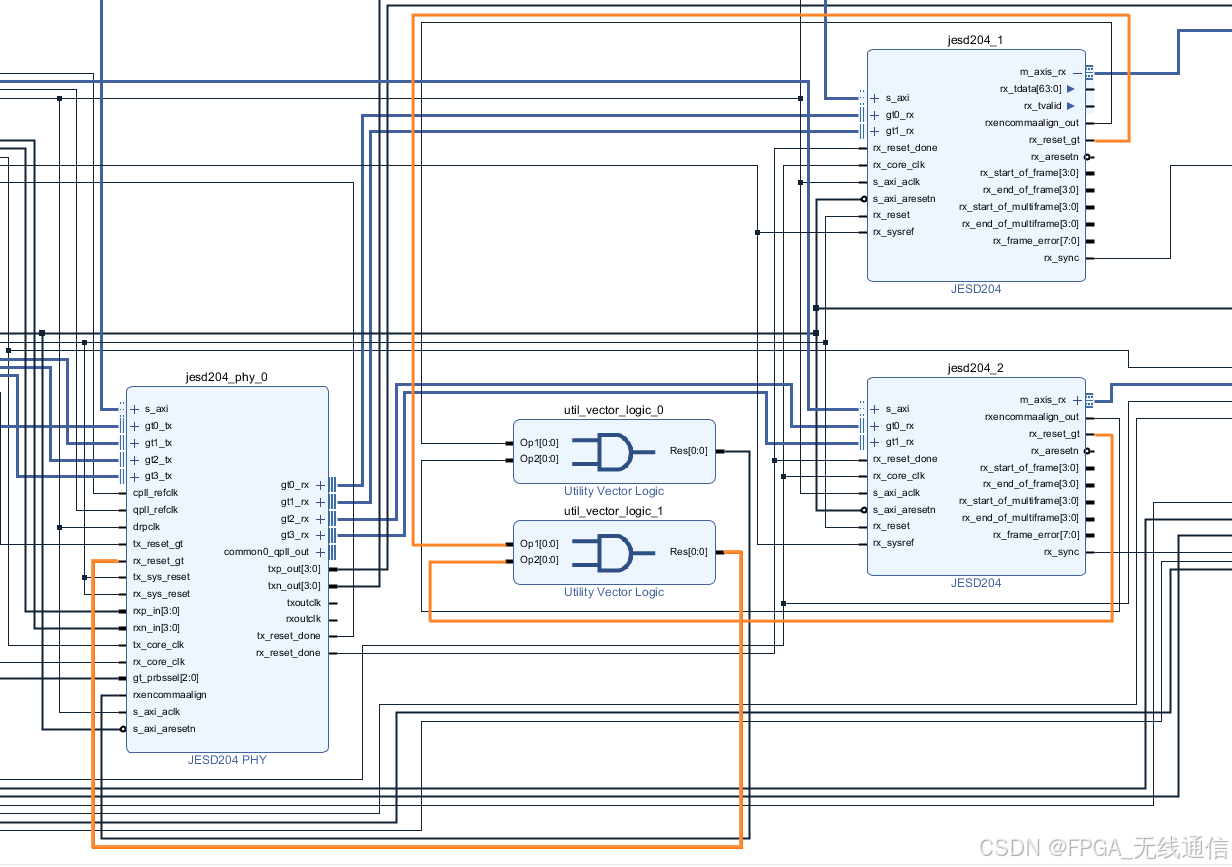

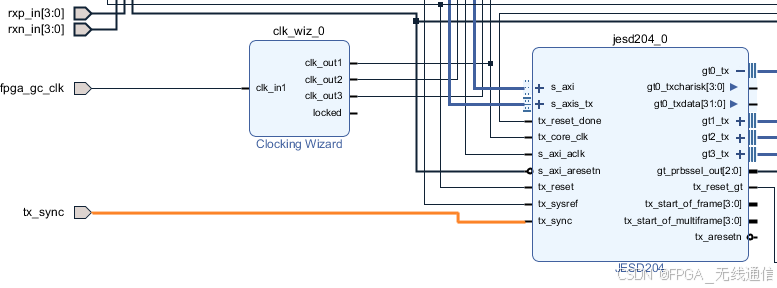

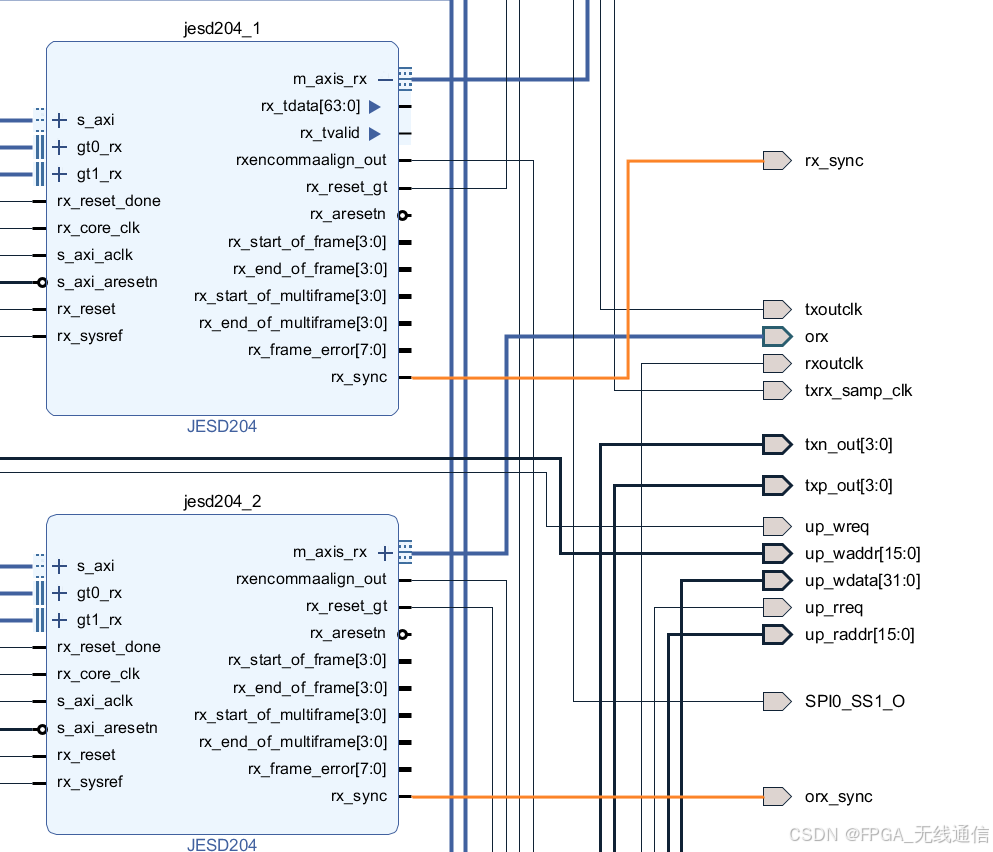

FPGA Block Design IP设置:

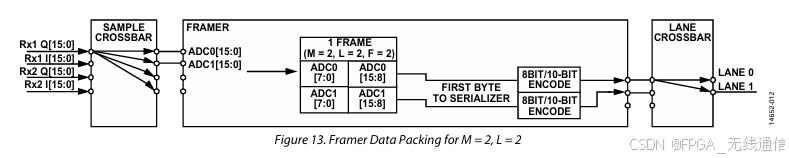

ORX和TX :F=2;

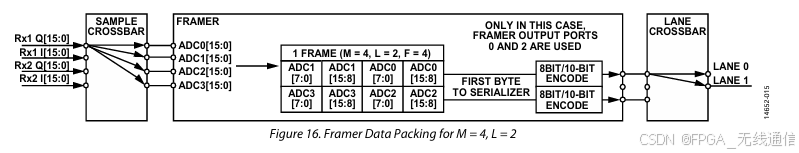

RX:F=4;

2个Lnae给RX ,2个Lane给ORX;

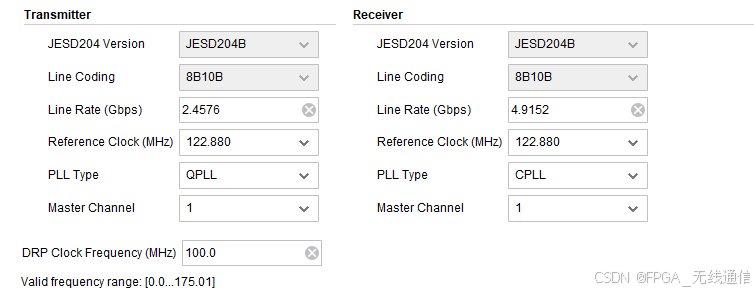

RX的线速率计算:(M*122.88*16/0.8)/L = 4915.2Mbps,M=4;L=2;

ORX的线速率计算:(M*122.88*16/0.8)/L = 2457.6Mbps,M=2;L=2;

链路时钟为122.88M;

TX侧需要一个时钟周期送进入两个采样点,所以TX侧时钟为61.44Mhz;

如果要把数据恢复到122.88M,可以增加一个FIFO进行时钟域变换,由61.44M变为122.88M;

RX和ORX为122.88M;

BD:

字符对齐:

复位:

此处的tx_sync 由ad9371送进来,

由高速接口给AD9371,因为接收serdes方需要提供sync,所以ad9371会输出tx_sync给到FPGA的204b的 TX端;

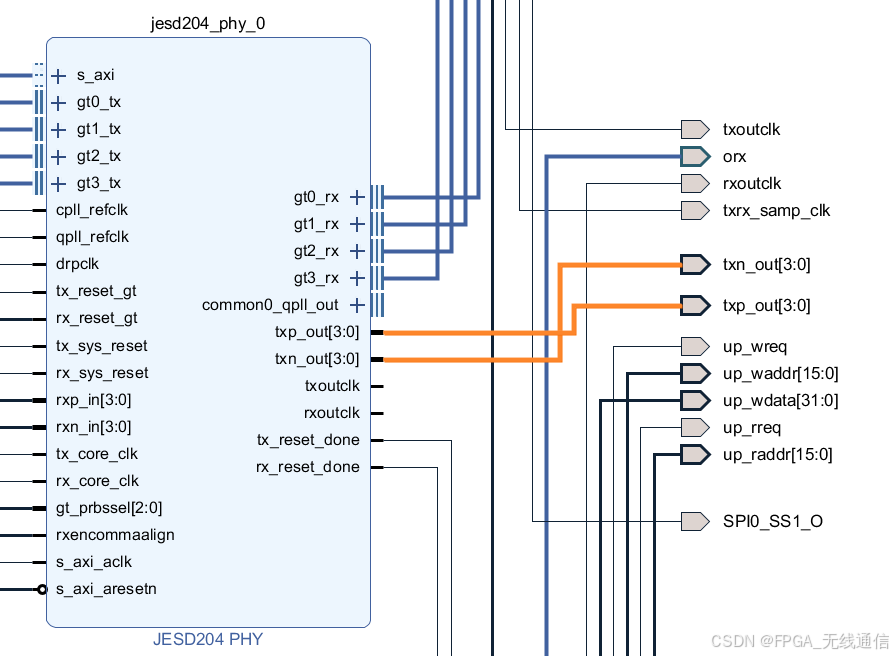

输出 rx_sync 和orx_sync 给到ad9371:

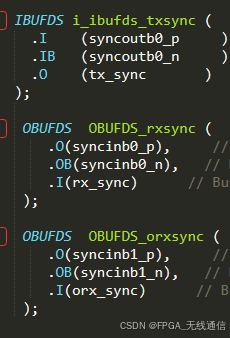

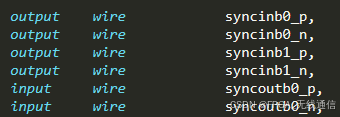

利用 IBUFDS,OBUFDS进行差分信号与单端信号转换;

通过顶层给出到ad9371,或者由ad9371给进来:

Jesd204b phy IP 的配置:4.9152G对应参考时钟输出122.88M;

由于ad9371中204b接口orx配置为2457.6M,对应时钟频率应该是61.44M,此部分就需要去初始化单独的线速率,因为IP只能配置整体4个Lane的线速率,配置ORX就只能在软件侧通过AXI接口去配置ORX的两个Lane;

RX部分的Framer映射Lane0 和 Lane1;

FramerADC_Xbar = 0xB1;指图16从Rx 通过sample crossbar 映射到framer ADC;

高速接口的映射 serializerLaneCrossbar = 0x08;对应图16右侧的映射

ORX部分的Frame映射:(ORX线速率为RX的一半)

FramerADC_Xbar = 0xB1;

serializerLaneCrossbar = 0x40;映射到Lane2和Lane3;

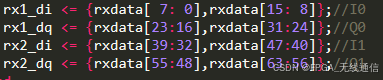

因为xilinx的jesd204b的接收IP 是低字节先输出,那么AD9371是ADCX[15:8]先出来,就需要进行高低字节转换,而jesd204b 接口位宽64位,正好是{Q2,I2,Q1,I1}, 122.88M,两个通道的4个ADC数据;

对于ORX观测通道是在122.88M时钟下输出64位,每个时钟输出两个采样点,

{Q1(n+1),I1(n+1),Q1(n),I1(n)},因为orx只有2个ADC,所以输出数据应该是每隔一个122.88M时钟输出两个采样点。但是ADI为了方便ORX和RX通道相同的线速率,直接将ORX的采样数据进行2倍过采样输出,也就是变成了122.88M*2输出给用户端;需要设置ORX通道的framer的时候进行设置。

映射关系: