通过 UART 实现远程 AXI 访问:让 FPGA 调试更灵活

UART 转 AXI 接口

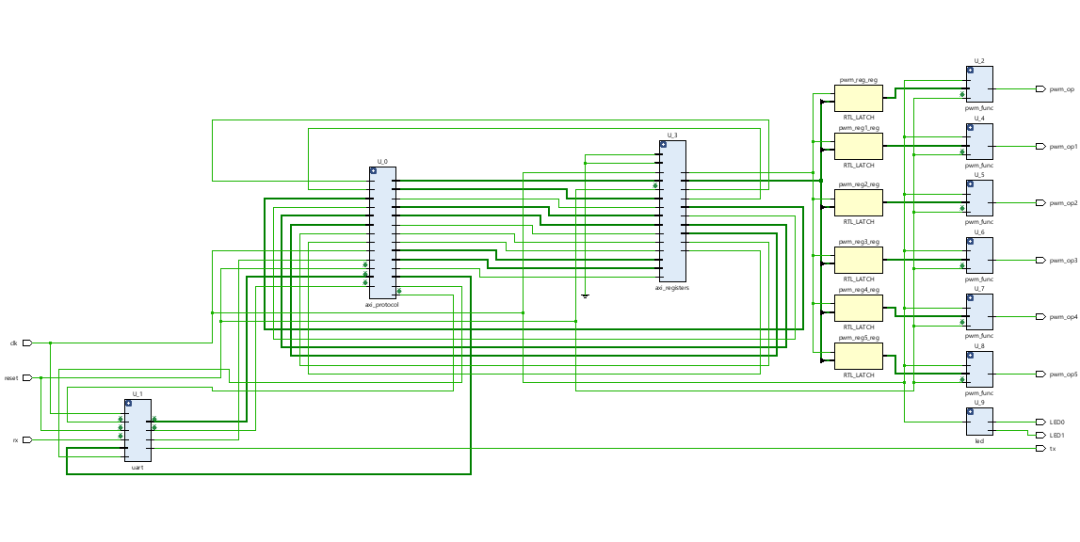

接口完全用 RTL 编写,它允许通过 UART 连接,在 AXI 总线上执行读写操作。

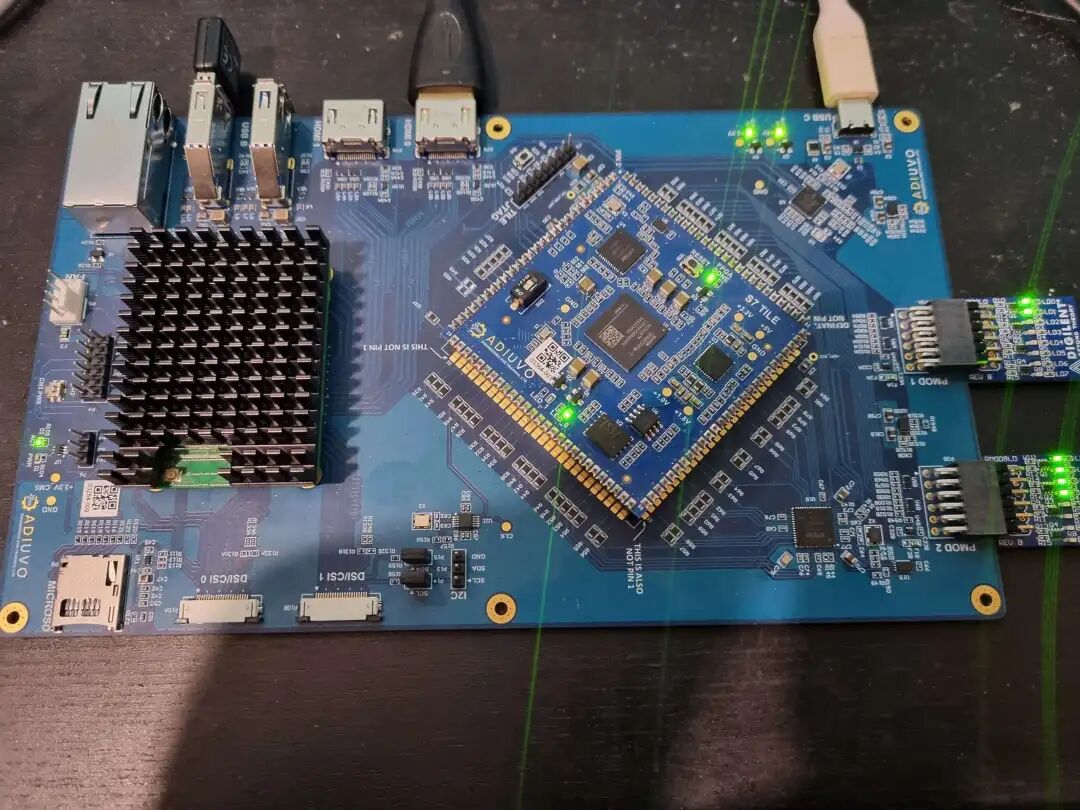

采用这种方式,可以让 FPGA 串口连接到嵌入式板卡的串口上,让后将其放在远程,只需通过网络连接 ------ 例如使用 VS Code + SSH就可以进行调试了。

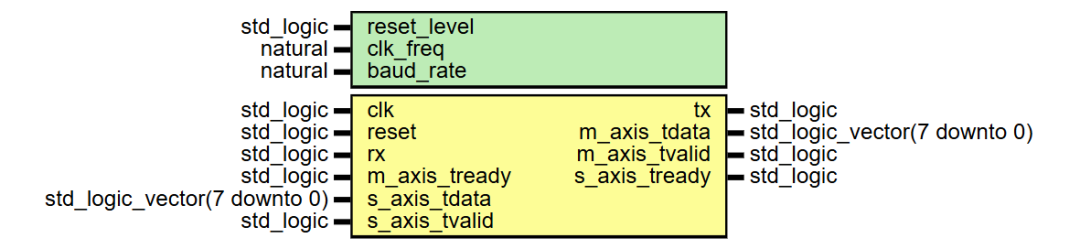

为了实现这一点,先实现一个简单的 UART 模块,该模块对外暴露 AXI-Streaming 接口(input / output),这样就可以方便地向 FPGA 发送和接收数据。

协议转换与 AXI 事务 (AXI Transactions)

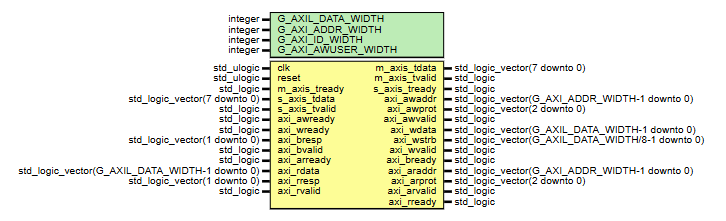

随后,加入一个协议转换模块 (protocol conversion module),它接收通过 AXI Stream 接收到的字节 (bytes),并将其翻译 (translate) 成 AXI 的读或写事务 (read / write transactions)。

因为这些 protocol block 使用的是 AXI-Streaming 接口,所以如果在不同测试环境下需要,也可以很方便地将 UART 替换为其它串行协议 (serial protocol),比如 I²C、SPI 或 QSPI。

接下来我们编写一个DEMO,将 protocol block 的输出连接到 LED。通过串口控制 LED,实现 "呼吸灯 (breathing)" 效果 ------ LED 会按顺序逐渐变亮然后变暗。

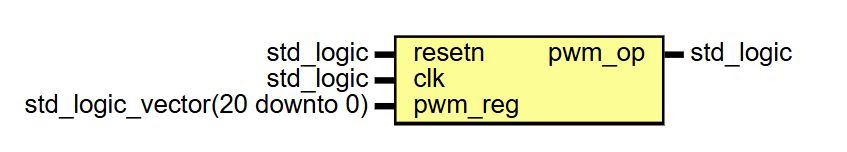

PWM 控制与寄存器接口 (Register Interface)

为了实现"呼吸灯"效果,在 FPGA 设计中实现六个 PWM (pulse-width modulators)。这些 PWM 被连接到 LED,并通过 AXI 寄存器进行控制。

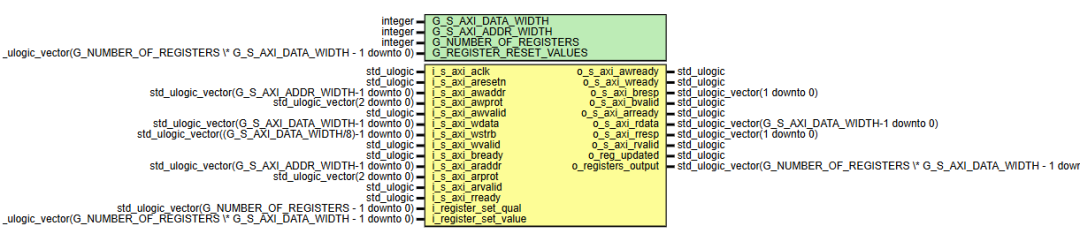

最后实现一个 AXI-to-register 模块,将 AXI 接口映射 (break out) 为一组 32 位寄存器 (32-bit registers)。每个 PWM 都对应一个寄存器,通过向这些寄存器写值 (write) 就可以控制 PWM 的占空比 (duty cycle),从而改变 LED 的亮度。

有了这一机制后,软件端仅需通过一系列寄存器写操作 (register writes),就能动态更新 PWM 占空比,实现想要的 LED 效果。

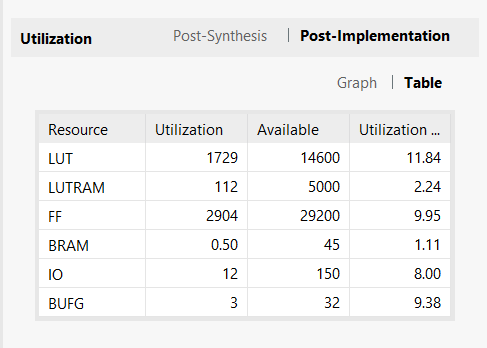

同时,这个设计在资源利用 (resource utilisation) 方面也相当高效 (resource-efficient)。

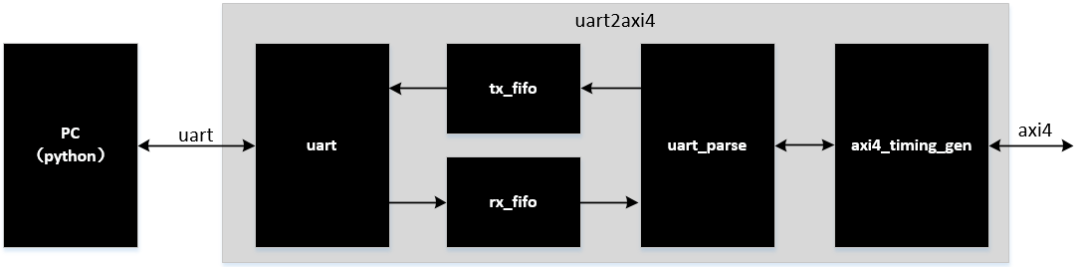

另一种方式

如果觉得上面的方式有点繁琐,可以看下下面的架构:

uart桥接出来的是axi4_full master接口,但是读,写突发长度固定为1,意味着如果写8个字节,就会发起2次突发,由于uart速度本来就慢,所以这种设计也是没有问题的。

数据包格式如下:

write操作

go

write_cmd(0x10) + len(byte为单位,写数据长度) + addr[31:24] + addr[23:16] + addr[15:8] + addr[7:0] + d0[7:0] + d0[15:8] + d0[23:16] + d0[31:24]+ d1[7:0] + d1[15:8] + d1[23:16] + d1[31:24] + ...注:如果len不是4的整数倍,则最后一拍会通过strb的mask操作写入,地址是MSB→LSB,而数据是LSB→ MSB,写操作没有应答包.

read操作

go

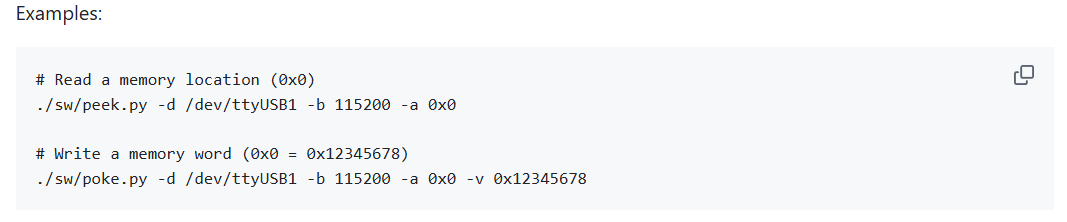

read_cmd(0x11) + len(byte为单位,读数据长度) + addr[31:24] + addr[23:16] + addr[15:8] + addr[7:0]注:返回的数据格式为:d0[7:0] + d0[15:8] + d0[23:16] + d0[31:24] + d1[7:0] + d1[15:8] + d1[23:16] + d1[31:24] + ...该项目还自带了python程序,可以参考项目给的例子程序进行验证,并且可以很方面的进行移植。

这个例程后续我们再整理。

参考代码

第一种架构(VHDL编写):

第二种架构(Verilog编写):

https://github.com/ultraembedded/core_dbg_bridge?tab=readme-ov-file