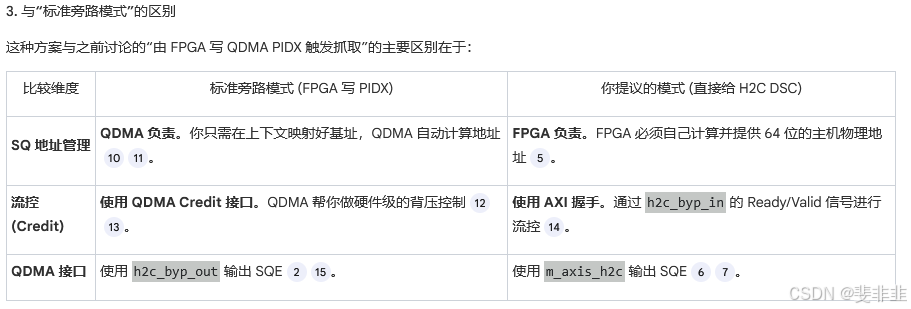

Q:那我直接产生 h2c dsc 给 h2c stream engine ; 让sqe通过_axis_h2c接口发送到fpga; 然后fpga 再通过byp in 给qdma 可以吗?

A:这种方案在技术上是可行的,本质上是你在 FPGA 内部实现了自己的"描述符抓取逻辑",完全绕过了 QDMA 描述符引擎(Descriptor Engine)的自动提取机制。

根据参考资料,以下是对你提议流程的可行性分析和操作细节:

-

方案可行性分析

• 功能支持:QDMA 的 H2C Bypass Input (h2c_byp_in) 接口允许用户逻辑直接向 H2C 引擎注入描述符。这不仅可以用来搬运普通数据,也可以用来搬运像 NVMe SQE 这样的控制信息。

• 引擎角色切换:在这种方案下,你把 QDMA 的 H2C Stream 引擎 当作一个通用的"远程内存读取工具",而不再依赖它的"描述符提取引擎"来自动维护队列索引(PIDX/CIDX)。

-

具体操作流程

如果你直接产生 H2C 描述符,流程将变为:

-

FPGA 自行管理地址:FPGA 逻辑必须知道主机 SQ 在内存中的确切物理基地址,并自行维护一个生产者/使用者索引计数器,以计算下一个待取 SQE 的地址。

-

注入 H2C 描述符:FPGA 通过 dmah2c_byp_in_st * 接口注入一个 16 字节格式的描述符。

◦ addr 指向主机内存中 SQE 的位置。

◦ len 设置为 64 字节。

-

SQE 传输至 FPGA:H2C Stream 引擎执行 PCIe 读取请求。抓取到的 64 字节 SQE 会通过 m_axis_h2c_tdata 接口以 AXI-Stream 报文的形式发送给 FPGA 用户逻辑。

-

后续 C2H 数据触发:FPGA 解析 m_axis_h2c 收到的 SQE。如果判定是 C2H 数据传输请求,FPGA 再通过 c2h_byp_in 接口给 QDMA 发送 C2H 描述符来启动数据搬运。

-

这种方案的优缺点

• 优点:FPGA 拥有绝对的调度权。你可以完全自主决定什么时候、以什么频率去读主机的命令,不需要维护 QDMA 的 PIDX 寄存器。

• 缺点/风险:

◦ 逻辑复杂度增加:FPGA 需要自己处理 SQ 环形缓冲区的卷绕(Wrap-around)逻辑。

◦ 资源占用:你实际上占用了一个 H2C 数据通道来传控制指令,如果 H2C 数据流量很大,读取 SQE 可能会和正常数据搬运发生竞争。

结论: 可以这样做。这是一种高度定制化的实现方式,常见于需要 FPGA 完全自主接管主机内存管理,或者 QDMA 默认的描述符提取机制无法满足特定实时性要求的特殊场景。