一,我们书接上回啊,我们接着对这个报告进行分析整理。

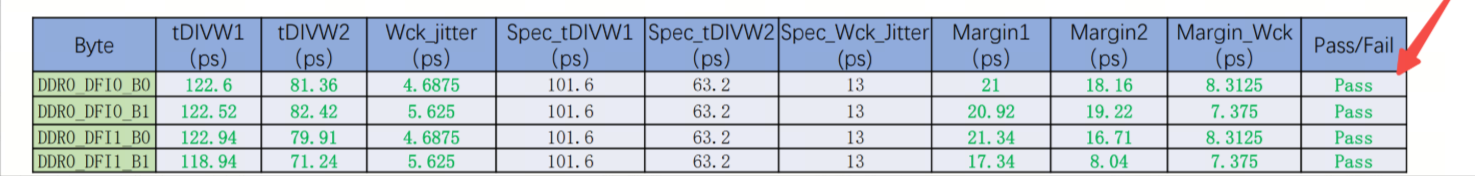

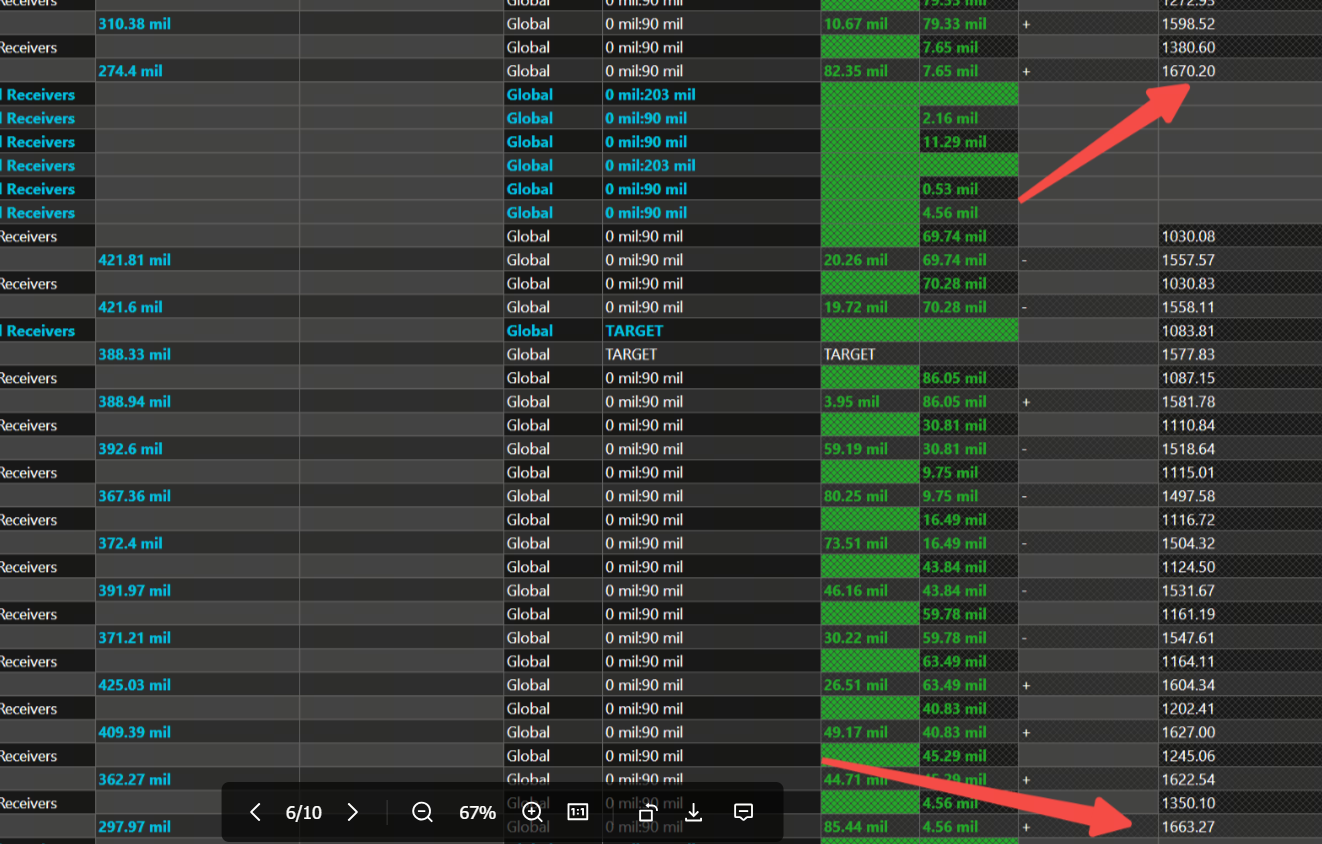

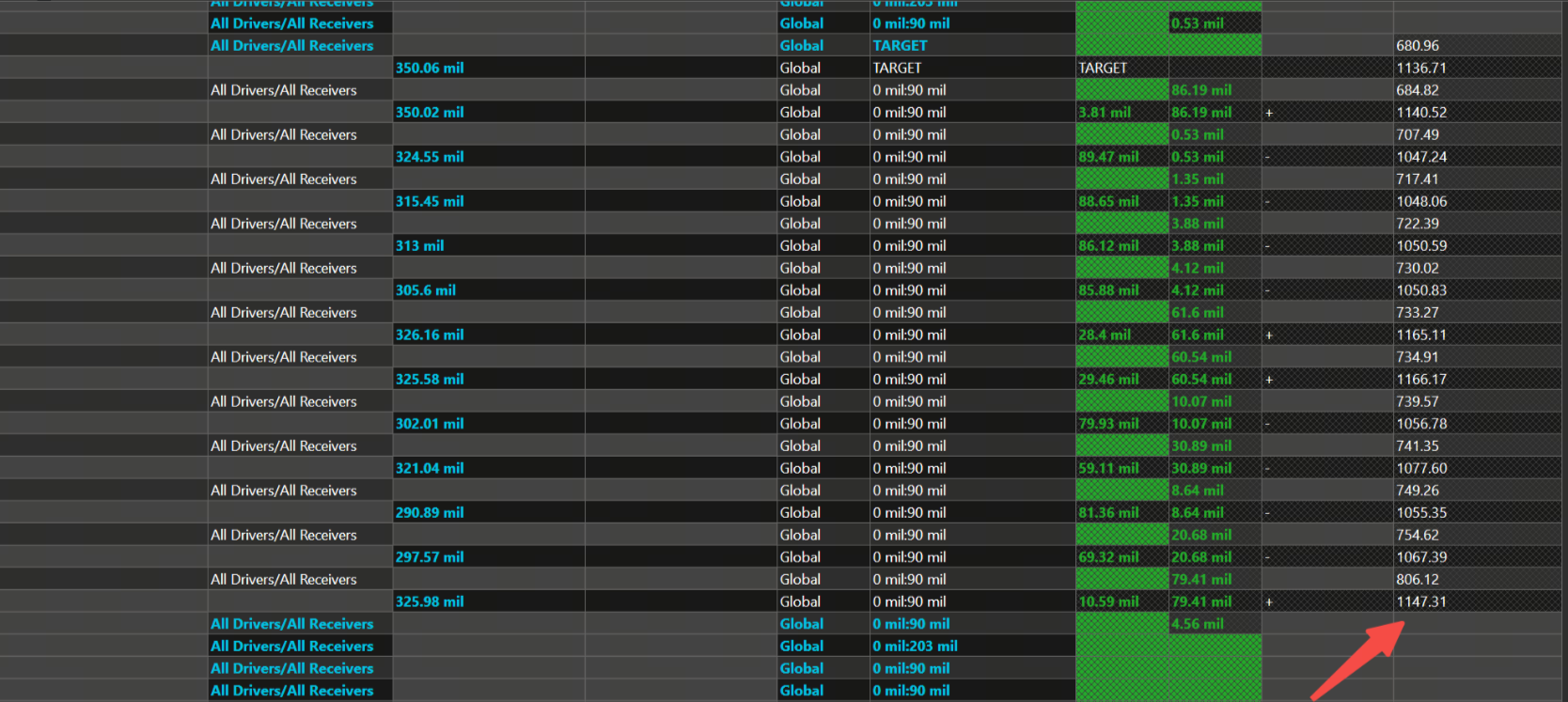

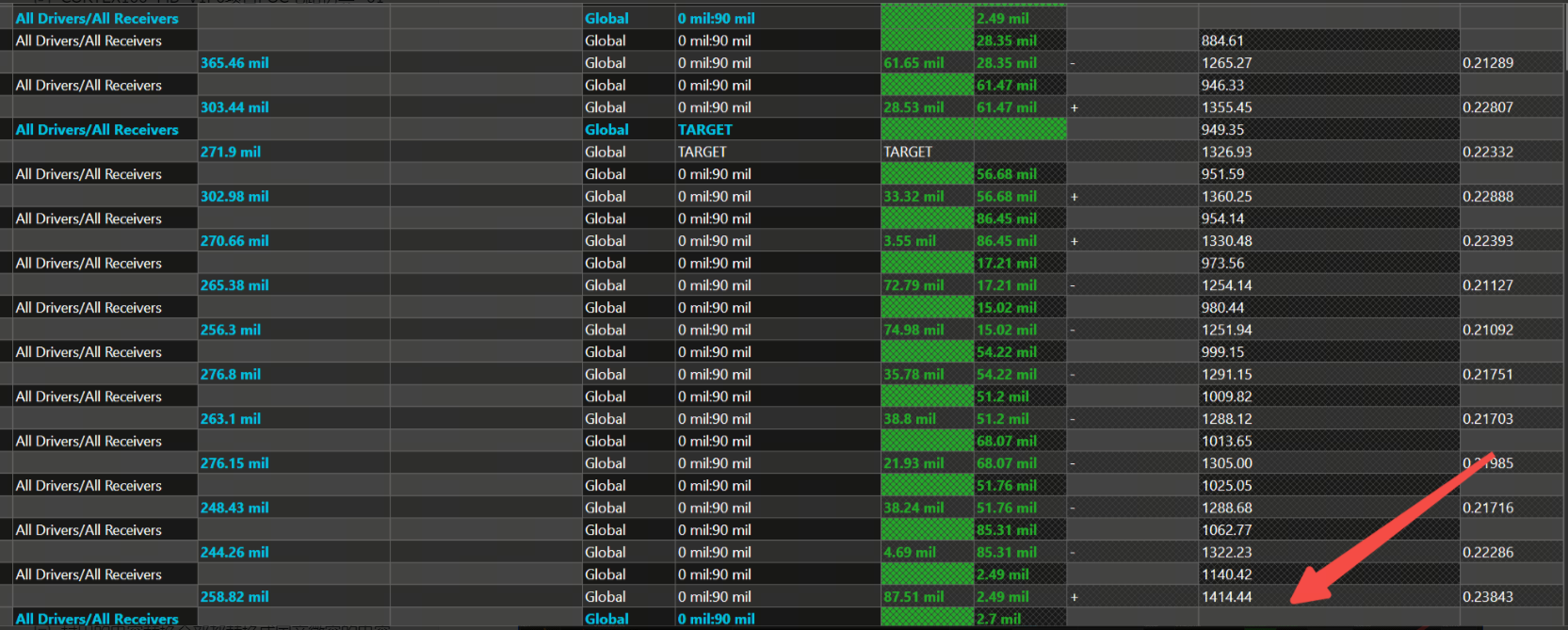

result:DDR0

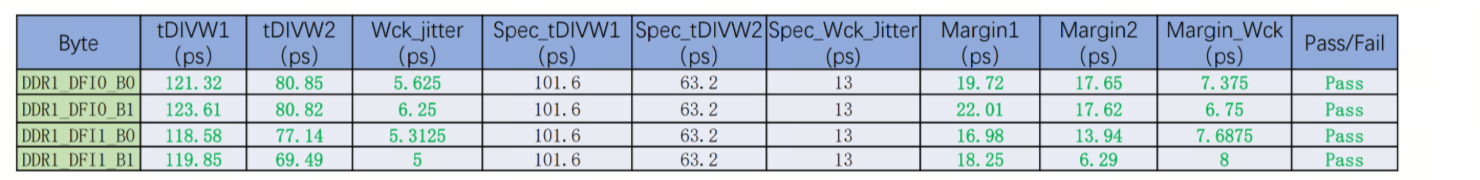

result:DDR1

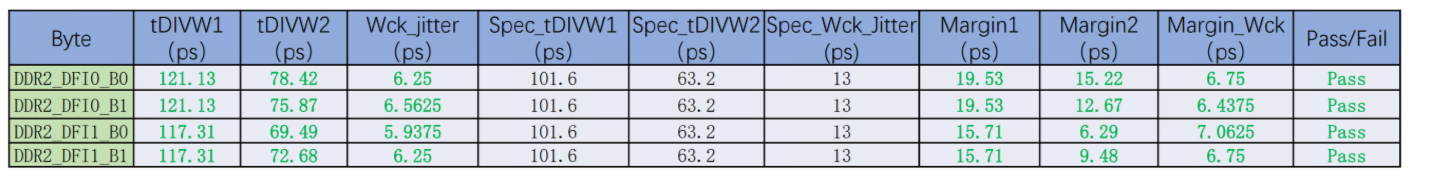

result:DDR2

按照上述仿真的数据可以得知,DDR2_DFI1_B0这组数据在tDIVW1 和 tDIVW2 以及Wck_Jitter数据的Margin相比其他组数据不是很多,是最差的一组,DDR0_DFI0_B0是最好的一组。

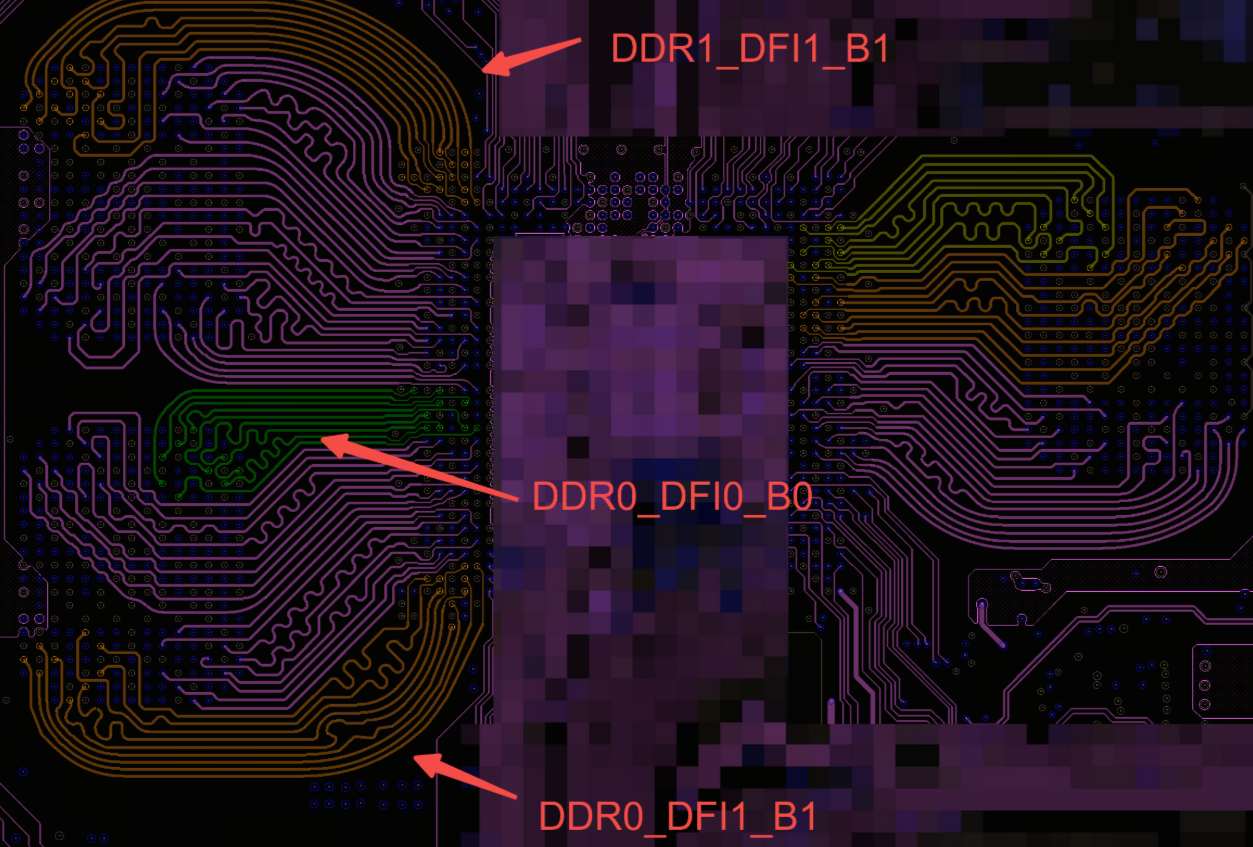

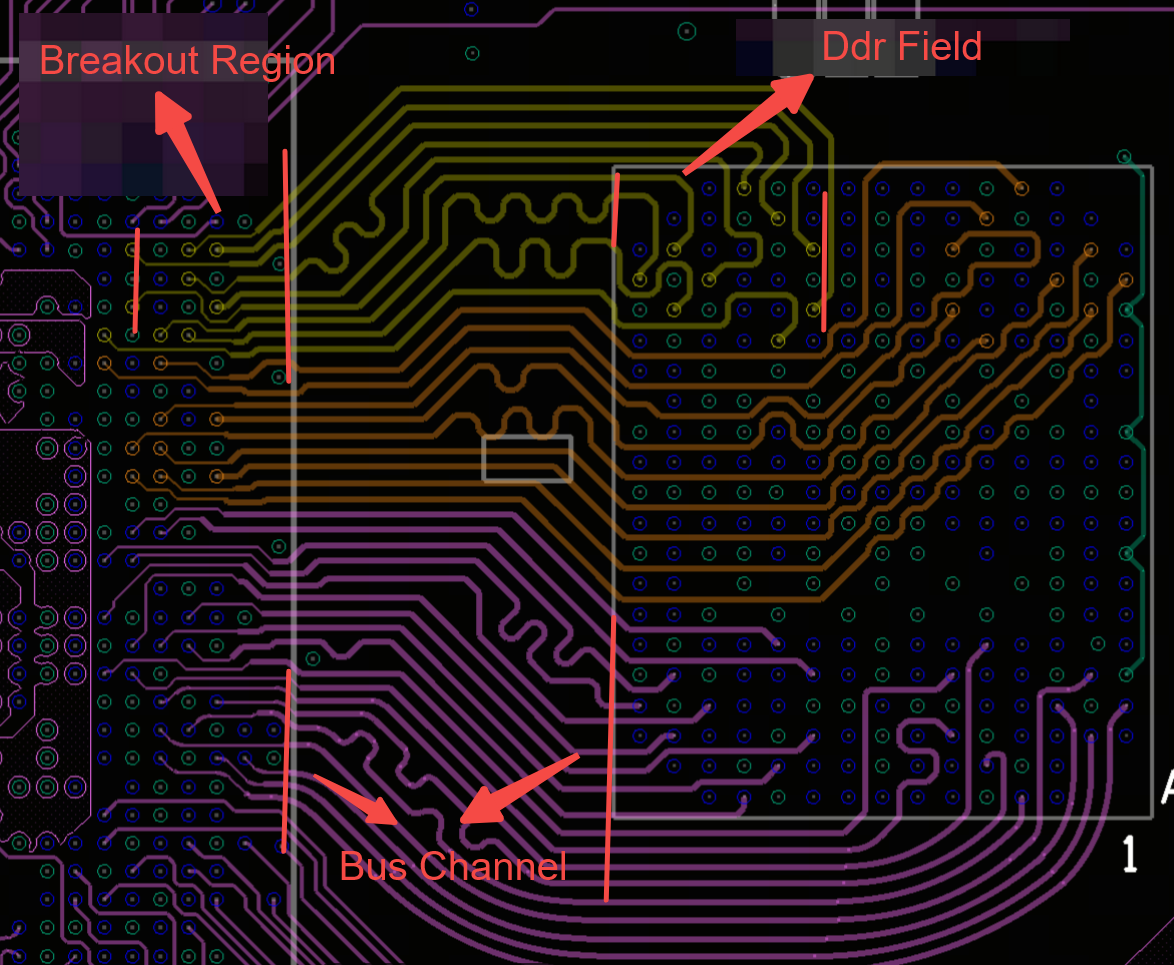

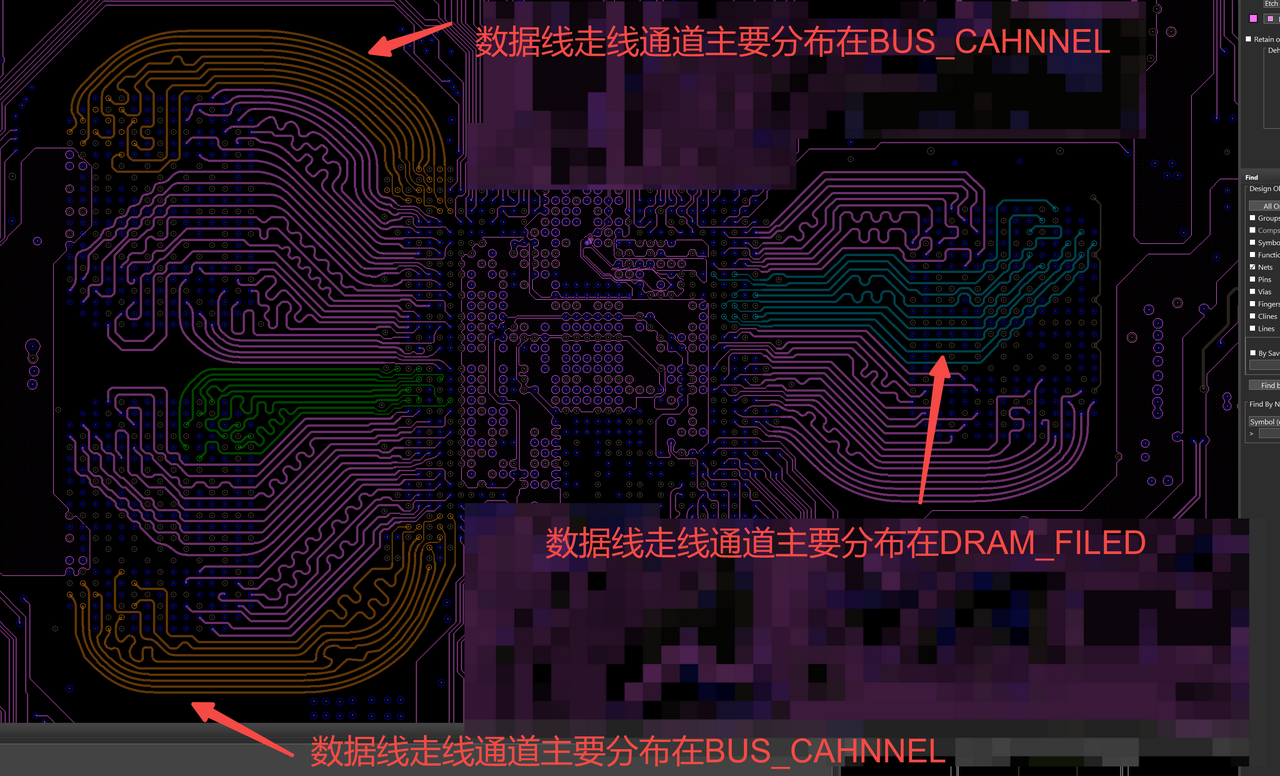

二 单纯的从PCB单板的走线长度看,DDR0_DFI0_B0这组数据线可能不是最长的,从下图所示的LPDDR5数据线走线分布情况来看最长的一组应该是在DDR0_DFI1_B1和DDR1_DFI1_B1这两组之间了。

DDR0_DFI1_B1和DDR1_DFI1_B1这两组之数据线的长度如下所示:

DDR0_DFI0_B0这组之数据线的长度如下所示:

我们看下最差的这组DDR2_DFI1_B0数据线的长度:

分析:组DDR2_DFI1_B0数据线的长度直观上是不如DDR0_DFI1_B1和DDR1_DFI1_B1这两组之数据线的长度的,但是DDR2_DFI1_B0这组走线虽然是走线长度不是最长的那组,但是这组BUS走线路径主要分布在了DRAM Field区域了,而不是在我们的Bus Channel这个区域了。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!