图像处理单元 (IPU) 深度技术解析指南

文章目录

- 图像处理单元 (IPU) 深度技术解析指南

-

-

- 技术原理与架构

-

- 1.1 IPU 硬件架构解析

- 1.2 图像处理流水线 (Pipeline)

- 1.3 IPU vs. CPU/GPU

-

- 实现细节与算法流程

-

- 2.1 典型处理流程伪代码

- 2.2 关键参数配置

-

- 性能优化策略

-

- 3.1 内存带宽优化 (Bandwidth Optimization)

- 3.2 并行处理技术

- 3.3 功耗管理

-

- 应用案例与效果对比

-

- 4.1 智能安防监控

- 4.2 车载辅助驾驶 (ADAS)

- 4.3 效果对比展示

- 4.4 性能指标对比

-

- 参考文献

-

1. 技术原理与架构

图像处理单元(Image Processing Unit, IPU)是现代嵌入式系统(如 SoC、DSP)中专门负责图像数据处理的核心硬件模块。它连接着前端的摄像头传感器(Camera Sensor)和后端的显示或编码模块,承担着将原始数据(Raw Data)转化为人眼可观看的高质量图像(RGB/YUV)的重任。

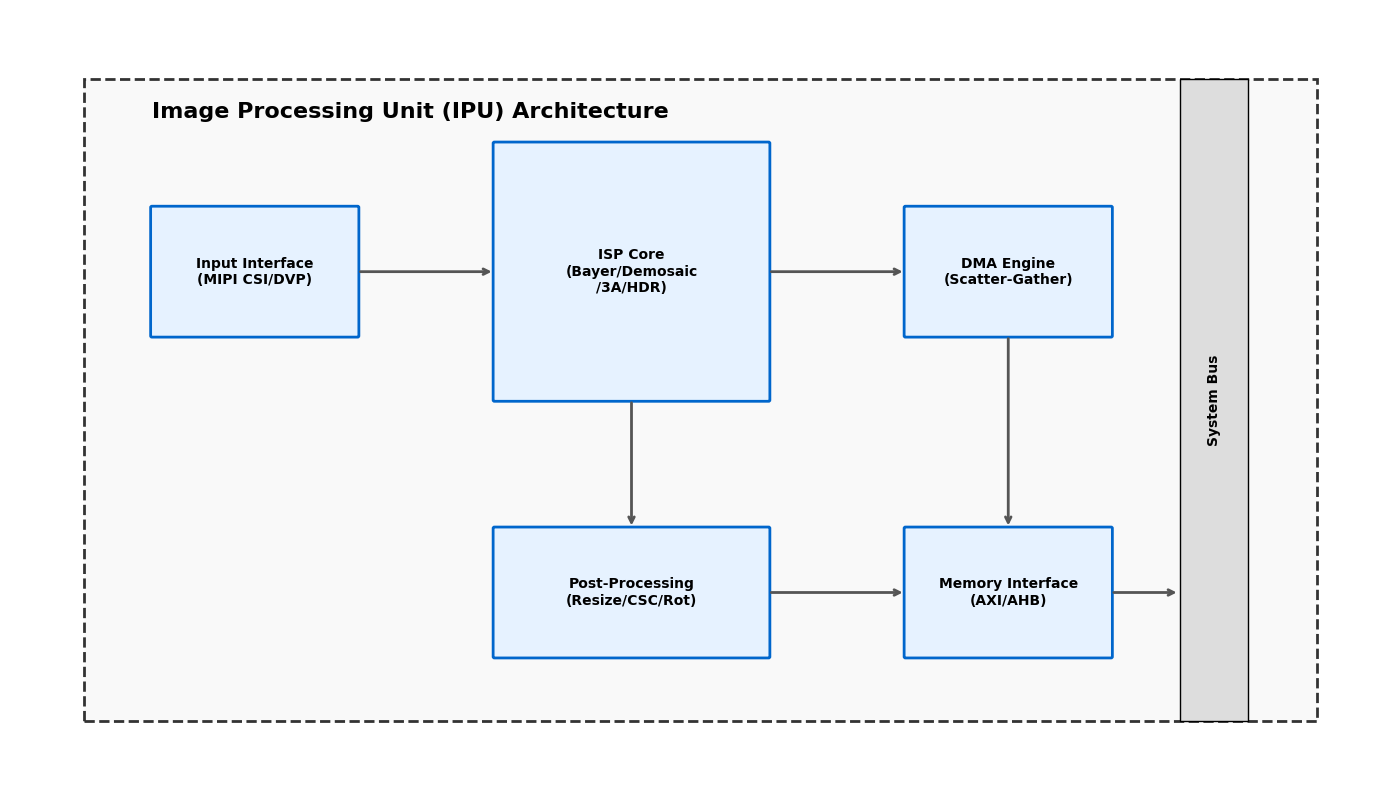

1.1 IPU 硬件架构解析

IPU 通常采用高度流水线化(Pipelined)和并行化(Parallel)的硬件设计,以满足高分辨率(如 4K/8K)和高帧率(60fps+)的实时处理需求。

一个典型的 IPU 子系统包含以下关键组件:

- 输入接口 (Input Interface) :

- 支持 MIPI CSI-2 (Camera Serial Interface) 或并行 DVP 接口,负责高速接收传感器数据。

- 内建 FIFO 缓冲以解决时钟域跨越(Clock Domain Crossing)问题。

- ISP 核心 (Image Signal Processor) :

- IPU 的心脏,包含数十个专用的硬件加速算子(Hardware Accelerators),如去噪、白平衡、去马赛克等。

- DMA 控制器 (Direct Memory Access) :

- 采用 Scatter-Gather 模式,负责在 IPU 和系统内存(DDR)之间高效搬运数据,减少 CPU 干预。

- 后处理引擎 (Post-Processing Engine) :

- 负责图像缩放(Scaler)、色彩空间转换(CSC, 如 YUV 转 RGB)、旋转与翻转。

1.2 图像处理流水线 (Pipeline)

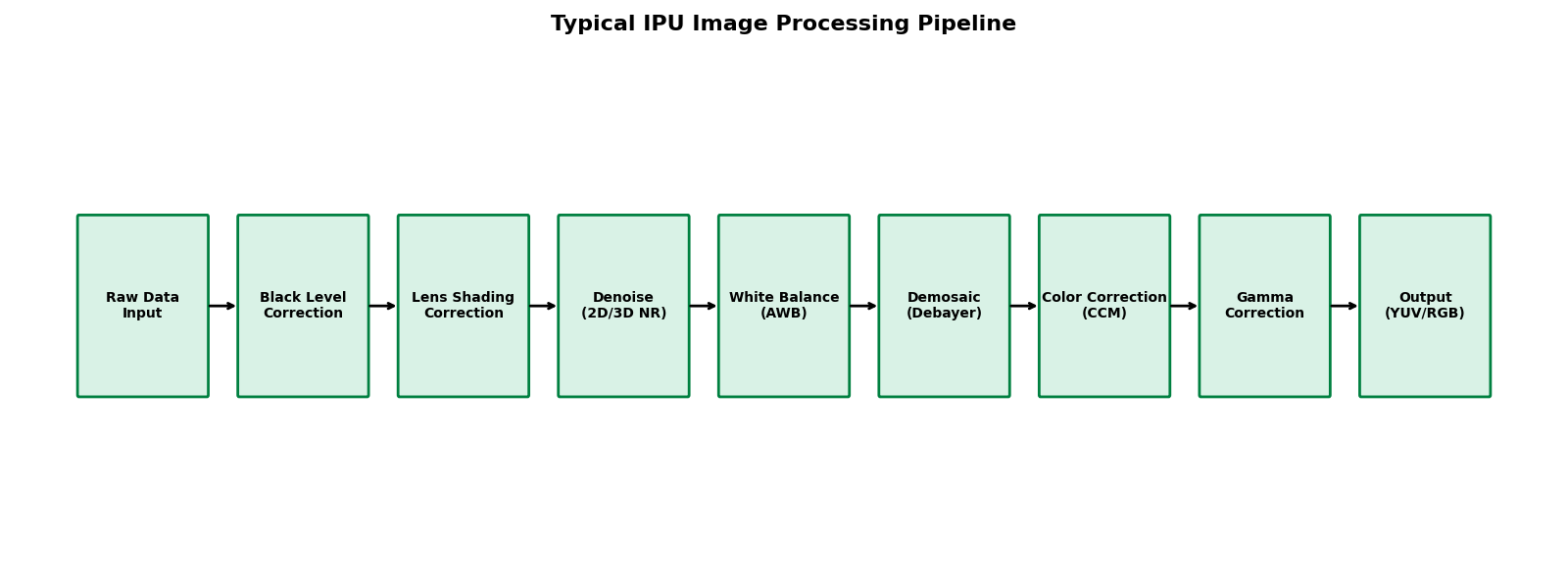

IPU 的处理流程通常是线性的,数据流依次经过各个硬件模块。

- 输入采集 (Input Acquisition): 接收 Bayer Pattern 的 Raw 数据。

- 预处理 (Pre-processing) :

- 黑电平校正 (BLC): 扣除暗电流噪声。

- 镜头阴影校正 (LSC): 修复镜头边缘的亮度衰减(Vignetting)。

- 特征提取与修复 (Restoration) :

- 坏点校正 (DPC): 动态检测并修复传感器坏点。

- 降噪 (Denoise): 2D 空域降噪(保留边缘)与 3D 时域降噪(消除闪烁)。

- 颜色处理 (Color Processing) :

- 白平衡 (AWB): 根据色温调整 R/G/B 增益。

- 去马赛克 (Demosaic): 将 Bayer 格式插值为全彩 RGB。

- 色彩校正矩阵 (CCM): 纠正传感器光谱响应偏差。

- 后处理 (Post-processing): Gamma 校正、锐化、对比度增强。

1.3 IPU vs. CPU/GPU

| 特性 | IPU (专用硬件) | CPU (通用处理器) | GPU (图形处理器) |

|---|---|---|---|

| 处理模式 | 硬件流水线,数据流驱动 | 串行指令执行 | 并行计算 (SIMD) |

| 能效比 | 极高 (专用电路) | 低 (指令解码开销大) | 中 (适合大规模浮点) |

| 延迟 | 微秒级 (Line Buffer) | 毫秒级 (Frame Buffer) | 毫秒级 |

| 灵活性 | 低 (算法固化) | 高 (任意编程) | 高 (Shader 编程) |

| 典型任务 | ISP, Resize, CSC | 逻辑控制, 复杂决策 | 3D 渲染, 深度学习 |

2. 实现细节与算法流程

2.1 典型处理流程伪代码

以下伪代码展示了一个简化的 IPU 处理逻辑,实际硬件中这些步骤是并行流水的。

python

class ImageProcessingUnit:

def process_frame(self, raw_frame, params):

"""

IPU Frame Processing Sequence

"""

# 1. Pre-processing

# Subtract black level (e.g., 64 for 10-bit)

linear_data = self.black_level_correction(raw_frame, level=64)

# Correct lens shading based on grid map

lsc_data = self.lens_shading_correction(linear_data, params.lsc_table)

# 2. ISP Core Processing

# Apply Digital Gain (White Balance)

wb_data = self.apply_awb_gains(lsc_data, r_gain=2.1, b_gain=1.8)

# Demosaic (Bayer -> RGB)

rgb_image = self.demosaic_bilinear(wb_data)

# Color Correction Matrix (3x3)

corrected_rgb = self.apply_ccm(rgb_image, params.ccm_matrix)

# Gamma Correction (Linear -> sRGB)

gamma_rgb = self.apply_gamma(corrected_rgb, gamma=2.2)

# 3. Post-processing

# Convert to YUV for encoder

yuv_output = self.rgb_to_yuv(gamma_rgb)

return yuv_output

def demosaic_bilinear(self, bayer):

# Simplified Bilinear Interpolation

# G_at_R = (G_left + G_right + G_up + G_down) / 4

pass2.2 关键参数配置

配置 IPU 时,需要根据传感器特性和应用场景设定参数:

- 分辨率 (Resolution): 如 3840x2160 (4K)。需注意对齐要求(如 16 字节对齐)。

- 数据格式 (Format) :

- Input: RAW10, RAW12 (Mipi Packed/Unpacked).

- Output: NV12, YUYV, RGB888.

- 时钟频率 (Clock): 决定最大像素吞吐率(Pixel Throughput)。例如 4K@60fps 需要约 500MHz 的像素时钟。

3. 性能优化策略

3.1 内存带宽优化 (Bandwidth Optimization)

- 分块处理 (Tile-based Processing): 将图像分割成小块(Tile),利用片上 SRAM (Line Buffer) 进行处理,减少对 DDR 的反复读写。

- 压缩传输 (Frame Compression): 在 IPU 各级之间使用无损压缩(如 ARM AFBC),可节省 30%-50% 带宽。

3.2 并行处理技术

- 多路 ISP (Dual ISP): 对于超高像素传感器,将其左右分割,由两个 ISP 核心并行处理,最后在后端拼接。

- 硬件流水线: 当前行正在做去噪时,下一行已经开始做黑电平校正,实现"吞吐量 = 时钟频率"。

3.3 功耗管理

- 时钟门控 (Clock Gating): 当某个子模块(如锐化模块)不工作时,自动关闭其时钟。

- 动态电压频率调整 (DVFS): 根据当前负载(如从 4K 切换到 1080p),动态降低电压和频率。

4. 应用案例与效果对比

4.1 智能安防监控

- 挑战: 低照度、高动态范围(逆光)。

- IPU 方案: 启用宽动态(WDR)模块,融合长短曝光两帧图像;启用 3D 降噪。

- 效果: 暗处噪点明显减少,亮处不过曝。

4.2 车载辅助驾驶 (ADAS)

- 挑战: 极低延迟、高可靠性。

- IPU 方案: 直通模式(Bypass),仅做必要的去马赛克和色彩转换,关闭美颜等耗时模块。

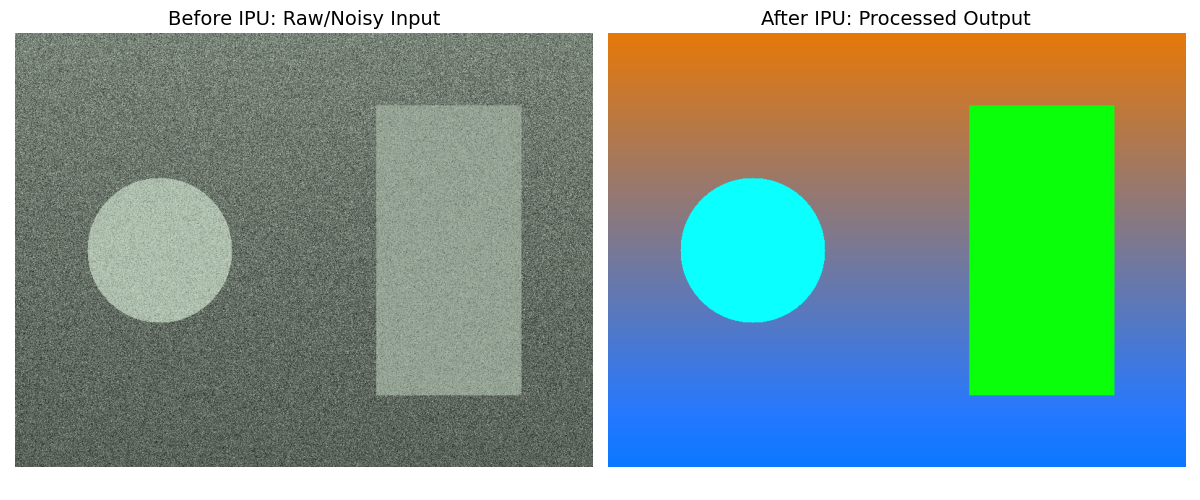

4.3 效果对比展示

下图展示了 IPU 处理前(Raw Domain 模拟图)与处理后(经过 ISP 管道)的视觉差异。

4.4 性能指标对比

| 指标 | 纯 CPU 处理 (ARM Cortex-A53) | 专用 IPU 处理 | 提升幅度 |

|---|---|---|---|

| 4K 处理帧率 | 2 - 3 fps | 60 fps | 20x - 30x |

| 处理延迟 | > 100ms | < 10ms (Line-based) | > 10x |

| 功耗 | ~2W (满载) | ~200mW | 10x 更低 |

| CPU 占用率 | 100% | < 5% (仅配置寄存器) | 释放 CPU |

5. 参考文献

- S. H. Park et al., "A low-power image signal processor for 8K UHD video applications," IEEE Transactions on Consumer Electronics, 2020.

- J. Adams, "The Architecture of Cameras," Stanford University CS448A Course Notes.

- MIPI Alliance, "MIPI Camera Serial Interface 2 (CSI-2) Specification."

- Ramanath, R., et al., "Color image processing pipeline," IEEE Signal Processing Magazine, 2005.