电容和电阻是不同的,电阻的阻抗就一个 R,而电容的容抗:

根据容抗的公式,如果频率越大,Xc 是不是越小?那 么是不是电容的阻抗就随频率升高无限变小呢?

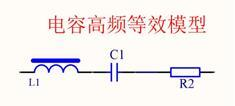

一开始确实是电容的阻抗逐渐变小的过程。但是,当频率大到某个程度,电容的总阻抗就不再仅仅

是 Xc,也就是电容的"总阻抗",不再仅仅是容抗,我们来看电容的高频等效模型。

电容在高频电路中,其内部寄生参数就不能忽略。L1 可以叫它寄生电感 ESL;R2 就是它的寄生电阻 ESR,此时就不能再忽略。电阻有阻抗,电容有容抗,电感有感抗。

在高频电路中,即使是一小段导线,它也是有电阻的吧,虽然这个电阻很小,但总会有。同样的,即使是一小段导线,它也有一定的感量,虽然说这个感量很小,但总会有。

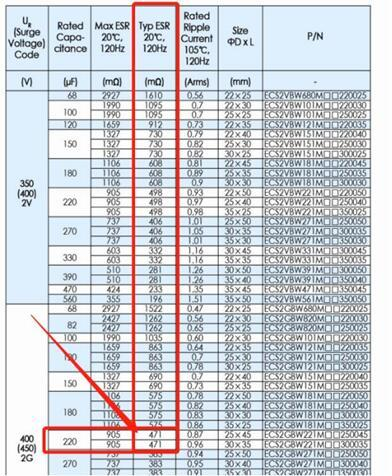

以铝电解电容为例:

插件电解电容的长引脚在高频下就是一个弊端,存在一定的感量。所以,铝电解电容相对于贴片电容寄生参数就要大很多。

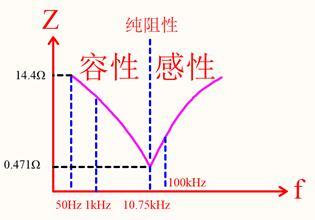

以这个铝电解电容为例,Esl=1uH,Esr=471mΩ,电容量为220uF,

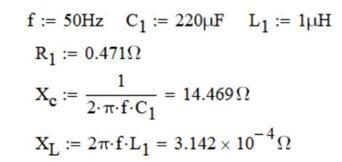

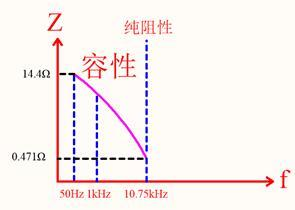

假设f=50Hz

三者数值,容抗最大

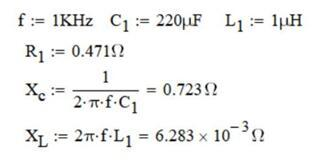

假设f=1KHz

容抗和电阻差不多一个量级了

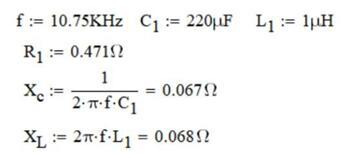

假设f=10.75KHz

感抗和容抗差不多相等了而且很小

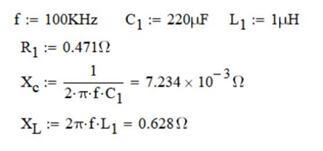

继续加大频率,假设f=100KHz

此时容抗很小,但是感抗开始增大了

总结:

对于电容来说,高频下它就是一个C,L,R串联的。若是想滤除高频干扰,就不能选电解电容。应为它总阻抗很大。需要用寄生参数更小的贴片电容来滤除高频干扰。

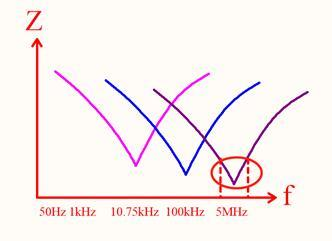

上面这个曲线表示的贴片电容的,在5M Hz附近,它的总阻抗最小。所以这个电容滤除5MHz这个频段的干扰效果最好。

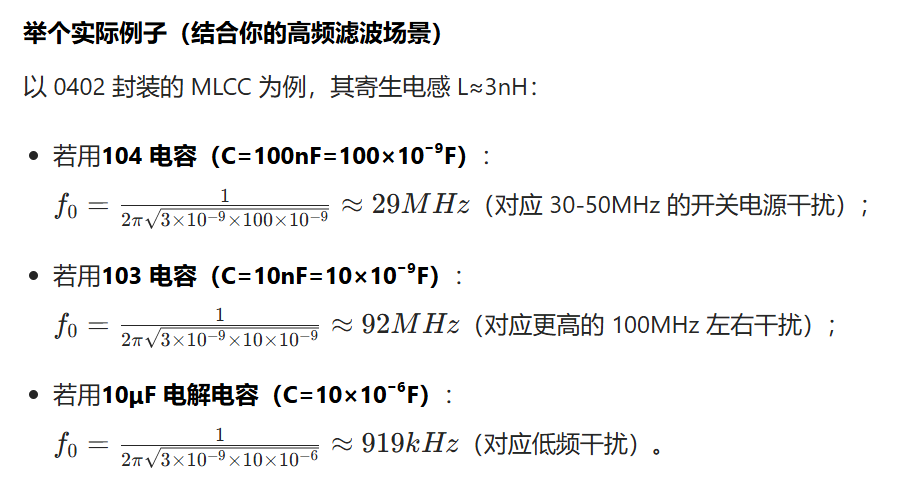

芯片引脚旁边一般防止10uF储能电容,还要并联一个104贴片电容。还有15V,12V,5V输出端也会并联一个104贴片电容。这个104电容就是用来滤除高频干扰的。

电容的谐振频率由 "容值(C)+ 寄生电感(L)" 共同决定,同类型电容的 L 基本固定,因此容值越小→谐振频率越高,能匹配更高频段的干扰;容值越大→谐振频率越低,匹配更低频段的干扰。这也是 "小电容滤高频、大电容滤低频" 的核心原理。