传输示例

接口连接

基本传输只连接最基础的接口信号,device clock同时给到TX RX,RX的SYNC接到TX,TX的lane信号接到RX。对于Subclass1后面sysref小节会添加sysref信号,对于Subclass2确定性延时还需要添加adj时钟信号。

assign jesd204_rx_if.dev_clk = SystemClock;

assign jesd204_tx_if.dev_clk = SystemClock;

assign jesd204_tx_if.sync = jesd204_rx_if.sync;

assign jesd204_rx_if.lane[j].dn = jesd204_tx_if.lane[j].dn;

assign jesd204_rx_if.lane[j].dp = jesd204_tx_if.lane[j].dp;配置

配置协议版本为JESD204版本B、8b10b编码、Subclass0、串行模式,JESD204B只支持8b10b编码。协议其实没提到串行并行,完整协议就是串行,对于一些没有PHY的验证场景可以选并行,并行数据宽度在8b10b时就是10b,在64b66b时就是66b。

tx_agent_cfg.coding_type==svt_jesd204_types::JESD204_8B_10B_CODING;

tx_agent_cfg.rev_num==svt_jesd204_types::JESD204_VER_B;

tx_agent_cfg.subclass_type = svt_jesd204_types::SUBCLASS_0;

tx_agent_cfg.interface_type = svt_jesd204_types::SERIAL_MODE;配置传输层参数,例如M、S、N、F、K等。

/** Configure Number of Converters */

tx_agent_cfg.m_converter = 2;

/** Configure Number of Lanes */

tx_agent_cfg.no_of_lane = 1;

/** Configure Total Number of Data Bits Per Sample(N') */

tx_agent_cfg.net_sample_size = 16;

/** Configure Total Number of Bits Per Sample(N) */

tx_agent_cfg.data_sample_size = 16;

/** Configure Number of Octets Per Frame*/

tx_agent_cfg.f_octets = 4;

/** Configure Number of Frame Per Multiframe */

tx_agent_cfg.k_multiframe = 5;

/** Configure Number of Samples Per Converters */

tx_agent_cfg.s_sample = 1; sequence

1帧对应1个传输包,通过sample配置传输数据,假如多转换器过采样(M>1 & S>1)场景,需要自己先把数据穿插到数组sample中。

`uvm_do_on_with(xact,p_sequencer.tx_seqr[0],

{

xact.cmd_type == svt_jesd204_transaction::DATA_COMMAND;

xact.sample.size == sample_size;

foreach(xact.sample[i]) xact.sample[i] == (i+1) + 2*j;

});也可以使用`uvm_create、`uvm_send进行传输。

`uvm_create_on(xact,p_sequencer.tx_seqr[0]);

if(!(xact.randomize() with

{

xact.cmd_type == svt_jesd204_transaction::DATA_COMMAND;

xact.sample.size == sample_size;

foreach(xact.sample[i]) xact.sample[i] == (i+1) + 2*j;

}))

`uvm_send(xact);传输波形

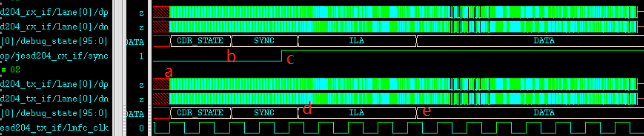

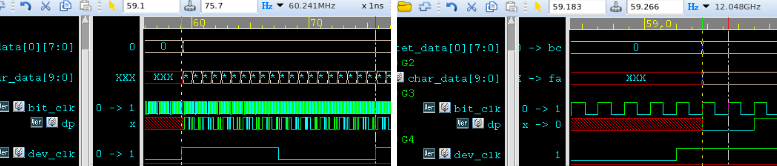

可以看到传输状态从CDR->SYNC->ILA->DATA变化,CDR、SYNC期间TX一直发送K28.5,然后发送ILA序列和DATA。

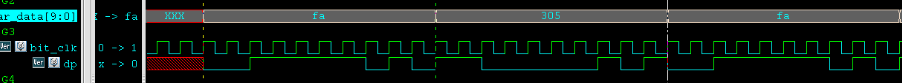

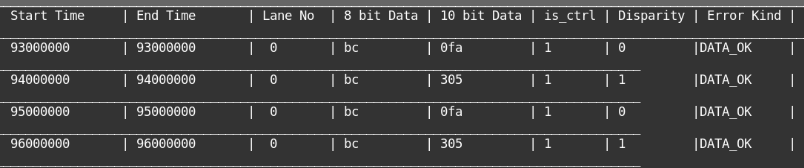

K28.5 10b对应0x0fa、0x305循环,可以从lane上看到10b数据,先发高位。

log打印

通过log文件jesd204_env_h.device_agent.tl_mon、ll_mon、pl_mon可以看到传输层、链路层和物理层数据。

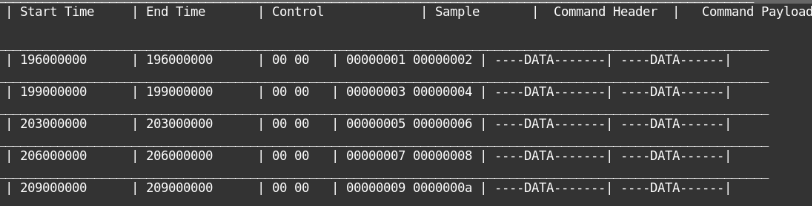

传输层,可以看到发送的递增数,1、2、3、4...

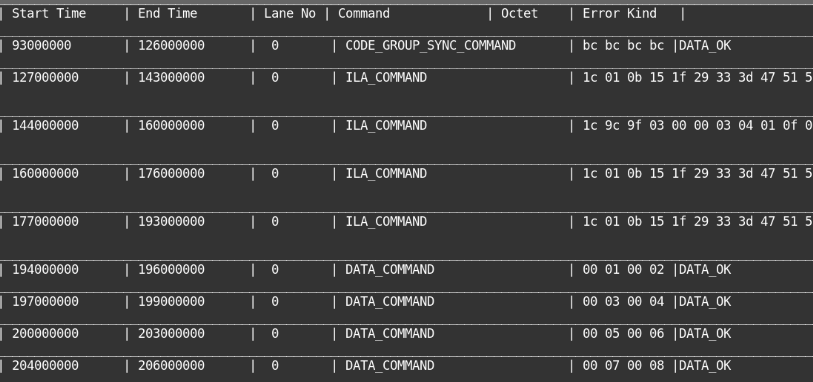

链路层,可以看到先发送K28.5序列,再发4帧ILA序列,再发送数据。其实K28.5在一直发,但log只显示了4个字符。

物理层,可以看到所有lane上信息,先开始发k28.5序列,0xbc按RD+/RD-查表得到的0xfa、0x305循环,表中也可以看到解码得到的RD。后面还可以看到ILA序列和数据的8b10b值,不再列举。

其他传输事项

传输类型

复位后VIP会自动建链,TX发K28.5同步序列,RX拉低SYNC,TX再发ILA序列,这个过程是不需要用户发起trans实现的。然后发起DATA_COMMAND类型传输,1次对应1帧。

xact.cmd_type = svt_jesd204_transaction::DATA_COMMAND;对于希望重新同步的场景,可以通过传输类型CODE_GROUP_SYNC_COMMAND实现。TX driver收到trans后开始重新发送K28.5同步序列,RX收到后重新把SYNC拉低,然后重新建链。

xact.cmd_type = svt_jesd204_transaction::CODE_GROUP_SYNC_COMMAND;对于传输类型ILA_COMMAND,会重新同步,但因为DATA状态也不能接ILA序列,还要重新同步SYNC拉低,所以效果和前相似。

xact.cmd_type = svt_jesd204_transaction::ILA_COMMAND;还有测试序列的传输类型,但这些类型也需要同时修改cfg类,在后小节描述。

传输状态

在同步未完成时即可发起DATA_COMMAND的trans,trans会在ILA结束后发送。但在一些场景还是需要获取传输状态,以准确控制时序。

相应状态主要在svt_jesd204_status类中,svt_jesd204_status类包含成员svt_jesd204_link_status指示链路状态,svt_jesd204_link_status类又包含数组成员svt_jesd204_lane_status指示每条lane的状态。

示例示例化svt_jesd204_status类为converter_tx_status作为TX设备,成员变量包括:

• sync_completion,1指示同步完成;

• sync_deasserted,指示SYNC信号状态。

converter_tx_status.link_status.sync_completion = 0/1;

converter_tx_status.link_status.sync_deasserted = 0/1;• pl_data_sent_completion[idx],指示idx lane传输状态,1:CGS阶段(发送K28.5同步序列)、2:ILA阶段、3:物理层剩余少量数据、4:物理层数据发送完成;

• fsm_state,lane状态机,包含svt_jesd204_types::CDR_STATE、SYNC、ILA、DATA状态。

converter_tx_status.link_status.pl_data_sent_completion[idx]=0~4;

converter_tx_status.link_status.lane_status[idx].fsm_state;device clock计算

正常流程是通过需要的lane速率反推设备时钟device clock。

a)对于JESD204A(Subclass1、2)、JESD204B、JESD204C(8b10b),device时钟和bit时钟关系如下,其中K、F为传输层协议中的帧数和字节数,lmfc_period_multiplier是VIP配置。

Dev_clk_period = bit_clk_period * 10 * K * F / lmfc_period_multiplier

示例符合这个条件,所以时钟关系为60.241M*10*5(K)*F=12.048G。需要注意VIP要求JESD204B的Subclass0也要这样算设备时钟,可能是因为ILA序列长度用到了K。至于JESD204A(Subclass1、2)这个配置就很奇怪,协议里都没有。

b)对于JESD204A(Subclass0),device时钟和bit时钟关系如下,区别主要在没有多帧LMFC概念,也就没有K。

Dev_clk_period = bit_clk_period * 10 * F

c)对于JESD204C(64B/66B),device时钟和bit时钟关系如下。

dev_clk_period = bit_clk_period * 66 / 8 * F_octets * K_multiframe / lemc_period_multiplier 或者

dev_clk_period = bit_clk_period * 66 * 32 * num_multiblock_in_emb / lemc_period_multiplier

skew

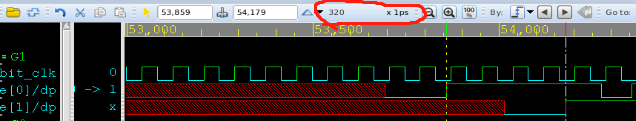

在cfg类中,通过lane_skew可以配置lane之间的偏斜,数组深度为lane数量。偏斜单位是bit时钟周期和320ps中的最大值,

tx_agent_cfg.lane_skew = '{1,2,3,4};

可以通过`SVT_JESD204_LANE_SKEW_VAR_OLD_DECL将lane_skew的数据类行改为real类型,但实际延时还是320的整数倍,不太理解有啥意义。