文章目录

- 1、nRF54L系列总概括

- 2、nRF54L系列功能

- 3、电源域

-

-

- [1. 中央处理单元(CPU核心)](#1. 中央处理单元(CPU核心))

- [2. 内存架构](#2. 内存架构)

- [3. 外设模块与总线分层](#3. 外设模块与总线分层)

- [4. 电源域(Power Domains)](#4. 电源域(Power Domains))

- [5. 关键互连结构](#5. 关键互连结构)

- [6. 调试与安全](#6. 调试与安全)

- [7. GPIO与扩展性](#7. GPIO与扩展性)

- 8.如何理解这张图?

-

- 4、内存

-

-

- [1. CPU(Arm Cortex-M33)](#1. CPU(Arm Cortex-M33))

- [2. RAM(SRAM)分区](#2. RAM(SRAM)分区)

- [3. Cache(缓存)](#3. Cache(缓存))

- [4. 外设接口总线](#4. 外设接口总线)

- [5. AMBIX接口](#5. AMBIX接口)

- [6. FLPR(Flash编程接口)](#6. FLPR(Flash编程接口))

- [7. LP Peripherals(低功耗外设)](#7. LP Peripherals(低功耗外设))

- [8. 内存映射(关键地址范围)](#8. 内存映射(关键地址范围))

- 实际开发中的应用建议

-

- 5、EasyDMA

- 6、相关推荐

1、nRF54L系列总概括

nRF54L15、nRF54L10 和 nRF54L05 构成了 nRF54L 系列。该系列中的所有无线片上系统 (SoC) 选项都集成了超低功耗多协议 2.4 GHz 无线电和 MCU(微控制器单元)功能,具有 128 MHz Arm® Cortex-M33 处理器、全面的外设集以及高达 1.5 MB NVM 和高达 256 KB RAM 的可扩展内存配置。

Nordic 专有技术(如低泄漏 RAM)和高级多协议无线电中采用的设计专业知识实现了超低功耗。nRF54L 系列中的每个无线 SoC 都具有更低的功耗,可延长电池寿命或减小电池尺寸。

nRF54L 系列 SoC 在设计时充分考虑了多功能性,适用于广泛的应用。多协议 2.4 GHz 无线电支持最新的蓝牙® 6.0 功能,包括蓝牙信道探测,以及适用于 Thread®、Matter 和 Zigbee® 等标准的 802.15.4-2020,以及支持高达 4 Mbps 的专有 2.4 GHz 模式,以实现更高的吞吐量。这些器件集成了无线微控制器中预期的外设,使许多产品能够通过单个芯片实现。集成的 RISC-V 协处理器进一步减少了对外部 IC 的需求。

2、nRF54L系列功能

nRF54L 系列无线 SoC 提供一系列内存和封装配置,包括引脚对引脚兼容选项。由于有多种存储器选项,因此找到适合应用的合适器件可以优化设计成本和灵活性。

主要特点

-

128 MHz Arm Cortex-M33® 处理器

-

高达 1.5 MB NVM 和高达 256 KB RAM 的可扩展内存配置

-

多协议 2.4 GHz 无线电,支持低功耗蓝牙、802.15.4-2020 和 2.4 GHz 专有模式(最高 4 Mbps)

-

全面的外设集,包括系统 OFF 中提供的新全局 RTC、14 位 ADC 和高速串行接口

-

128 MHz RISC-V 协处理器

-

高级安全性,包括 TrustZone® 隔离、篡改检测和加密引擎侧信道泄漏保护

-

超紧凑封装

- WLCSP 2.4 x 2.2 毫米

- QFN 6.0x6.0 毫米

-

多协议无线电

-

蓝牙 6.0、IEEE 802.15.4-2020 和支持 2.4 GHz 的收发器

- 在 1 Mbps 低功耗蓝牙模式下灵敏度为 -96 dBm,误码率为 0.1%

- 在 125 kbps 低功耗蓝牙模式(长距离)下灵敏度为 -104 dBm,误码率为 0.1%

- -102 dBm 典型灵敏度(IEEE 802.15.4 标准)

- 高达 +8 dBm 的可配置输出功率;1 dB 步长,从 -8 dBm 到 +8 dBm

- 支持的数据速率:

- 蓝牙 6.0 -- 2 Mbps、1 Mbps、500 kbps 和 125 kbps

- IEEE 802.15.4-2020 -- 250 kbps

- 专有 2.4 GHz -- 4 Mbps、2 Mbps 和 1 Mbps

- 单端天线输出(片上巴伦)

- 128 位 AES/ECB/CCM/AAR 协处理器(动态作)

- RSSI (1 dB 分辨率)

-

平台安全性

- 安全/非安全内存保护

- 对称和非对称密钥加密加速器

- 安全的密钥管理

- 篡改检测

- 不可变引导分区

- 调试访问端口保护

- 两个看门狗定时器,用于安全和非安全访问

-

内存

- nRF54L15 -- 1524 KB 非易失性存储器 (RRAM) 和 256 KB RAM

- nRF54L10 -- 1022 KB 非易失性存储器 (RRAM) 和 192 KB RAM

- nRF54L05 -- 500 KB 非易失性存储器 (RRAM) 和 96 KB RAM

-

运行状态

- 1.7 V 至 3.6 V 电源和 I/O 电压

- 单个 32 MHz 晶振作

- 可选 32.768 kHz 时钟

- 工作温度从 -40°C 到 105°C

-

采用 TrustZone 技术的 Arm Cortex-M33,128 MHz

- 从非易失性内存运行 500 EEMBC CoreMark® 分数,每 MHz 3.90 CoreMark

- 单精度浮点单元 (FPU)

- 内存保护单元 (MPU)

- 数字信号处理 (DSP) 指令

- 数据观察点和跟踪 (DWT)、嵌入式跟踪宏单元 (ETM)、仪表跟踪宏单元 (ITM) 和交叉触发接口 (CTI)

- 串行线调试 (SWD)

- 跟踪端口接口单元 (TPIU)

- ITM 和 ETM 跟踪数据的 4 位并行跟踪

- ITM 数据的串行线输出 (SWO) 跟踪

-

外设

- RISC-V 协处理器

- 全局 RTC (GRTC),可在 System OFF 模式下运行并实现共享系统定时器

- 7 个 32 位定时器,带计数器模式

- 多达 5 个功能齐全的串行接口,带 EasyDMA,支持 I2C、SPI 控制器/外设和 UART

- 1 个高达 32 MHz 的高速 SPIM,4 个高达 8 MHz 的高速 SPIM

- 1 个高达 4 Mbps 的高速 UARTE,4 个高达 1 Mbps 的 UARTE

- I2C 至 400 kHz

- 三个带 EasyDMA 的脉宽调制器 (PWM) 单元

- I2S 双通道 Inter-IC 声音接口

- 具有多达 8 个可编程增益通道的 ADC。14 位 31.25 ksps,12 位 250 ksps 和最高 10 位 2 Msps。

- 脉冲密度调制 (PDM) 接口

- 近场通信 (NFC)

- 多达 2 个正交解码器 (QDEC)

- 比较器和低功耗比较器,可从 System OFF 模式唤醒

- 温度传感器

-

封装

- QFN48 6.0x6.0 mm,带 31 个 GPIO 引脚

- WLCSP 2.4x2.2 mm,带 32 个 GPIO 引脚

- 300 μm 间距

3、电源域

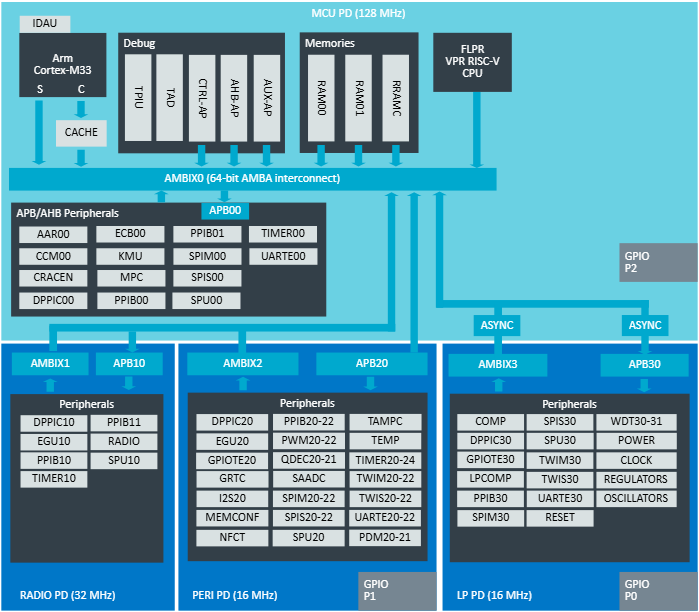

方框图:框图说明了整个系统。

1. 中央处理单元(CPU核心)

- Arm Cortex-M33 (128MHz):

主处理器,负责运行应用程序,支持TrustZone安全扩展和浮点运算。 - RISC-V协处理器 (FLPR/VPR):

通常用于低功耗场景或专用任务处理(如传感器数据预处理),与M33协同工作。

2. 内存架构

- RA400/RAM01/RR/AMC :

不同用途的内存区域,可能包括:- RA400:高速缓存或紧耦合内存(TCM)。

- RR/AMC:保留内存或加密内存区域。

- 非均匀访问设计:通过AMBIX互连总线连接,优化不同模块的内存访问效率。

3. 外设模块与总线分层

外设通过**APB(低速)和AHB(高速)**总线分层连接:

- APB00-APB30 :

外设分组示例:- APB00:基础外设(AAR00加密模块、ECB00电子密码本)。

- APB20:丰富外设(SPIM20 SPI主机、TWIM20 I2C、UART20串口)。

- APB30:系统管理(WDT30看门狗、POWER电源控制)。

- 专用加速模块:如RADIO(2.4GHz射频)、NFCT(NFC标签读写)。

4. 电源域(Power Domains)

电源域划分实现动态功耗管理:

- MCU PD:主CPU核心域,通常常开。

- RADIO PD(32MHz):射频模块独立供电,仅在通信时激活。

- PERI PD(16MHz):外设域,可按需关闭未使用外设。

- LP PD(低功耗域):包含GPIO P0/P1等,支持休眠状态唤醒。

- 动态切换:通过REGULATORS和CLOCK模块调节各域电压/频率。

5. 关键互连结构

- AMBIX0-AMBIX3 :

基于AMBA协议的64位互连总线,实现:- 低延迟CPU与内存通信(AMBIX0)。

- 外设与DMA控制器数据交换(AMBIX2)。

- DMA支持:通过DPPIC模块管理外设间直接数据传输,减少CPU负载。

6. 调试与安全

- 调试接口 :

- AHB-AP/AUX-AP:用于JTAG/SWD调试访问。

- SPU(安全保护单元):隔离敏感资源(如加密密钥)。

- 硬件加密:AAR00/ECB00模块支持AES-256等算法。

7. GPIO与扩展性

- GPIO P0/P1/P2 :

分组供电,支持独立唤醒(如P0在休眠时检测按键)。 - 复用功能:每个GPIO可配置为SPI/I2C/UART等外设引脚。

8.如何理解这张图?

- 横向看数据流 :

CPU通过AMBIX总线访问内存,外设通过APB总线与CPU交互,射频等高速模块直连AHB。 - 纵向看电源管理 :

不同电源域可独立开关(如关闭RADIO PD以省电),通过POWER模块协调。 - 设计意图 :

Nordic通过模块化设计平衡性能与功耗,适合物联网设备(如蓝牙传感器)。

如果需要更具体的某部分(如RADIO时序或低功耗流程),可进一步展开说明。

多个电源域确保低功耗运行。

MCU 域包含一个 Arm Cortex-M33。CPU 连接到调试系统,允许调试和 ETM 跟踪。CPU 通过指令缓存执行来自 RRAM 的程序代码。数据存储在单周期 RAM 中,该 RAM 被划分为多个总线从属,但它在 memory map 中形成一个连续的 RAM 空间。高速外设也存在于 MCU 领域。

还有三个额外的域分配了外围设备。他们是 以后:

- Radio domain (无线电域) -- 包含无线电协议堆栈使用的短程无线电和支持外围设备。它与 MCU 域同步以 32 MHz 运行。

- Peripheral domain (外围域) -- 包含大多数外围设备。它与 MCU 域同步以 16 MHz 的速度运行。

- 低功耗域 -- 包含用于超低功耗模式的外设,可用于唤醒系统的其余部分,即使外设域已关闭。它以 16 MHz 的速率与 MCU 域异步运行。

每个域都映射到一条 APB 总线,并且可以独立供电。来自每个域的 EasyDMA 流量聚合在本地 AMBIX 互连中,并且可以访问 MCU 域中的 RAM。

其中 3 个 Power Domain 有自己的 GPIO 端口。GPIO 引脚可由同一电源域中的外设使用。有关例外情况,请参阅 GPIO --- 通用输入/输出和 PIN 分配。

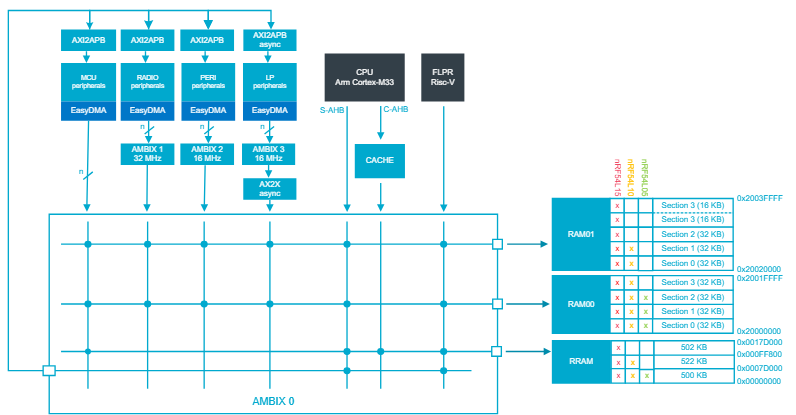

4、内存

带有 EasyDMA 的 CPU 和外设可以通过 AMBIX 互连访问内存。相同的 interconnect 也用于 CPU 对 peripheral registers 的访问。下图是简化的互连图。

1. CPU(Arm Cortex-M33)

- 功能:中央处理单元,执行指令和数据处理。

- 关键接口 :

- S-AHB总线:系统高速总线,用于连接高性能外设(如Cache、RAM)。

- C-AHB总线:代码高速总线,专用于指令取指(如Flash访问)。

- 特点:支持TrustZone安全扩展和低功耗模式。

2. RAM(SRAM)分区

- RAM00/RAM01 :片内静态存储器(SRAM),分为多个地址块:

- 地址范围 :例如

0x20000000-0x2003FFFF(32KB)。 - 用途 :

- 数据存储:全局变量、堆栈。

- 代码执行(XIP):可将关键代码拷贝到RAM加速运行。

- 地址范围 :例如

- SRAM其他块:可能用于特定外设的DMA缓冲区或安全隔离区域。

3. Cache(缓存)

- 类型:通常指指令/数据缓存(如L1 Cache)。

- 连接:通过S-AHB总线与CPU交互。

- 作用:减少访问Flash/RAM的延迟,提升性能。

4. 外设接口总线

- AXI2APB桥 :

- 功能:将高速AXI总线转换为低速APB总线,连接简单外设(如GPIO、UART)。

- 协议差异:AXI支持高吞吐量,APB适合低功耗外设。

- EasyDMA :

- 功能:轻量级DMA控制器,用于外设与RAM间直接数据传输(如ADC采样到内存)。

- 优势:无需CPU干预,降低功耗。

5. AMBIX接口

- 类型:AMBIX 是 Nordic 芯片内部的片上互联总线(基于 AMBA 协议),用于连接 CPU、内存和外设(类似于内部的高速公路网),它不是用于连接外部传感器(如温湿度计)的外部接口(如 SPI/I2C/UART)。

- 速度:图中标注了多组AMBIX(如32MHz、16MHz),可能用于连接外部传感器或无线模块(如蓝牙射频)。

- 用途:灵活配置为Master/Slave模式,支持多设备级联。

6. FLPR(Flash编程接口)

- 功能:用于固件更新或运行时Flash读写。

- 操作:通过特定寄存器擦除/编程Flash扇区。

7. LP Peripherals(低功耗外设)

- 示例:RTC(实时时钟)、WDT(看门狗)。

- 设计目标:在CPU休眠时维持基本功能,最小化能耗。

8. 内存映射(关键地址范围)

- 0x00000000-0x1FFFFFFF:通常为Flash区域(存储代码)。

- 0x20000000-0x3FFFFFFF:SRAM区域(数据)。

- 0x40000000-0x5FFFFFFF:外设寄存器地址空间。

实际开发中的应用建议

- 性能优化:将频繁访问的数据放入RAM或Cache。

- DMA配置:使用EasyDMA处理高速数据流(如音频采集)。

- 低功耗设计:通过LP外设和休眠模式降低功耗。

- 安全隔离:利用TrustZone划分安全/非安全内存区域。

如果需要更具体的某部分(如DMA配置细节或地址分配),可进一步展开说明。

请参阅框图、AMBA 互连 (AMBIX) 和 EasyDMA 了解有关 AMBIX 互连和 EasyDMA 的更多信息。

RAM 和 RRAM 内存区域受 TrustZone® 安全性保护,并在重置后是安全的。可以使用 MPC --- 内存权限控制器将内存区域配置为不安全。

5、EasyDMA

EasyDMA 是一种硬件模块(常见于 Nordic 半导体芯片,如蓝牙低功耗芯片 nRF 系列),它的核心作用是让外设(如传感器、通信模块)直接和内存交换数据,跳过 CPU 的参与,从而大幅降低 CPU 负担和系统功耗

1.通俗比喻:

想象你要从仓库搬货到商店:

- 传统方式(无 DMA):你需要亲自(CPU)一箱一箱搬运,全程不能做其他事。

- 使用 EasyDMA:你雇了一个快递员(EasyDMA),告诉它仓库地址、商店地址和搬运数量后,就可以去喝茶(CPU 休眠或处理其他任务)。快递员会自动搬完所有货物,完成后通知你。

2.主要作用:

- 省 CPU

CPU 不用参与数据搬运,可以处理其他任务(如算法、用户交互)或进入低功耗模式(对物联网设备省电至关重要)。 - 高效率

例如蓝牙芯片传输数据时,EasyDMA 能直接将射频模块收到的数据写入内存,或从内存读取数据发送出去,速度快且稳定。 - 低功耗

CPU 休眠时间越长,设备整体耗电越低(尤其适合电池供电的物联网设备)

3.典型应用场景:

- 传感器数据采集

比如温度传感器持续采集数据,EasyDMA 自动将数据存入内存,CPU 只在需要时批量处理。 - 无线通信(蓝牙/Wi-Fi)

发送/接收数据包时,EasyDMA 直接搬运数据,减少通信延迟。 - 音频传输

实时音频流通过 EasyDMA 传输,避免 CPU 频繁中断导致卡顿。

6、相关推荐

想系统学习BLE可阅读下面文章

(一)蓝牙的发展历史

(二)蓝牙架构概述-通俗易懂

(三)BLE协议栈协议分层架构设计详解

(四)BLE的广播及连接-通俗易懂

(五)图文结合-详解BLE连接原理及过程

(六)BLE安全指南:别让"配对降级"和硬件I/O毁了安全等级(BLE SMP)

(七)Nordic实战--保姆级教程:nRF Connect SDK 开发环境搭建全指南