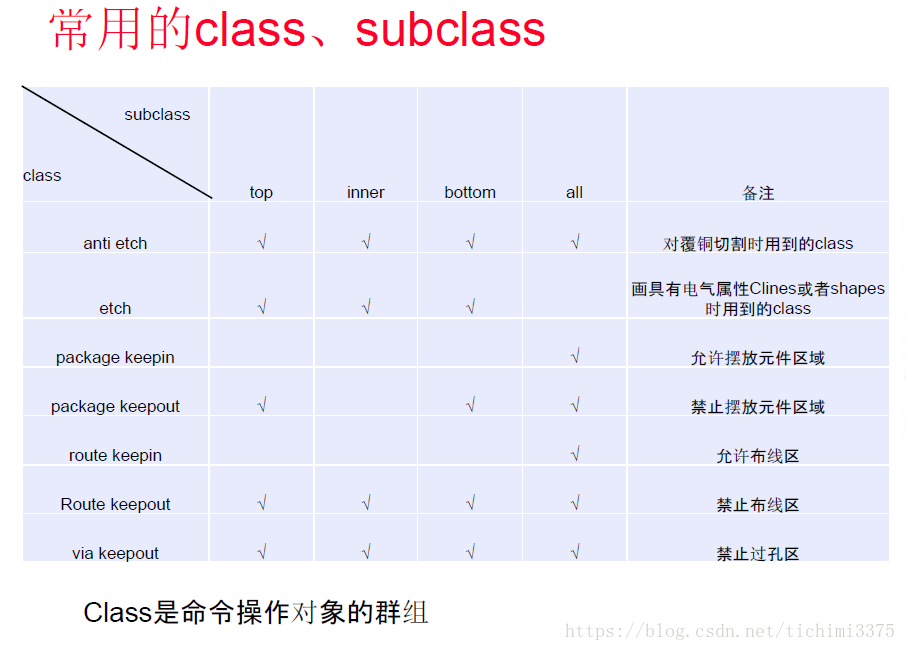

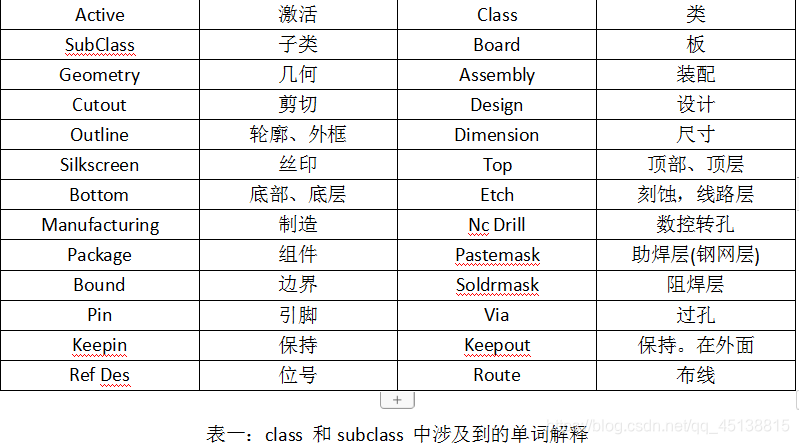

一、class和subclass

1.**Route Keepin:**允许布线区(经常用于outline内缩10mil,用来限制布线区域)

2.**Route Keepout:**禁止布线区(经常用于PCB封装时电感下方的区域内,不能布线)

3.**Via Keepout:**禁止放置Via区

4.**Package Keepin:**允许布局区

5.**Package Keepout:**禁止布局区(一些特殊要求的场合)

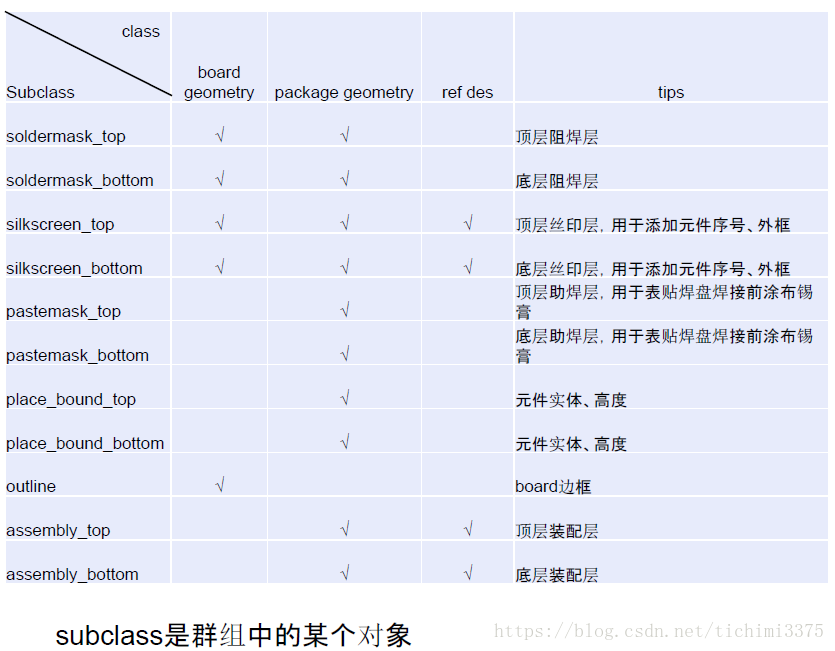

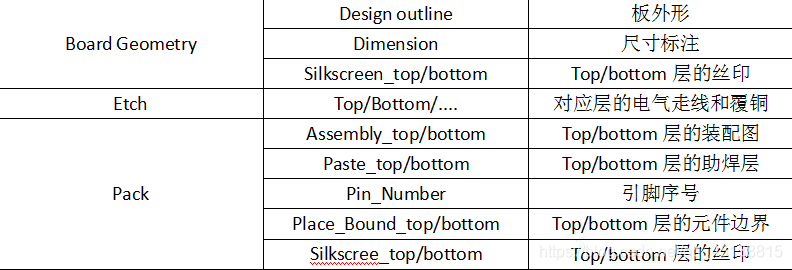

Board Geometry

1.Silkscreen-Bottom和Silkscreen-Top分别为Bottom层和Top层丝印,我习惯是在后期的丝印添加在此层

2.Design_Outline用于绘制PCB的外形(板框)

3.Soldermask_Bottom和Slodermask_Top用于设计在Bottom层和Top层添加阻焊窗,即添加不需要俗称绿油的区域。(可以手工添加阻焊层,有一定的自由度)

Package Geometry

1.ASSEMBLY-TOP和ASSEMBLY-BOTTOM是与装配相关的内容,表示的是零件的外形和方向。

2.PLACE-BOUND-TOP和PLACE-BOUND-BOTTOM表示的是零件在Top层和Bottom层各自占位大小,在同一层中如果两个零件的PLACE,BOUND区域有交叠将发生DRC错误。在3D显示时如果没有提交step文件,那么就会显示此地方的高度值。

3.PIN-NUMBER用于表示零件的引脚号的显示。

4.Soldermask_Bottom和Slodermask_Top用于设计在Bottom层和Top层添加阻焊窗,这个是在设计PCB焊盘封装时添加的,负片的,有图形的地方没有绿油。

5.Pastemask_Bottom和Pastemask_Top用于设计在Bottom层和Top层添加助焊窗,这个是在设计PCB焊盘封装时添加的,用于开钢网,这个是负片的,有图形的地方是需要开空的。

6.body_center,这个是封装的中心位置。

7.Silkscreen-Bottom和Silkscreen-Top分别为Bottom层和Top层丝印,对应封装。

Components(组件)

Refdes:元器件显示字符,对应到原理图对元器件定义的位号属性,里面包含了,装配的位号,和部件的位号。

二、绘制板框

使用**Design Outline(板框)和Cutout(挖槽)**定义电路板外形。

在Cadence Allegro高版本(如17.2及以上)中,Outline和Design Outline是两种不同的电路板外形定义方式,主要区别在于操作方式和版本兼容性。以下是核心差异和使用要点:

核心区别

- Outline(传统方式) :通过画线(lines)方式定义板框,适用于17.2之前版本。高版本中仍可使用,但会触发警告提示(如输出Gerber时),且可能导致3D视图缺失板框。

- Design Outline(新版本推荐) :通过添加shape(如闭合图形)定义板框,17.2及以上版本默认方式。操作路径:Board Geometry → Shape命令 → Create设计轮廓

三、快捷键使用

单击字母,不需要回车,即可启动快捷键。

现象:option会弹出,弹出对应快捷键功能的设置。

设置快捷键:找到安装目录下的env文件。(share/pcb/text/)

funckey A assign color

funckey B shape add

funckey m move //移动命令

funckey ' ' iangle 90 //空格90度旋转 需要先用move命令选中

funckey r iangle 45 //r 45度旋转 需要先用move命令选中

funckey w add connect //电气走线

funckey l add line //非电气属性线

funckey e shape add //铺铜,任意形状

funckey E shape select //shift+E 选中铜皮,一般用来修改网络和改变铜皮形状

funckey A delay tune //蛇形走线

funckey q show measure //测量

funckey 1 rats net //显示选中网络飞线

funckey 2 unrats net //隐藏选中网络飞线

funckey b mirror //将器件切换到底层

funckey d slide //修线

funckey s swap components //交换器件位置

funckey c Change //改变属性

funckey ~D delete islands //删除孤岛

funckey ~E shape edit boundary //Ctr+E 修剪铜皮

funckey ~Z undo //回到上一步 Ctr+Z

funckey ~Y redo //回到下一步

funckey ~C copy //复制

funckey ~S save //保存

funckey f fix //锁定

funckey ~F unfix //解锁

alias Esc done //取消

alias Del delete //删除

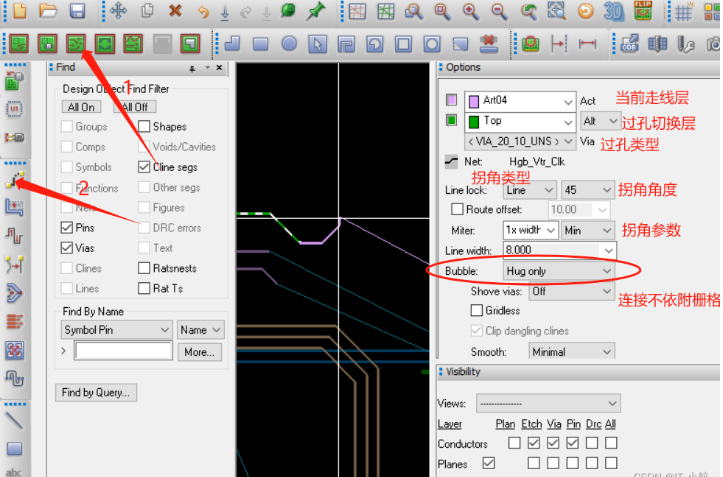

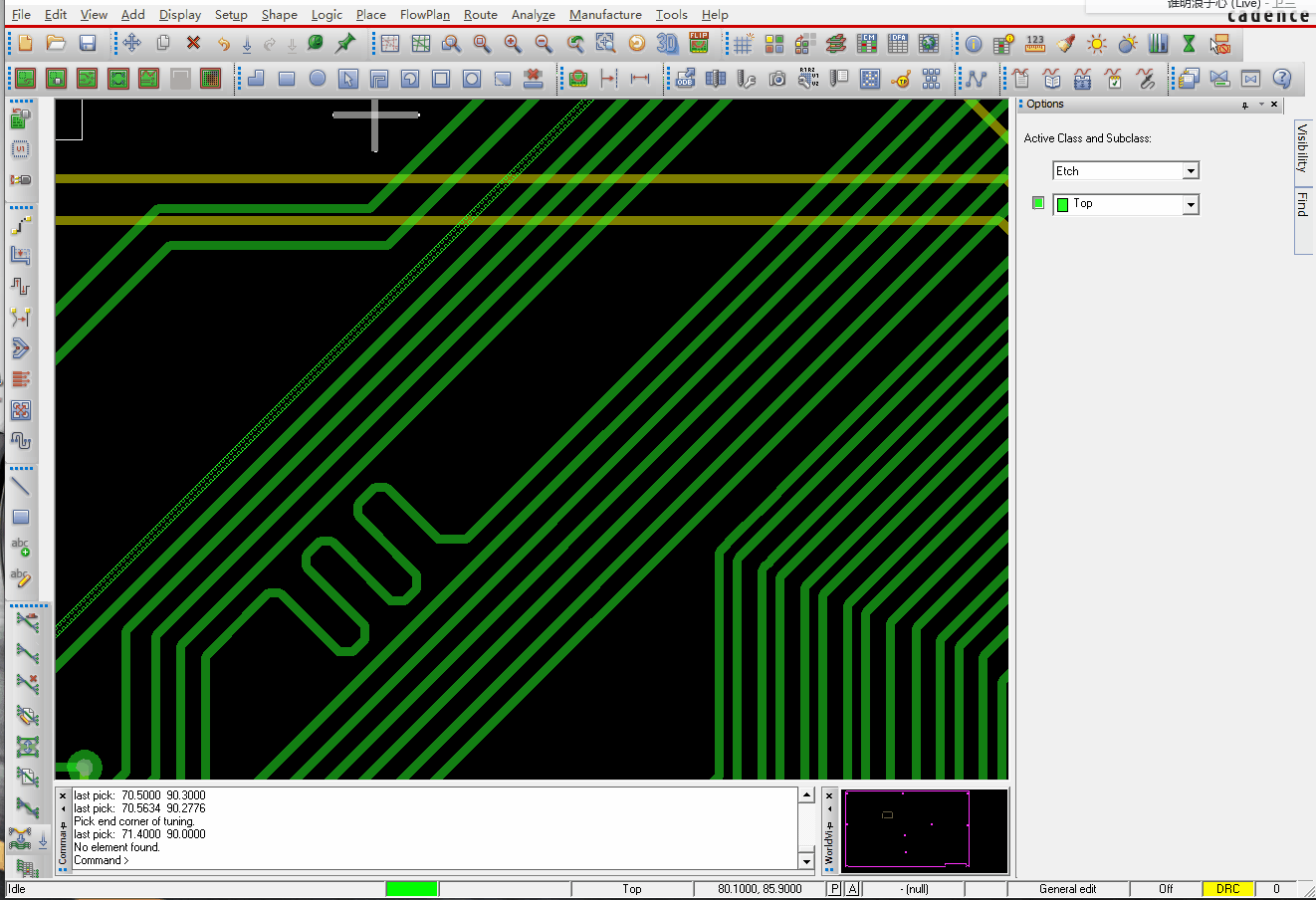

四、走线

切换到走线模式,点击走线,走线时双击左键可以放置过孔,在options中进行走线参数设置

Bubble: 障碍物冲突设置: (图中画框参数)

**off:**无视冲突

**Hug only:**环绕障碍物 (一般使用这个)

**Hug preferred:**环绕优先

**Shove preferred:**推挤优先

4.1 群组走线

选择走线,框选多个过孔,开始群组走线。

右键Route Spacing设置线之间 的间距。

右键Change Control Trace,点击线端点,改变变更控制线。

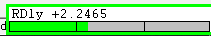

4.2 等长走线

先设置差分对,再设置差分对的长度误差。

再使用等长修正命令,走线旁边,像蛇形线的按钮。

走等长时,,右下角有等长延迟提示将延迟提示控制在绿色就是在误差范围之内

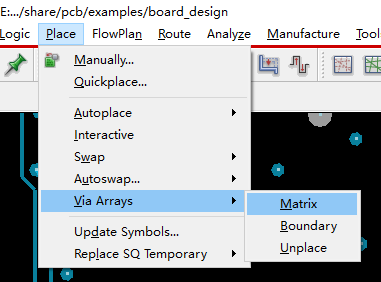

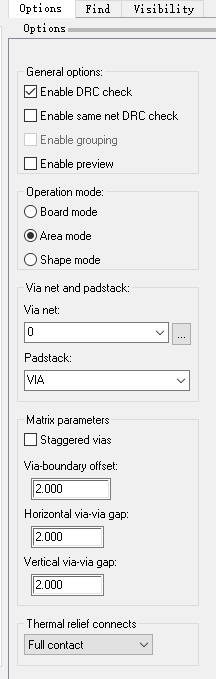

4.3 阵列过孔

这里以在铜皮上打阵列过孔为例,介绍一下阵列过孔的操作过程。