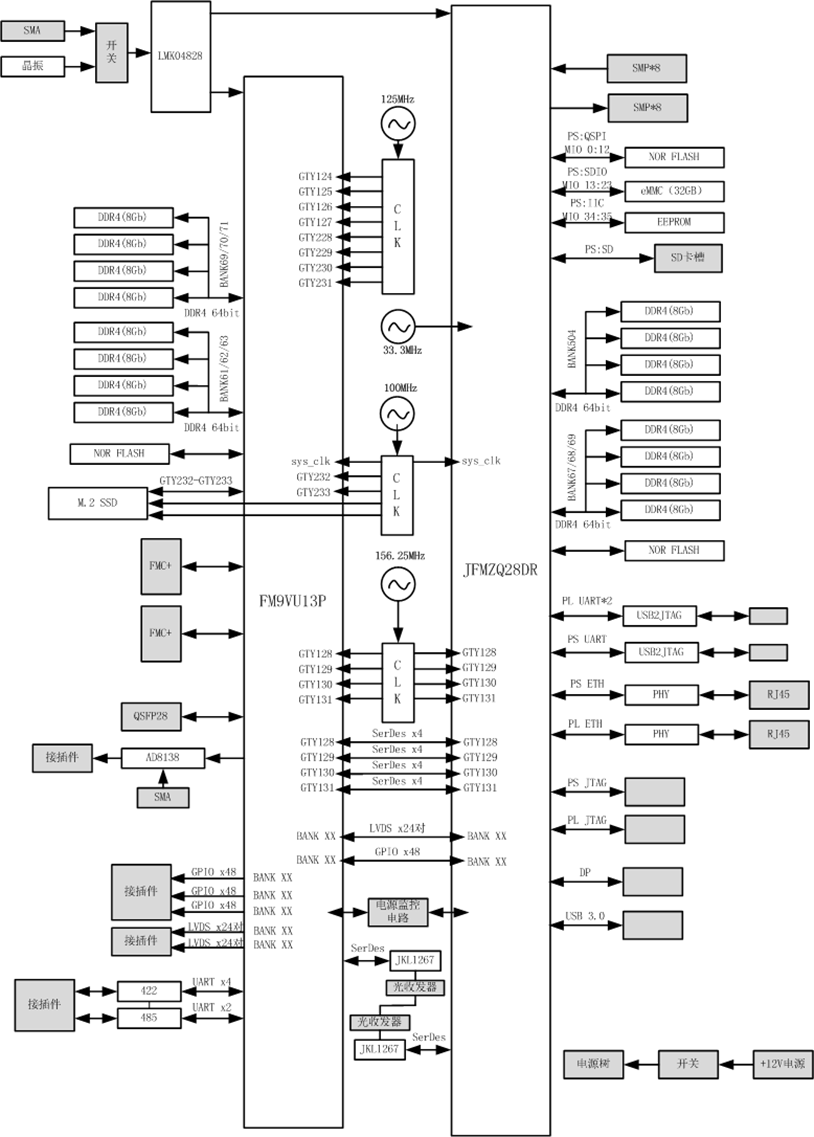

信号处理板原理框图如下图所示。28DR作为整板的主控中心、VU13P作为整板的基带信号处理中心。

技术指标

1片复旦微 RFSOC 芯片JFMZQ28DR(RFDC版本V03以上)+1片复旦微FPGA芯片FM9VU13PB2104作为主芯片,主芯片国产化,其他IC器件无国产化要求(原则上选择国产可替代器件);

FPGA-VU13P芯片外围配置

- FPGA-外接2组DDR4 SDRAM,每组容量4GB,速率2400MT/s;

- FPGA-外接SPI FLASH,容量不低于1Gb;

- FPGA-外接M.2 SSD;

- FPGA-外接两路光纤通信;

- FPGA-外接两组FMC+;

- FPGA-外接164245,实现48对LVDS和144个GPIO控制;

- FPGA-外接串口芯片,实现4个422和2个485串口控制;

- FPGA-外接差分ADC驱动器(如AD8138),用于输出

RFSOC-28DR芯片外围配置

- 对外引出8路ADC和8路DAC,ADC采样率最大支持5GSPS,量化位数14bit,DAC采样率最大支持6.554GSPS,量化位数14bit;

- 8路DAC输出工作频段为10M~6GHz,输出功率不小于-2dBm,DA幅度误差小于1dB;8路ADC输入工作频段为10M~6GHz;

- SFDR不小于50dB,全频带条件下同步精度不大于5°;

- PS外接 DDR4 SDRAM动态存储器,容量4GB,速率2400MT/s;

- PS外接 eMMC存储器,容量不低于32GB;

- PS外接 SD卡槽;

- PS外挂SPI FLASH,容量不低于512Mb;

- PS外接一路千兆网口、一路DP接口、一路USB3.0接口、一路422串口;

- PL外接SPI FLASH,容量不低于512Mb;

- PL外接 DDR4 SDRAM动态存储器,容量4GB,速率2400MT/s;

- PL外接两路422串口;

- 28DR需支持通过跳线帽方式择启动模式,启动模式需支持:QSPI Flash启动、SD卡启动、eMMC启动;

- 28DR与VU13P间连接4组GTY bank、24对LVDS,48个GPIO;

- VU13P需支持8组GTY,功能待定;

- 28DR和VU13P均外接一路GLINK接口;

- 28DR需支持对射频部分供电的开关控制,默认为关闭状态;

- 28DR需支持对VU13P的上电控制以及运行时的上电复位控制;

- 28DR需支持对VU13P运行时的重配置;

- 28DR需支持对时钟树配置,用户可根据需求配置预期时钟,时钟LMK04828;

- 28DR需支持对参考时钟源的选路配置,用户可根据需求选择板载高精度晶振作为时钟源还是外部参考输入时钟作为时钟源;

- 板上增加电源监控模块,监控核心电源;

软件程序:

|--------|------------------|------------------|----------------------------------------------------------|

| ||||

| 序号 | 驱动类型 | 驱动名称 | 功能描述 |

| 1. | PS 外设驱动 | 网口驱动 | LWIP,以裸机方式实现网口驱动,可与上位机ping通 |

| 1. | PS 外设驱动 | 串口驱动 | 1路串口,UART0可作为调试串口正常使用 |

| 1. | PS 外设驱动 | I2C驱动 | |

| 1. | PS 外设驱动 | QSPIFlash驱动 | |

| 1. | PS 外设驱动 | eMMC驱动 | eMMC需格式化成2个分区,第一个分区存放根文件系统,第二个分区存放用户数据;第二分区支持mount在文件系统下 |

| 1. | PS 外设驱动 | SD卡驱动 | 支持在Linux系统启动后挂载SD卡文件系统 |

| 1. | PS 外设驱动 | USB驱动 | 以裸机方式实现usb驱动与上位机libusb收发测试 |

| 1. | PS 外设驱动 | DP驱动 | 以裸机方式DP接口驱动 |

| 1. | PL外设驱动 | 时钟配置驱动 | 实现对时钟芯片输出时钟频率配置 |

| 1. | PL外设驱动 | DDR4读写驱动 | PL侧实现对DDR4读写 |

| 1. | PL外设驱动 | 在线升级驱动 | |

| 1. | PL外设驱动 | 串口驱动 | |

| 1. | PL外设驱动 | 网口驱动 | 实现TCP/IP协议 与上位机通信 |

| 1. | VU13P外设接口驱动 | DDR4读写驱动 | 实现对DDR4读写 |

| 1. | VU13P外设接口驱动 | 在线升级驱动 | |

| 1. | VU13P外设接口驱动 | QSFP+光口驱动 | 通过Ibert测试链路通路,可通过光模块回环测试 |

| 1. | VU13P外设接口驱动 | AD8138驱动 | |

| 1. | VU13P外设接口驱动 | M.2 SSD驱动 | |

| 1. | VU13P外设接口驱动 | I2C通信驱动 | |

| 1. | VU13P外设接口驱动 | FMC+ 驱动 | 约束文件 |

| 1. | VU13P与28DR互联接口驱动 | GT连通性测试 | 通过Ibert测试链路通路 |

| 1. | VU13P与28DR互联接口驱动 | AURORA x16通信驱动 | 实现VU13P与28DR之间基于AURORA64b66b的16 lane数据收发 |

| 1. | VU13P与28DR互联接口驱动 | SRIO x4通信驱动 | 实现VU13P与28DR之间基于SRIO x4数据收发 |

| 1. | VU13P与28DR互联接口驱动 | GPIO连通性测试 | 测试VU13P与28DR互联的GPIO连通性即可 |

| 1. | VU13P与28DR互联接口驱动 | LVDS连通性测试 | 测试VU13P与28DR互联的LVDS连通性即可 |

| 1. | 系统功能驱动 | 28DR AD/DA IP核工程 | 提供复旦微官方ADC/DAC IP核,该IP核在开发阶段支持相关参数配置。具备校准功能。 |

| 1. | 系统功能驱动 | 28DR射频通路测试 | 基于单音信号的进行收发射频回环测试 |